ELECTRONIC PACKAGING & SPACE PARTS NEWS EEE ...ecanderssen/Cable_Harness_Stds/v4-n3...those with...

Transcript of ELECTRONIC PACKAGING & SPACE PARTS NEWS EEE ...ecanderssen/Cable_Harness_Stds/v4-n3...those with...

EEE LinksELECTRONIC PACKAGING & SPACE PARTS NEWS

July 1998, Vol. 4 No. 3In this issue:

Ø Challenges ofImplementing CSPTechnology

Ø ProgrammableLogic ApplicationNotes

Ø COTS Effort at JPL& Launch of aCOTS Website

Ø Evaluation of ESDEffects DuringRemoval ofConformalCoatings UsingMicro AbrasiveBlasting

Ø The Rational Useof Plastic Parts inSatellites

Ø 1998 Military andAerospaceApplications ofProgrammableDevices andTechnologiesConference

Ø Low PowerEvaluation ofCOTS 4MegSRAMs for SpaceApplications

Next Generation M2MAntifuse FPGA

QYH530 Quick-Turn ASIC

A1020 DUTController

(RH1020 for SN 002)

DITS-2/STRV-COTS 2 S/N 001

CX2041 Quick-Turn ASIC

under the MCM

PICO SystemsSubstrate

with QYH530 &CX2041 Die

QUAD HexFETfor DUT Power

Switching

UT22VP10Amorphous Silicon

Antifuse PAL

80C32uP

SpacecraftInterface

Editor: Robert Humphrey, (301) [email protected]

Mailing List Information and Article Submissions: (301) 731-8625Desk Top Publisher: Esther Bailey

Published by the NASA/GSFC Electrical Systems CenterComponent Technologies and Radiation Effects Branch, Code 562

Branch Head: Robert LebairWWW URL Address:

http://misspiggy.gsfc.nasa.gov/ctre/hq/eee_links

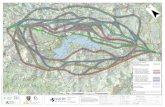

The above picture shows both sides of a STRV-1d/COTS-2 flight card. The cardincorporates a number of technologies, including quick-turn ASICs, prototype next-

generation FPGAs, radiation-hardened FPGAs and PALs, programmable sub-strates, plastic packaging, a fuzzy logic processor, compact HEXFETs, and a variety

of commercial memory devices. The card is heavily instrumented to measure theaffects of the space radiation environment on the components and data will be com-

pared with that obtained from the ground test program

EEE Links, Vol. 4 No. 3

ii

Letter from the Editor ........1

1998 Military and AerospaceApplications of ProgrammableDevices and TechnologiesConference............................... 1

Challenges of ImplementingCSP Technology...................... 2

COTS Effort at JPL & Launchof a COTS Website.................. 4

Low Power Evaluation of COTS4Meg SRAMs for SpaceApplications............................. 4

Evaluation of ESD EffectsDuring Removal of ConformalCoatings Using Micro AbrasiveBlasting ................................ ...4

The Rational Use of PlasticParts in Satellites..................... 4

Programmable LogicApplication Notes.................. 14

Jet Propulsion Laboratory PartsAnalyses................................ 23

Goddard Space Flight CenterParts Analyses....................... 25

GIDEP & NASA AdvisoryImpact Report ........................ 25

c

o

n

t

e

n

t

s

Articles Articles

EEE Links, Vol. 4 No. 3

1

Letter from the EditorRobert Humphrey

Editor of EEE Links(301) 731-8625

Welcome to the July issue of EEE Links. In the lastissue I mentioned that in an effort to improve acces-sibility to the electronic version of the EEE Links weswitched to a PDF format for the EEE Links Webpage. In addition we are also in the process of up-dating past issues to the PDF format.

Please note the new URL address for EEE Links ishttp://misspiggy.gsfc.nasa.gov/ctre/hq/eee_links.

As always, please keep us informed with your ques-tions and needs so we may be able to better providethe information you need and want.

________________________________

1998 Military and AerospaceApplications of

Programmable Devices andTechnologies Conference

Janet JewGoddard Space Flight Center

(301) 286-5533 or [email protected]

The conference will address devices, technologies,usage, reliability, fault tolerance, radiation suscepti-bility, and applications of programmable devicesand adaptive computing systems in military andaerospace systems. The technical program will con-sist of oral technical presentations as well asindustrial exhibits. The conference will be held at theNASA Goddard Space Flight Center in Greenbelt,Maryland.

Presentations will be in all aspects of the use of pro-grammable elements, devices, and applications formilitary and aerospace applications. These include:PALs, FPGAs, PROMs, Programmable Substrates,FPIC, Programmable Analog Circuits, adaptive com-putting systems and related technologies. Allpresentations are expected to be technical in nature.Each presentation will be twenty-five minutes. Con-ference proceedings will be published anddistributed to all attendees.

Topics include (but are not limited to) the following:• Programmable Technologies and State-of-the-Art

Devices− COTS and MIL/AERO− New Technology Development− Adaptive Computing Systems

• Radiation Effects, Device Reliability and ElementCharacteristics

• Device Architecture, Performance, and Capabili-ties

• Applications and Novel Techniques for Militaryand Spaceflight Circuits.− Signal Processing− High-Speed Designs− System Impact of State-of-the-Art Tech-

nologies− Reconfigurable Processing− Low Power Designs− Advanced Packaging

• Use of COTS Devices in the Military and Space-flight Environment− PEMS− Shielding, Latchup Protection− SEE including SEFI and Destructive Effects− System Protection− Testing and Analysis Techniques− Performance Results− Use of Programmables in Critical Systems− Software Tools for Design/Analysis

§ Synthesis§ Macro Generators§ Timing Analysis and Simulation§ Redundancy, Fault Tolerance, and

SEU-Hardening

PRELIMINARY CONFERENCE SCHEDULE

September 14NASA/GSFC Tours, and early registration at theGSFC Visitor Center, Soil Conservation Road.

September 15 and 16In addition to over twenty presentations, keynotespeakers are Dennis Andrucyk of the Goddard SpaceFlight Center who will address “Achieving the EarthScience Vision”; John Birkner, Vice President and Co-founder of Quicklogic Corporation, addressing“From Simple PALs to High-Speed, High DensityLeading Edge FPGAs, their Technologies and Appli-cations”; Janet Barth of the Goddard Space FlightCenter providing “An Overview of the RadiationEnvironment for Spaceflight Electronics”; and Jose

EEE Links, Vol. 4 No. 3

2

Munoz addressing “DARPA’s Adaptive ComputingSystems (ACS) Program.”

A Posterboard session will be held Tuesday eveningfor additional presentations.

The conference is sponsored by (preliminary list):NASA/GSFC, JHU/Applied Physics Laboratory, andthe NASA Radiation Effects Program.

For event schedules, a list of presentations, andmore information on the conference please seehttp://rk.gsfc.nasa.gov/richcontent/Ksymposium/kSymposium.htm

Please Send Abstract Submissions to:Martha O'[email protected]: (301) 286-1412Fax: (301) 286-0220

Conference Chair:Richard KatzNASA Goddard Space Flight [email protected]: (301) 286-9705

Conference Co-Chairs:Alan W. [email protected](301) 688-0292

Ann DarrinJohns Hopkins University/Applied [email protected](240) 228-4952

Richard B. KatzNASA Goddard Space Flight CenterMicroelectronics and Signal Processing BranchBldg. 11, Room S31 (lab and deliveries)Bldg. 11, Room E217 (office)Code 564Greenbelt, MD 20771301-286-9705Fax: 301-286-0220email: [email protected] page: http://rk.gsfc.nasa.gov

________________________________

Challenges of Implementing CSPTechnology

Dr. Reza Ghaffarian, Ph.D.Jet Propulsion Laboratory

California Institute of Technology(818) 354-2059

email: [email protected]

Availability of board solder joint reliability informa-tion is critical to the wider implementation of ChipScale Packages (CSPs). CSPs are defined as packagesthat are up to 1.2 or 1.5 times larger than the perime-ter or the area of the die. Many manufacturers nowrefer to CSP as the package that is a miniaturizedversion of the previous generation.

A consortium was formed from the team membersof the original JPL-led BGA consortium and newmembers added with experience in this technology.All participants have furnished in-kind contributionsby providing their expertise and resources requiredto complete the objectives of the program. Diverseparticipants, including those from military andcommercial sectors permitted implementation of theobjectives of the program in a concurrent engineeringenvironment.

In the process of building the first test vehicle ofCSPs, many challenges were identified regardingvarious aspects of technology implementation. Keychallenges are summarized as follows:

Maturity and availability — Availability of CSPs foruse and attachment reliability evaluation is the mostchallenging issue. There are numerous publicationson a wide range of CSPs, but most packages are attheir early stages of development and lack packagereliability data. Assembly reliability data are rare.Most packages were available in prototype form andthis does not guarantee the uniform package charac-teristics for the production version or even theiravailability. Delay on package delivery from theprojected time is the norm.

Lack of Design Guideline Standards— Currently,guidelines and standards on various elements ofCSPs are not available. For our design, guidelinesdeveloped by the package suppliers were used whenavailable. Otherwise, available knowledge and engi-neering judgment were considered. Packages chosen

EEE Links, Vol. 4 No. 3

3

had different pitches, solder ball volumes, solder ballcompositions, and daisy chain patterns. In mostcases, these patterns were irregular and much timeand effort was required for design. This was espe-cially cumbersome for packages with higher I/Osand many daisy chain mazes. Board design guide-lines are needed, especially for the build up(microvia) configuration.

PWB Materials — The standard PWB design couldbe used for low I/O CSPs. Our test vehicle includedseveral of these packages with the objective of char-acterizing assembly reliability when conventionalPWB design was used. Higher I/O packages withactive dies require the use of buildup (microvia)board technology. For testing purposes, however, itwas possible to design high I/O daisy chain pack-ages on a standard board. Another version of ourtest vehicle included a PWB with microvia technol-ogy.

Applications — There were a number of packagesfrom low I/O (<50) to higher I/Os selected for char-acterization. It became apparent that for the nearfuture, 1-3 years, the dominant packages would bethose with less than 50 I/Os. Specific applicationrequirements could utilize packages with muchhigher I/Os. Mixture of conventional SM packages,direct chip attachment, BGAs, and CSPs on oneboard is another expected design and assembly chal-lenge.

TEST VEHICLE DESIGN

The consortium agreed to concentrate on the follow-ing aspects of CSP technology after numerousworkshops, meetings, and weekly teleconferences.

Package — Numerous packages from leaded andleadless to micro type ball grid arrays were selectedfor evaluation. I/Os ranged from 40 to 300 to meetthe short and longer term applications.

PWB Materials and Build — Both FR-4 and BT (Bis-maleimide Triazine) materials were available in theresin copper coated form for evaluation. Both stan-dard and microvia board technologies were used. Indesign of daisy chains, it became apparent that thestandard PWB technology could not be used for themajority of packages.

Surface finish — At least three types of surface fin-ishes are being considered for evaluation: OSP,HASL, and Au/Ni. Other surface finishes are alsobeing considered. Three types of solder pastes willbe evaluated: no clean, water soluble and RMA.

Underfill — Packages with underfill requirementswill be evaluated both with and without underfill tobetter understand the reliability consequence of notusing underfill.

Test vehicle feature — The test vehicle is 4.5 by 4.5inches and divided into four independent regions.Each region has four daisy chains and can be cut forfailure analysis without affecting the daisy chains ofother regions. All packages are daisy chained andhave up to two internal chain patterns.

Environmental testing — At least three conditionswill be considered; -30 to 100°C and -55 to 125°C, tolink our data to those generated for the Ball Grid Ar-rays. Also, thermal cycling will be performedbetween 0 and 100°C to meet the needs of commer-cial team members. In addition, mechanicalvibration and shock will be performed and theoreti-cal modeling will be carried out as needed.

STATUS OF THE MICROTYPEBGA PR OGRAM

The consortium has completed the design of two testvehicles: one from collective team effort (TV-1) andthe other initiated internally by a team member (TV-H). The trial assembly of the TV-H is now complete.These assemblies were evaluated and the requiredchanges were implemented for full production as-sembly. The only remaining challenge is the processoptimization for a flip chip package. Flip chips withand without bridges were built. One possible reasonfor bridging was the lack of solder mask between thepads. The solder mask was not feasible to apply be-cause of the fine pitch pattern.

The TV-1 trial boards were built to optimize the as-sembly processes and to verify continuity of daisychains. The consortium is currently assembling thefull production test vehicles. We will assemblenearly 300 test vehicles with CSP I/Os from 40 to300.

EEE Links, Vol. 4 No. 3

4

ACKNOWLEDGMENTS

The research described in this publication is beingcarried out by the Jet Propulsion Laboratory, Califor-nia Institute of Technology, under a contract with theNational Aeronautics and Space Administration.

I would like to Acknowledge in-kind contributionand cooperative efforts of MicrotypeBGA consortiumteam members and those who have been contribut-ing to the progress of the program.

________________________________

COTS Effort at JPL & Launch of aCOTS Website

Mike SandorJet Propulsion Laboratories

[email protected] Agarwal

Jet Propulsion [email protected]

Phone: 818-354-5598FAX: 818-393-4559

As JPL moves toward the new millenium, new com-mercial technologies and microelectronics will beused more and more to help meet mission constraintsand requirements and in consort with a faster, better,cheaper environment within NASA. Commercial mi-croelectronics (parts) offer some advantages such asreduced weight with plastic packaging, more per-formance with advanced processes and designs, andan assortment of integrated functions only availableas commercial off-the-shelf (COTS) parts.

Using COTS in space successfully requires completeunderstanding of the product's capabilities and limi-tations under a space environment. Since COTS bydefinition are not designed to operate in Space, theremay be serious or compromising factors that couldjeopardize mission success if not understood. Al-though, there are some situations where COTS can beused satisfactorily provided all potential risks areknown or can be mitigated.

Office 507 has undertaken an initiative to evaluateand explore the issues regarding the use of COTSparts in Space. In addition, Office 507 can help JPLprojects in ascertaining the suitability of COTS intheir applications. This is accomplished by utilizingcharacterization, reliability evaluation, and risk as-

sessment. The use of COTS in Space applications isincreasing and making a prominent presence, in-cluding in the military and aerospace industries. Tostay abreast with the developments in COTS parts,Office 507 has developed a web site to disseminateinformation on COTS that will help users in evalu-ating, ascertaining risk, or selecting parts for theirapplications.

The web site has technical reports, presentations,data, and news related to COTS work completed bythe electronic parts engineering group and others.

This new web site called "COTS Microelectronics inSpace" can be found at: http://cots.jpl.nasa.gov/.

As always, comments are welcome. Check on the"access" button on the home page for information.

________________________________

Low Power Evaluation of COTS4Meg SRAMs for Space

ApplicationsMike Sandor

Jet Propulsion [email protected]

Shri AgarwalJet Propulsion [email protected]

Phone: 818-354-5598FAX: 818-393-4559

An evaluation was performed under the auspices ofJPL Office 507 LPSEP (Low Power Space ElectronicParts) task whose objective is to identify flight wor-thy 3.3V state-of-art devices. 5V commercial 4-megabit static random access memories (4MegSRAMs) from Sony, Hitachi and Motorola whichwere characterized for operation at 3.3V. This workwas done in collaboration with Space Electronics, Inc.(SEI). Based on the test results and the fact that theyalready sell a 5V radiation tolerant 4Meg SRAM withHitachi die, SEI has offered to make a 3.3V Hitachiversion for the space community.

For a copy of the report, go to JPL COTS website(http://cots.jpl.nasa.gov)and look under reports.

________________________________

EEE Links, Vol. 4 No. 3

5

Evaluation of ESD Effects DuringRemoval of Conformal CoatingsUsing Micro Abrasive Blasting

Nitin ParekhComponent Technologies Branch (Code 562)

Unisys/NASA(301) 731-8677

[email protected] Frades

NASA Training CenterHEI/NASA

(301) [email protected]

The following is an abstract of a paper published andpresented at the IPC Printed Circuits Expo'98 held inLong Beach, California on April 26-30, 1998.

ABSTRACT

Recent environmental regulations such as MontrealProtocol and Clean Air Act have had a significantimpact on Coating Technology including equipment,materials, application and removal processes, par-ticularly with regard to control of volatile organiccompounds (VOCs) and ozone depleting chemicals(ODCs). Manufacturers and suppliers of conformalcoatings materials have been developing non-solventbased coatings and environmentally acceptablemethods of application, curing and removal proc-esses.

The most commonly used methods for removal ofpolymeric coatings from printed wiring assemblies(PWAs) involve thermal, chemical, mechanical, microabrasive, plasma and laser based systems and proc-esses. The need for rework or repair of a conformalcoating can arise at any time after completion of anassembly due to a variety of process/product re-quirements or component replacement issues.

NASA's objective is to determine the effectiveness ofmicro abrasive blasting techniques to remove con-formal coatings from printed circuit boards (PCBs)and assemblies. Micro abrasive systems generatestatic electricity as the high velocity particles impingeon the PWB surface. The ESD voltage generated atthe point of contact can cause damage to componentsand electrical circuits on a PWA.

This paper presents the preliminary results of NASAstudy on the level of ESD damage at the point of

contact and any visible physical damage as a result ofmicro blasting during removal of urethane and par-ylene conformal coatings. The final study is expectedto be completed by FY 1999.

________________________________

The Rational Use of Plastic Partsin Satellites

Anthony Casasnovas & Andrew F. MoorThe Johns Hopkins University Applied Physics Laboratory

Laurel, Maryland

Copyright 1998 IEEE. Reprinted, with permission,from the Proceedings of the IEEE 1998 InternationalFrequency Control Symposium, May 27-29, 1998 RitzCarlton Hotel, Pasadena, CA.

Key Words -- Commercial Off The Shelf (COTS),Handling, Plastic Encapsulated Microcircuit (PEM),Qualification, Screening

Summary & Conclusions --Management of plasticencapsulated microcircuits begins and ends with aconcurrent engineering effort. The effort begins withthe establishment of partnerships with a handful ofworld-class suppliers and ends with the develop-ment, documentation, and enforcement of rigorousin-house controls regarding device handling,screening, qualification, uprating, derating and stor-age.

The Johns Hopkins University Applied Physics Labo-ratory (JHU/APL) has successfully selected screenedand qualified PEMs for multiple artificial satelliteapplications. We discuss the rationale on how thesecommercial devices can be properly qualified andapplied.

1. INTRODUCTION

Trends in the marketplace for smaller, more cost ef-fective, state-of-the-art technologies are rapidlyforcing obsolescence and leading to decreased avail-ability of military-grade hermetically sealedelectronic components. PEMs, once a non-alternativefor space flight applications, have become a neces-sity. Predominant factors to consider such as vendorselection, environmental considerations, procure-ment, handling, screening and qualification strategieswith associated systems implications are presented.The Thermosphere- Ionosphere - Mesosphere - Ener-

EEE Links, Vol. 4 No. 3

6

getics and Dynamics Program (TIMED) is used todescribe the JHU/APL approach.

TIMED Program

The TIMED Program is the first mission in the Na-tional Aeronautics and Space Administration’s(NASA) Solar Connections Program. TIMED willexplore the Earth’s mesosphere and lower thermo-sphere in the 60km - 180km range. TIMED has a 3year development cycle, followed by a 2 year missionlife; launch is expected in January 2000. Key techni-cal accomplishments for TIMED include: 2GB solid-state recorder, radiation-hardened 32-bit RISC proc-essor, redundant MIL-STD-1553 data bus, and theintegrated command, telemetry, radio-frequencycommunications, global positioning system and datastorage module.

To accomplish the TIMED mission objectives, it wasnecessary to successfully balance the risks associatedwith using commercial technology against the needfor space-level component reliability. For example,high-density commercial memory devices were theenabling technology that allowed the development ofthe TIMED 2GB solid-state recorder. While suitablePEMs were found for TIMED, it may not be possibleto find PEMs that are useable for every high-reliability application. It is expected that this willchange over time as the risks associated with PEMusage are fully understood.

Looking more specifically at TIMED, Table 1 pro-vides a breakdown of the electrical, electronic, andelectromechanical (EEE) parts that comprise theTIMED spacecraft. The numbers are representativeof unique line items, whereas, multiple occurrencesof a device is not shown. Definitions for the columnheadings are as follows:

Military: All military specifications, /883, QML,DESC-SMD and NASA specifications

SCD: JHU/APL source control drawings (SCD),purchase order line-item requirements, manufac-turer’s internal hi-rel flow

PEM: A PEM is a COT which has a plastic package.A PEM can be a microcircuit, semiconductor, passivecomponent, or otherwise.

COTS: Any commercially developed component.

Table 1. TIMED Parts Breakdown.COTS represent 16% of the total line items used

on the TIMED Program.

2. PEM SELECTION CRITERIA

JHU/APL utilizes a four-tiered approach to part se-lection: Concurrent engineering; evaluation of eachpart for its intended application; partnership withworld-class suppliers; and review of manufacturer’sreliability data.

An effective parts management program begins witha concurrent engineering effort. Key team playersfrom the following disciplines are required: Design,Manufacturing, Component Reliability, Logistics andPurchasing. It is the responsibility of the team toevaluate each part selected for its intended applica-tion. It is important to realize that a PEM which issuitable and qualified for a particular application ona spacecraft, may be completely unusable in anotherapplication on the same spacecraft! This simple con-cept is often overlooked by the traditionalist who isaccustomed to approving a part solely on the basis ofits military designation and not its intended applica-tion.

To help simplify the selection process, efforts aremade to form partnerships with only a select handfulof world-class suppliers. The rationale behind lim-iting vendor selection is founded in a variety ofreasons. First, limiting the number of vendors ulti-mately reduces the number of parts that have to beevaluated by the engineering team. Secondly, it fa-cilitates the working relationship between JHU/APLand the manufacturer. Having good and reliable

Military SCD PEM COTSCapacitor 124 1 3Connector 38 31 47

Diode 27 1 3Int-Ckt 134 11 8 4

Magnetics 8 11Oscillator 4 4 4

Relay 2 6Resistor 321 21 7 24

RF-Devices 4 19 24Transistor 12 4 1 3

Miscellaneous 34 21 15Totals 708 119 16 138

EEE Links, Vol. 4 No. 3

7

contacts is crucial to overcoming the service aspectsof being identified as a small volume customer. Thisties into the third reason, JHU/APL needs access tomanufacturers’ reliability reports and technical staff.The TIMED program has very specific guidelinesregarding vendor selection and PEM reliability thatneed to be met. As such, the adequacy of a givenmanufacturer’s reliability report ultimately becomesthe basis for acceptance, as well as the foundation forthe screening and qualification regime employed byJHU/APL.

3. PEM HANDLING ISSUES

As with PEM selection, JHU/APL employs a four-tiered approach to handling: Use of finger cotsand/or gloves; moisture protection; conformal coat-ing; and adherence to ElectroStatic Discharge (ESD)sensitivity practices and procedures.

The rationale for taking such precautions is corrosionavoidance. For galvanic corrosion to occur in PEMs,the following elements are necessary: a bimetalliccouple, most often gold-aluminum, present in thegold bond wire to the aluminum metallization pad;free mobile ionic contamination, usually chlorine, potas-sium, bromine, and/or sodium; and moisture,diffused from the atmosphere, to form an electrolyte[1].

We can identify two sources of ionic contamination:Traditionally, the encapsulant material was the mainsource of ionic contamination internal to the PEM.However, the present generations of molding com-

pounds are considered ion-free since the typical ionicresidue level in today’s parts is less than 10 part permillion (ppm) [2]. The second potential source is in-cidental contamination, external to the PEM. Thiscontamination can be from sources such as the at-mosphere, human handling, and cleaning agents.

The ionic transport of incidental ionic contaminationto the die surface is still the subject of intense debate.The addition of up to 80% silicon fillers to producethe epoxy novolac encapsulant used today in mostPEMs allows for limited ionic mobility. The encap-sulant material manufacturers reacted to this limitedionic mobility by adding an ion-getter, or scavenger.The incorporation of alkali- and halide-ion getteringagents into the epoxy-molding compound makes mi-grating ions in the epoxy unavailable for dissolutioninto any diffused or accumulated water in the pack-age [3]. The diffusion of ionic contaminants throughepoxy-novolac encapsulant is presented in the nextsection.

The Case for Finger Cots and GlovesThe case for finger cots and/or gloves is a strong one.Figure 1 depicts data from a recent University ofMaryland CALCE Electronic Packaging ResourceSource Center study. The study has demonstratedthat the rate of ionic diffusion through the encapsu-lant is a function of the ionic concentration, the epoxynovolac formulation, and the additives in the epoxy-novolac [4]. This study was conducted by separatingtwo cavities with a slice of epoxy novolac; CALCEpersonnel filled one cavity with distilled water and

Figure 1. Effect of Concentration on Ion Diffusion. No diffusion occurs for several days

EEE Links, Vol. 4 No. 3

8

the other with a solution of ionic contaminants. Theyevaluated various combinations of ionic species, con-centrations, temperatures, and epoxy formulations.The diffusion rate of ionic species throughout theepoxy was measured by sampling the distilled waterand analyzing it.

Two points can be gleaned from the graph presented.First, since the diffusion rate is directly related to ionconcentration, it becomes necessary to limit the in-troduction of any external contaminants, thusjustifying the use of finger cots and/or gloves. Sec-ondly, the use of ion-getters impedes the diffusion ofions. Unfortunately, it can be seen that these ion-getters are a limited resource. From Figure 1, afterapproximately 18 days the ion getters were com-pletely exhausted and the solutions reachedequilibrium.

What is truly frightening is that the University ofMaryland study was based on epoxy novolac slices ofapproximately 30 mils. How much time does a de-vice have, such as Figure 2, where onlyapproximately 6 mils of separation exist between thePEM surface and the bond wires? Hours may pass,not days, before ionic contamination could travelalong the bond wire to the surface of the die undersimilar conditions. The authors anticipate a muchslower ionic diffusion rate for PEMs under normalusage because the moisture available will be limitedand far less than 100% saturated as in the CALCEstudy.

The Need for Moisture ProtectionMoisture protection techniques are required for twodistinct reasons: First, to alleviate any potential“popcorning” of PEMs during the fabrication proc-ess, and secondly, in general, to combat corrosion.JHU/APL’s approach to controlling moisture in-volves timely bake-out of components,environmentally controlled storage areas, and the useof dry boxes.

In terms of popcorning prevention, devices undergoa bake-out for 24 hours at +125°C at the conclusion ofall incoming inspections. However, some parts maynot be baked at +125°C due to solderability and leadfinish concerns. Alternative methods, such as vac-uum bakes at lower temperatures may be used.Then, all parts are individually vacuum sealed indry-nitrogen purged bags prior to placement in flightstores. Once the dry-bag is opened, the part has alimited time duration to be soldered before it must bebaked-out again. The actual time allotted (out-of-bag-time) varies for each part and is a function of themoisture sensitivity level ascribed to it in accordancewith Interconnections Packaging Circuitry StandardIPC-SM-786A.

In regards to combating corrosion, we have alreadyexplained how finger cots and/or gloves can be ef-fective in reducing external contaminants. However,since it is not possible to eliminate all sources of ioniccontaminants additional prevention techniques mustbe employed. The focus of these techniques is cen-tered upon moisture avoidance.

From discussion above, moisture serves as the trans-port vehicle which allows ionic contamination toreach surface of the die. The simplest methods usedto minimize the moisture ingress have already beendiscussed under popcorn prevention: use of dry-nitrogen purged bags and bake-out of PEMs. How-ever, it is not sufficient to rely solely on a dry-bag forprotection. Cleanliness and moisture avoidance areconjoined. A JHU/APL study has demonstrated thatdry-bags serve only as barriers to moisture, not air[5]. Data from the study shows noticeable air-exchange occurring within a one week period andcomplete air exchange occurring within a month’stime. To assure cleanliness, it is necessary to main-tain parts in environmentally controlled storage areasor dry-boxes until needed. The dry-boxes can be

Figure 2. Samsung 32MB Flash Static Random Ac-cess Memory (SRAM). Note the close proximity of

the bond-wire loop to the top surface of PEM.

EEE Links, Vol. 4 No. 3

9

used, as long as it is practical, during piece-part test-ing, during board fabrication, and prior to and afterconformal coating [6]. In fact, entire printed circuitboard assemblies can be placed in the dry-box.

The Need for Conformal CoatingJHU/APL has performed numerous studies, re-viewed industry data, and continues to conductstudies in the area of long term dormant storage. Theresults of these studies evidence to the fact that de-lamination may be present in the “as-received”condition of devices directly from the manufacturer.

While it is true that differing opinions exist regardingthe validity and concerns placed on delamination,until definitive answers can be ascertained JHU/APLwill continue to take a very conservative approach.When a PEM exhibits large delaminations we assumethat these are a path for moisture and contaminantsto reach the surface of the die by traversing along thelead frame and bond wires. Therefore, we need con-formal coating to seal this path. Conformal coating isknown for increasing the reliability of assembliescontaining PEMs [7]. Since conformal coating willnot prevent moisture diffusion entirely (only slow itdown), we speculate that it will preserve ion gettersby filtering out some ionic species. The specific con-formal coating recommended by JHU/APL isParylene. The choice of Parylene is based on a studyconducted for the JHU/APL managed Full SignalTranslator (FST) program, as well as other industrydata [7]. The FST study involved subjecting threegroups of parts simultaneously to Steady State Tem-perature Humidity Bias Life Testing (85/85). Thethree categories of parts were: uncoated PEMs; PEMswith Urelane conformal coating; and PEMs with Par-ylene conformal coating. After 500-hour 85/85, onlythe Parylene coated parts were functional.

In addition, a recent chip-on-board (COB) study, alsoconducted by JHU/APL, has validated the recom-mendation for Parylene. The COB studydemonstrated that a Parylene/epoxy combinationwas effective in protecting unpassivated Sandia Na-tional Laboratory “Triple-Track” die during 1,000-hour 85/85 [8].

As with any good thing, there are always somedrawbacks. Several associated usage issues need tobe addressed regarding Parylene. First, Parylene re-

quires a vacuum deposition process. As such, accessto appropriate equipment is required. In addition,the effects of the vacuum deposition process on non-hermetically sealed or vented components is not fullyunderstood. It therefore becomes necessary to mask-off certain devices and interconnect pads of theboard. Secondly, rework becomes difficult once adevice is coated with Parylene. Either mechanicalstripping or localized heating can be used to removea device. Both of these approaches can lead to cos-metic scarring of the printed wiring board (PWB)assembly. In efforts to minimize PWB damage,NASA Goddard Space Flight Center is currently in-vestigating an alternate method that involves a “fine-nozzle” sand-blaster with ionizers to offset ESD con-cerns.

ESD Practices and ProceduresThe final topic to be discussed under PEM handlinghas to do with ESD awareness. ESD is an issue inde-pendent of PEM usage. It is prudent practice tohandle all components in such a manner as to avoidESD damage. JHU/APL has an established ESDprogram that conforms to MIL-STD-1686, “Electro-static Discharge Control Program for Protection ofElectrical and Electronic Parts, Assemblies, andEquipment.” In addition, local ionizers are recom-mended to further dissipate electrostatic charges.

4. PEM SCREENING

For the TIMED program, individual piece part test-ing involves electrical verification (at the missiontemperature profile), radiographic inspection, andvisual & mechanical inspection. With the exceptionof mechanical inspection, all screening tests are per-formed on a 100% basis.

Electrical VerificationMost PEMs do not meet standard military tempera-ture range (i.e., -55°C to +125°C). This should not beviewed as an immediate cause for concern, but a riskto be mitigated. The process which is used to reducethe risk involved in using components and/or sys-tems outside the manufacturer’s temperaturespecifications has been termed by the University ofMaryland CALCE, as uprating [9].

What is most important is for the PEM in question tomeet the appropriate mission temperature profile.In most instances the most severe temperature

EEE Links, Vol. 4 No. 3

10

extremes occur during ground based testing, notduring actual flight. For TIMED, the most severeenvironment occurs during spacecraft thermal vac-uum testing, -40°C to +100°C; actual componenttemperatures during flight are not expected to exceed+5°C to +50°C.

It is not JHU/APL’s intention to automatically use apart outside its intended manufacturer’s temperaturerating in a flight application. In fact, JHU/APL der-ates components to minimize the occurrence of thispossibility. Derating is defined as a process in whichdevice voltage, current and power are reduced by acertain percentage to extend longevity. However, ifno alternative part can serve, it becomes necessary toassure that part can function at the temperature pro-file required.

The choice to uprate comes with various legal conse-quences. Manufacturers have advocated that using apart outside its intended temperature range willautomatically invalidate any implied warranty.There may be even more serious legal repercussions,including the possibility of defamation lawsuits.

To assure a part will function reliably in the intendedflight application JHU/APL performs 100% electricalverification at the mission temperature profile ex-tremes. Since little power is dissipated duringelectrical tests, the device integrity is not compro-mised. In addition, sample parts are subjected to aselected set of qualification tests. Determination ofspecific tests to perform is based upon detailedanalysis of the manufacturer’s reliability data. Thepurpose of qualification testing is to complimentwhat has already been accomplished by the manu-facturer. Ramifications associated with qualificationtesting will be discussed in more detail under Sec-tion 5.

Radiographic ExaminationRadiographic examination (X-ray) is performed, on a100% basis, in accordance with MIL-STD-883,Method 2012, “Radiography.” JHU/APL recom-mends and uses real-time X-ray to obtain beneficialresults. Unlike film, real-time X-ray provides highresolution images in various planes by rotating thedevices inside the chamber. This enables the PEMsuser to develop a three-dimensional abstraction ofthe device internal construction. Figure 3 provides

an excellent view of the results obtained using thereal-time technique. The photograph is representa-tive of a Samsung 64MB Dynamic Random AccessMemory (DRAM). This DRAM is the integral part ofthe TIMED solid-state recorders. Figure 2 also em-phasizes the superior capabilities of real-time X-ray.

Figure 3. Real-Time X-ray of Samsung 64MBDRAM. From “Top View,” the die occupies a p-

proximately 90 percent of the package, with the leadframe on the top.

Performance of X-ray should not be viewed in thecontext of pass/fail criteria attributed to lot rejection.Rather, the purpose of performing the examination isto gain knowledge regarding overall device con-struction. Information learned serves as aninvaluable aid toward device decapsulation; a proc-ess necessary to accomplish Single Event Upset (SEU)testing and/or failure analysis. Additional informa-tion regarding SEU testing can be found in Section 5.

Visual & Mechanical InspectionVisual inspection is performed, on a 100% basis, inaccordance to the nearest applicable standard (i.e.,military, JEDEC, best commercial practices, etc.).Mechanical inspection is performed, on a sample ba-sis, in accordance to the same. The intent of theseinspections is to ensure device compliance to pur-chase order requirements.

5. PEM QUALIFICATION

JHU/APL approach to PEM qualification is centeredaround a five-tiered testing regime: radiation hard-ness assurance, temperature cycling, steady-statetemperature humidity bias life test, destructivephysical analysis, and high temperature operatinglife. For reasons that will be outlined below, all test-ing performed is considered to be destructive innature. The selected regime is designed to qualifyPEMs for all its mission environments, including

Side View

approx. 3.5X Mag.

approx. 3.5X Mag.

package top

EEE Links, Vol. 4 No. 3

11

integration, test, storage, transportation, launch, andmission life.

Radiation Hardness Assurance (RHA)All parts, commercial and/or military must be evalu-ated for RHA. When required, testing is performedin accordance with MIL-STD-883, Method 5005,“Qualification and Quality Conformance Proce-dures,” Group E, or equivalent.

It has been the experience of JHU/APL that totaldose is not the main cause for concern for RHA. Themajority of parts chosen either meet the low totaldose requirements associated with the TIMED mis-sion, or can be adequately shielded against sucheffects. The primary issue associated with RHA, forany part, is SEU immunity. For PEMs, SEU testingcan be cause for concern. Specifically, in question, isthe ability to decapsulate the PEM in order to per-form the SEU test. PEM decapsulation will becovered in more detail under Destructive PhysicalAnalysis, below.

One final thought in regards to RHA, it is necessaryto compensate for the affects of burn-in. Data pre-sented by Shaneyfelt, Winokur, Fleetwood, Hash,Schwank & Sexton, has demonstrated that burn-inmay affect radiation results [10]. As a result, partsused for RHA testing must resemble those in theflight configuration. If 100% burn-in was performedas a screen, it becomes necessary to ensure parts cho-sen for RHA are burned-in equally.

Temperature Cycling (T/C)The purpose of performing T/C is to cull potentialcoefficient of thermal expansion (CTE) mismatch con-cerns. T/C testing can induce or exacerbatedelamination, aiding corrosion by creating pathwaysfor moisture ingress. Mitigating against the effects ofdelamination justifies the need to conformally coatPWBs, as outlined above in Section 4.

When T/C testing is performed, JHU/APL followsthe guidelines established in Joint Electron DeviceEngineering Council (JEDEC) Standard JESD-22-A104, “Temperature Cycling.” After the completionof T/C testing, final electrical measurements at themission temperature extremes (e.g., cold, room, &hot) is performed. Finally, selected T/C samples aresubjected to DPA.

As an alternative to preconditioning, all parts used forT/C testing are assembled onto flight-like boards(e.g., same materials & manufacturer as flight boards)and conformally coated prior to conducting the T/Ctest. Preconditioning, as defined by JEDEC StandardA113-A, “Preconditioning of Plastic Surface MountDevices Prior to Reliability Testing,” aids in theevaluation of long term part reliability by taking intoaccount the impact of multiple solder reflow opera-tions. JHU/APL’s approach of assembling PEMsonto flight-like boards and conformally coating themprior to test qualifies the intended flight application.

T/C testing is performed as a result of reviewing themanufacturer’s reliability data.

Steady-State Temperature Humidity Bias Life Test(85/85)The purpose behind performing 85/85 testing is toassure that parts can survive in the uncontrolledmoisture laden environment prior to launch. Specifi-cally, variances in moisture and temperature duringintegration, test, transportation and storage of thespacecraft.

Once in the vacuum of space, moisture becomes anon-issue; moisture is immediately depleted uponentering the vacuum environment. Protecting thedevices while still on the ground requires the main-tenance of a “moisture-free” environment. Asalready stated, JHU/APL uses both dry-boxes andconformal coating to minimize moisture. Dry-boxes,by their very nature, are moisture free. Conformalcoating will not stop water, but it will slow it downand filter it.

When 85/85 testing is performed, JHU/APL followsthe guidelines established in JEDEC Standard JESD-22-A101, “Steady-State Temperature Humidity BiasLife Test.” Testing is done in a manner consistentwith that of T/C testing. The parts are assembledonto flight-like boards and conformally coated priorto conducting the test. After completion of testing,three temperature final electrical measurements aretaken and selected samples are subjected to DPA.

85/85 testing is performed as a result of reviewingthe manufacturer’s reliability data.

EEE Links, Vol. 4 No. 3

12

Destructive Physical Analysis (DPA)As with radiographic inspection, above (Section 4),the purpose of conducting DPA is to build a knowl-edge base of component construction technology.Special attention is given to the effects of T/C and85/85 testing on PEM reliability. It is hoped that ob-servations and measurements made during DPA willaid in the establishment of uniform pass/fail criteriaassociated with scanning acoustic microscopy results(delaminations).

When DPA is performed, JHU/APL follows theguidelines established in MIL-STD-1580, “Destruc-tive Physical Analysis for Electronic,Electromagnetic, and Electromechanical Parts,” asapplicable.

To further understand delamination phenomena, allsamples are subjected to C-mode scanning acousticmicroscopy (C-SAM) prior to decapsulation. Thistopic will be discussed in more detail under Section 6(reference U.S. Army Missile Command Study).

Currently JHU/APL utilizes three decapsulationmethods: oxygen plasma etching; wet etching witheither red fuming nitric and/or red fuming sulfuric acid;and thermo-mechanical means including grinding,heating, and breaking of the plastic encapsulation byforce. Each method has associated advantages anddrawbacks. Final selection of a particular method isdependant upon the end-results desired (e.g., func-tionality, access to internal structures, etc.).

High Temperature Operating Life (HTOL)Burn-in is only performed as part of qualificationtesting on a sample size basis. The first and fore mostreason for performing burn-in during qualificationhas to do with time. Applying the Arrhenius equa-tion, with an assumed activation energy of 0.7 V, astandard burn-in of 168 hours, at +125°C, extrapo-lated to +70°C, would require 3,272 hours tocomplete! Another reason for performing burn-in asa qualification test has to do with temperature. Asalready stated, the majority of PEMs are not rated to+125°C.

From Section 4, it has been established that duringTIMED spacecraft thermal vacuum testing somePEMs will exceed their data sheet temperature limits.As such, survivability of devices at these tempera-

tures must be assured. The purpose of performingHTOL, therefore, is to provide justification for uprat-ing of components.

When HTOL is performed, JHU/APL follows theguidelines established in JEDEC Standard JESD-22-A108, “Bias Life.” Dynamic bias is preferred, but notmandatory. Sample size for HTOL is 22 pieces. Thetime and temperature used are 1,000 hours, and+125°C, respectively. Unlike T/C or 85/85 testing,there is no need for preconditioning or to confor-mally coat. HTOL is concerned with infant mortalityand the long term reliability of devices to withstandtemperature extremes. At the completion of testing,final electrical measurements are taken at three tem-peratures.

6. LONG-TERM DORMANT STORAGE

The qualification tests outlined in Section 5, above,concentrate solely on the individual effects of tem-perature and/or moisture on PEMs. Limited studieshave been conducted on what has been classified asthe wooden-round concept. The wooden-round con-cept is concerned with the synergistic effects ofmoisture and temperature on PEMs under uncon-trolled long term dormant storage conditions.

JHU/APL has already completed one such study forthe U.S. NAVY F/A-18 Program. A total of 92 PEMswere involved in this effort, with parts dated as earlyas 1967. The results of the investigation revealed thatonly two devices, both 28 years in age, exhibited evi-dence of corrosion, and that a total of 91% of partswere delaminated.

Recently, JHU/APL has been selected to be an inde-pendent assessor for the U.S. ARMY MissileCommand (MICOM). The MICOM study involves16 PEM lots, consisting of 10 manufacturers, for atotal of 160 pieces per lot. Each lot will be split intothree groups of 50 parts, with three control samplesper group, and subjected to the testing outlined inFigure 4. The purpose of the study is to gain furtherknowledge of the synergistic effects of temperaturecycling and moisture on PEMs as related to long termdormant storage issues. Of particular interest are theeffects of these conditions in the presence of delami-nations. The performance of C-SAM and DPA, bothpre and post test, is done for this very reason.

EEE Links, Vol. 4 No. 3

13

REFERENCES[1] Casasnovas, A., and White, J. W., “Commercial

Plastic Encapsulated Microcircuits for NavalAviation Applications,” JHU/APL Technical Digest18 (1), 50-58, (1997).

[2] Nguyen, L.T., Lo, R. H. Y., Chen, A. S., and Belani,J. G., “Molding Compound Trends in a DenserPackaging World: Qualification Tests and Reli-ability Concerns,” IEEE Trans. on Reliability 42(4),529 (Dec 1993).

[3] Pecht, M. G., Nguyen, L. T., and Hakim, E. B.,Plastic-Encapsulated Microelectronics: Materials,Processes, Quality, Reliability, and Applications,John Wiley & Sons, New York (1995).

[4] Lantz, L. II, “Fundamental Studies in Plastic En-capsulated Microcircuits,” in Advanced PlasticEncapsulated Microelectronics Short Course,CALCE Electronic Packaging Research Center,University of Maryland College Park, (Aug 1997).

[5] Cooper, K., “Plastic Bag Study,” JHU/APL Memo-randum SOR-3-94088, (Oct 1994).

[6] Gardner, J. R., “The Appropriateness of PlasticEncapsulated Microcircuits in a Specific Wooden-

Round Application,” IEEE Trans. on Reliability 45(1), 10-18 (Mar 1996).

[7] Condra, L., O’Rear, Freedman, T., Flancia, L.,Pecht, M., and Barker, D., “Comparison of Plasticand Hermetic Microcircuits Under TemperatureCycling and Temperature Humidity Bias,” IEEETrans. on Components, Hybrids, And ManufacturingTechnology 15 (5), 640-650 (Oct 1992).

[8] Maurer, R. H., Le, B. Q., Nhan, E., Lew, A. L., Gar-rison Darrin, M. A., “Fabrication and Qualificationof Coated Chip-On-Board Technology For Minia-turized Space Systems,” in Proc. 3rd ESA ElectronicComponents Conference, ESTEC, Noordwijk, TheNetherlands, 22-25 April 1997, ESA SP-395 (July1997), pp 199-204.

[9] McCluskey, P., “Uprating: Introduction and KeyConcerns,” in Electronic Component Management& Uprating Workshop, CALCE Electronic Pack-aging Research Center, University of MarylandCollege Park, (Aug 1997).

[10] Shaneyfelt, M. R., Winokur, P. S., Fleetwood, D.M., Hash, G. L., Schwank, J. R., and Sexton, F. W.,“Impact of Aging on Radiation Hardness,” IEEETrans. On Nuclear Science 44(6), 2040-2047, (Dec1997).

Figure 4. JHU/APL U.S. ARMY MICOM Study. Investigating the effects of multiple environmentalstresses applied to PEMs.

DPA C-SAMFAILUREANALYSIS

VISUALINSPECTION

ELECTRICAL3 TEMP.

PRE-CONDITIONING

DPA

C-SAM

T/C-40°C TO +85°C

150 CYCLES

ELECTRICAL3 TEMP

HAST130°C/85%RH

100 HOURBIASED

REPEAT?

YES

ELECTRICAL3 TEMP

T/C-65°C TO +150C

100 CYCLES

ELECTRICAL3 TEMP

HAST121°C/85%RH

100 HOURUNBIASED

REPEAT?

YES

ELECTRICAL3 TEMP

T/C-55°C TO +125C

125 CYCLES

ELECTRICAL3 TEMP

HAST121°C/85%RH

100 HOURBIASED

REPEAT?

YES

ELECTRICAL3 TEMP

NO

NO

NO

EEE Links, Vol. 4 No. 3

14

AUTHORS

Anthony Casasnovas received a B.S. degree in elec-trical engineering from the Instituto Technológico deSanto Domingo, Dominican Republic, in 1987 and amaster’s degree in engineering management from theGeorge Washington University in 1995. He joinedAPL in 1994. He is a member of IEEE. He previouslyworked at Unisys Corporation in Lanham, Marylandin support of various NASA Goddard Space FlightCenter programs. Mr. Casasnovas is a Senior Com-ponent Reliability and Performance AssuranceEngineer for APL’s Space Reliability and Quality As-surance Group. His e-mail address [email protected].

Andrew F. Moor is a Senior Staff engineer in APL’sSpace Department. He received his B.S. degree inengineering science in 1987 from Loyola College. Hethen attended George Washington University andreceived an M.E.M. degree in engineering manage-ment in 1995. Mr. Moor joined APL’s SpaceReliability and Quality Assurance Group in 1993 andis currently the lead Component Reliability and Per-formance Assurance Engineer for several APLprograms. He is a member of IEEE. He previouslyworked at Unisys Corporation, in support of variousNASA Goddard Space Flight Center programs, andWestinghouse Advanced Technology Labs, in sup-port of various DOD programs. His e-mail address [email protected].

________________________________

Programmable Logic ApplicationNotes

by Richard KatzMicroelectronics and Signal Processing Branch

Goddard Space Flight Center301-286-9705

[email protected]://rk.gsfc.nasa.gov

This column will be provided each quarter as asource for reliability, radiation results, NASA capa-bilities, and other information on programmablelogic devices and related applications. This quarter’scolumn will include some announcements and somerecent radiation test results and evaluations of inter-est. Specifically, the following topics will be covered:the Military and Aerospace Applications of Pro-grammable Devices and Technologies Conference to

be held at GSFC in September, 1998, proton test re-sults, heavy ion test results, and some total doseresults.

MAPLDRegistration is now open for the Military and Aero-space Applications of Programmable Devices andTechnologies Conference, to be held at NASA’s God-dard Space Flight Center September 15-16, 1998. Latenews poster papers are also being accepted. Theprogram will consist of 4 invited talks, 4 technicalsessions, a poster session, and an industrial exhibit.For registration and program information, includingabstracts, please see http://rk.gsfc.nasa.gov.

NSREC ’98The 35th Annual Nuclear and Space Radiation EffectsConference was held in Newport Beach, California,July 20-24. Several papers were presented coveringprogrammables and ASICs including: Current Radia-tion Issues for Programmable Elements and Devices, R.Katz, et. al., which gives an overview of state-of-the-art technology and their radiation characteristics,Erasure of Floating Gates in the Natural Radiation Envi-ronments of Space, P. McNulty, et. al., which discussedthe floating gate technology, Single Event Effect andProton Damage Results for Candidate Spacecraft Elec-tronics, M. O’Bryan, et. al., which gives a broadoverview of recent technologies, Total Dose and SingleEvent Effects Testing of UTMC Commercial RadHardGate Arrays, D. Kerwin, et. al., showing radiation-hard performance, High Total Dose Response of theUTMC Gate Array Fabricated at Lockheed-Martin FederalSystems, J. Benedetto, et. al., showing the capability ofthe ASIC on the radiation-hardened line, Total Ioniz-ing Dose Effects on Flash Memories, D. Nguyen, et. al.,showing the effect of internal cell structures andcharge pumps on radiation performance, Anatomy ofan In-flight Anomaly: Investigation of Proton-InducedSEE Test Results for Stacked IBM DRAMs, K. LaBel, et.al., discusses test techniques for devices with smallcross-sections, including the A1280A, etc., and Neu-tron Single Event Upsets in SRAM-based FPGAs,discusses the performance of an SRAM-based FPGAwith neutrons.

MAPLUGA military/aerospace programmable logic usersgroup is being formed. The goal of the organizationis, similar to other disciplines, promote sharing of

EEE Links, Vol. 4 No. 3

15

ideas, techniques, information, product announce-ments, alerts, and experiences between users of thetechnology, parts and reliability engineers, and ven-dors. Individuals and vendors may join by emailing:[email protected]. There will be no feeand no advertising. Membership lists will by defaultnot be distributed as we wish to remain spam-free.

Proton Test Results from IUCFA variety of FPGAs and a quick-turn ASIC wastested at the Indiana University Cyclotron Facility inJune, 1998. All tests were run with ~ 193 MeV pro-tons; the fluence varied according to the part typeand test being performed. Devices tested were theRH1020, QL3025, A1280A/MEC, A54SX16 prototype(CSM), RT54SX16 prototype (MEC), and the QYH530(Yamaha, two lots). The internal code name ‘CKJ911’was used for the A54SX16 prototype in the test re-port.

Below are reports on each of the tests. These areavailable on-line at http://rk.gsfc.nasa.gov. Key re-sults included good SEU performance of the 0.35µm/3.3V devices from Actel and Quicklogic. Smallcross-sections were measured for the RH1020 and theA1280A devices. No upsets were detected in theQYH530, operated at VCC = 3.3VDC.

Total dose responses of the devices involved in thistest was also measured, with ICC vs. total dose curvesgiven for many of the devices; tables are provided forsome. There was reasonable agreement between theradiation response with protons and the Cobalt-60radiation tests. No latchups, clock upsets, or configu-ration upsets were detected from SEU affects.

SUMMARY OF PROTON TEST ON THE ACTELA1280A AT INDIANA UNIVERSITY

JUNE, 1998Prepared by: R. Katz, K. LaBel NASA/GSFC

Date: June 23, 1998Test FacilityThe Actel A1280A FPGA was tested at the IndianaUniversity Cyclotron Facility (IUCF). The protonenergy was 193 MeV and the flux was set at ap-proximately 2 x 108 p/cm2/sec. The total fluence foreach device was determined by the total dose re-sponse of the device and it’s affect on the currentdraw; details for each device including bias are given

in the tables below. The device was irradiated nor-mal to the beam.

Device Under TestThe A1280A devices were in a CPGA176 packageand were active during irradiation. All die werefrom the Matsushita (MEC) foundry with a 1.0 µmfeature size. Upsets and currents were monitored inreal-time with the device being clocked at 1 MHz.The stimulation pattern was a 500 kHz square wave.The test pattern used, the TMRA2.C, contains 522 S-Module flip-flops and 40 C-Module flip-flops.

Sample devices were taken from several lots usedpreviously in radiation tests along with a few ‘sparedevices’ to increase sample size. A total of 19 deviceswere used in this study. The intent of the study wasto investigate the proton response of the hard-wiredS-Module flip-flops with a large sample size. Previ-ous testing did not detect proton upset within theoperating voltage range but used a low fluence.

TEST RESULTS

Nineteen devices were irradiated, with 12 devices ata worst-case bias of 4.5V and the remaining 7 devicesat a nominal bias of 5.0V. An estimate of the cross-sections, by lot and bias, are given in Table 1 and Ta-ble 2, above. Previous tests of the A1280 (1.2 µm) andthe A1280A (1.0 µm) did not detect proton upset.The large sample size for this study, with upsets de-tected in each device, shows that this device issensitive to protons for S-Modules. No upsets weredetected in the C-module flip-flops. However, therewas a small number of flip-flops in this pattern so adifferent pattern should be used for measuring the C-module flip-flops’ sensitivity to protons. Note thatthe C-module flip-flops in the RH1020, tested in June1998, have a small, but non-zero cross-section for 193MeV protons.

There was no clock upset detected in any of the devices.The device’s total dose performance falls into the ra-diation-soft range, typical for devices of this class.The data within a lot was relatively consistent.

EEE Links, Vol. 4 No. 3

16

Table 1. Summary for VCC = 4.5VDC.

S/NLot Total

DosekRads

(Si)

Upsets Fluence (p/cm2)Estimated

Cross-Section(cm2/flip-flop)

by LotBC284 9424 5 6 80 x 109

BC283 9424 5 2 80 x 109

BC209 9424 5 4 80 x 109 96 x 10-15

JJ9 9614 Lot Split 2 5 5 80 x 109 120 x 10-15

JJ1 9614 Lot Split 3 7 13 112 x 109

JJ2 9614 Lot Split 3 7 7 112 x 109

JJ10 9614 Lot Split 3 5 2 80 x 109 139 x 10-15

JJ5 9614 Lot Split 4 7 9 112 x 109

JJ6 9614 Lot Split 4 7 14 112 x 109

JJ11 9614 Lot Split 4 5 6 80 x 109

JJ12 9614 Lot Split 4 5 4 80 x 109165 x 10-15

Table 2. Summary for VCC = 5.0VDC.

S/NLot Total

DosekRads

(Si)

Upsets Fluence(p/cm2)

EstimatedCross-Section

(cm2/flip-flop)by Lot

JJ3 9614 Lot Split 3 7 7 112 x 109

JJ4 9614 Lot Split 3 7 9 112 x 109137 x 10-15

BC203 9424 5 5 80 x 109

BC104 9424 5 2 80 x 10983.8 x 10-15

JJ7 9614 Lot Split 4 7 8 112 x 109

JJ8 9614 Lot Split 4 7 10 112 x 109154 x 10-15

RK1 9415 5 4 80 x 109 95.8 x 10-15

A1280A Proton TestVCC = 4.5 VDC

Indiana University, June, 1998193 MeV, 2E8 p/cm^2/Sec

NASA/GSFC

kRads (Si)0 1 2 3 4 5 6 7 8

Del

ta I C

C (m

A)

0

1

2

3

4

JJ Series, Lot Split 3, S/N's JJ1, JJ2, JJ10BC Series, S/N's BC283, BC284, BC209

JJ Series, Lot Split 4, S/N's JJ5, JJ6, JJ11, JJ12, JJ13

JJ Series, Lot Split 2, S/N JJ9

A1280A Proton TestVCC = 5.0 VDC

Indiana University, June, 1998193 MeV, 2E8 p/cm^2/Sec

NASA/GSFC

kRads (Si)0 1 2 3 4 5 6 7 8

Del

ta I C

C (m

A)

0

1

2

3

4

5

6

7

JJ Series, Lot Split 3, S/N's JJ3, JJ4BC Series, S/N's BC104, BC203

JJ Series, Lot Split 4, S/N's JJ7, JJ8

RK Series, S/N RK1

EEE Links, Vol. 4 No. 3

17

SUMMARY OF PROTON TEST ON THE ACTELRH1020 AT INDIANA UNIVERSITY

JUNE, 1998Revision A.

Prepared by: R. Katz, NASA/GSFCDate: June 18, 1998

Test FacilityThe Actel RH1020 was tested at the Indiana Univer-sity Cyclotron Facility (IUCF). The proton energywas 193 MeV and the flux was set at approximately 1x 109 p/cm2/sec. The total fluence for each devicewas 1.6 x 1012 p/cm2 corresponding to a total dose of100 kRads (Si); details for each device including biasare given in the tables below. The device was irradi-ated normal to the beam.

Device Under TestThe devices were in a CQFP84 package and were ac-tive during irradiation. Upsets and currents weremonitored in real-time with the device being clockedat 1 MHz. The stimulation pattern was a 500 kHzsquare wave. Since the devices are quite hard to totaldose effects, the test equipment was run in an SEUtime-tagging mode to aid in the detection and in-strumentation of clock upsets. The test pattern used,TMRA1BRB, contains 136 flip-flops with 102 in aTMR configuration and 34 in a shift register. The Act1 architecture only has routed flip-flops; there are nohard-wired or I/O module flip-flops.

Sample devices were taken from two lots, a “pre-production” lot and a production lot. In this case, the

difference between the devices were an improvedclock buffer for ‘clock upset’ (production lot) and thethickness of the antifuses, with the production de-vices having a 90Å thick antifuse and the pre-production devices having a 96Å thick antifuse.

Test ResultsThe table included below summarizes the device,bias conditions, and irradiation.

Five devices were irradiated with a 5V bias and threewith a 4.5 bias with a total of 3 upsets for all of theruns. The cross-sections can be estimated as 1.8 x 10-

15 cm2/flip-flop at VCC = 5V and 1.5 x 10-15 cm2/flip-flop at VCC = 4.5VDC. Obviously, with the small er-ror counts, the statistics are poor, and it would beexpected that the device would have a larger cross-section at the lower bias level.

There was no evidence of any clock upset in eitherthe pre-production devices or the hardened produc-tion lot.

The device’s total dose performance was excellent,with changes of currents not exceeding more than afew hundred microamps. This also shows, as ex-pected, no antifuse damage. Previous testing hasshown that at LET = 37 MeV-cm2/mg, a bias of 6.1volts was necessary to rupture a production device(two samples tested). Note also that these deviceshad already been previously irradiated during heavyion tests.

S/N Lot Bias(Volts)

TotalDosekRads(Si)

Upsets Fluence(p/cm2)

RH3 Production 5.0 100 0 1.6 x 1012

RH4 Production 5.0 100 0 1.6 x 1012

RH6 Production 5.0 100 2 1.6 x 1012

RH1095 Pre-Production 4.5 100 0 1.6 x 1012

RH1098 Pre-Production 4.5 100 1 1.6 x 1012

RH1099 Pre-Production 5.0 100 0 1.6 x 1012

RH1101 Pre-Production 5.0 100 0 1.6 x 1012

RH3769 Pre-Production 4.5 100 0 1.6 x 1012

EEE Links, Vol. 4 No. 3

18

SUMMARY OF PROTON TEST ON THE ACTELCKJ911 PROTOTYPE AT INDIANA

UNIVERSITYJUNE, 1998

Prepared by: R. Katz, NASA/GSFCDate: June 18, 1998

Test FacilityThe Actel CKJ911 prototype FPGA was tested at theIndiana University Cyclotron Facility (IUCF). Theproton energy was 193 MeV and the flux was set atapproximately 1 x 109 p/cm2/sec. The total fluencefor each device was determined by the total dose re-sponse of the device and it’s affect on the currentdraw; details for each device including bias are givenin the chart below. The device was irradiated normalto the beam.

Device Under TestThe devices were in a PQFP208 package and wereactive during irradiation. Upsets and currents weremonitored in real-time with

the device being clocked at 1 MHz. The stimulationpattern was a 500 kHz square wave. The test patternused contains 400 flip-flops. The CKJ911 architectureonly has hard-wired flip-flops with the availablesoftware; there are no I/O module flip-flops.

Sample devices were taken from a prototype lot, withIDDSB currents higher than would be expected from afull-scale production lot. The “p-fuse” was not pro-grammed on these devices and the TCK pin (an inputto the IEEE 1149.1 JTAG TAP controller) was not ac-tive.

Test ResultsThe following table summarizes the device, bias con-ditions, and irradiations.

S/N Lot Bias(Volts)

TotalDose

kRads(Si)

Upsets Fluence(p/cm2)

CKJ1 Prototype 4.5/3.0 116.9 2 1.9 x 1012

CKJ2 Prototype 5.0/3.3 100.1 0 1.6 x 1012

Two devices were irradiated, one with biases of 4.5Vand 3.0V and the other with biases of 5.0V and 3.3V.An estimate of an upper bound for the cross-sectionscan be computed as 2.6 x 10-15 cm2/flip-flop at the

worst-case voltage and, assuming a single upset, as1.6 x 10-15 cm2/flip-flop at nominal supply voltages.

There was no clock upset detected in any of the de-vices and no upsets were detected in the JTAG TAPcontroller.

The device’s total dose performance was good, de-spite the high initial device bias currents. The doserate was high at 252 kRads (Si) / hour for S/N CKJ1and 316 kRads (Si) / hour for S/N CKJ2. Details areshown in the strip charts below for the 3.3V supplycurrents.

Only moderate (< 250 µA) changes in the 5V bias cur-rents were observed.

SUMMARY OF PROTON TEST ON THE ACTELRT54SX16 PROTOTYPE AT INDIANA

UNIVERSITYJUNE, 1998

Prepared by: R. Katz, NASA/GSFCDate: June 18, 1998

Test FacilityThe Actel RT54SX16 prototype FPGA was tested atthe Indiana University Cyclotron Facility (IUCF).The proton energy was 193 MeV and the flux was setat approximately 1 x 109 p/cm2/sec. The total flu-ence for each device was determined by the totaldose response of the device and it’s affect on the cur-rent draw; details for each device including bias aregiven in the chart below. The device was irradiatednormal to the beam.

CKJ911 193 MeV Proton TestIUCF - June, 1998

Flux ~ 1 x 10 9 p/cm2/SecS/N CKJ1, CKJ2 Prototype Lot

NASA/GSFCJune 18, 1998

kRads (Si)0 20 40 60 80 100 120

Del

ta I C

C3.

3DY

N(m

A)

0

20

40

60

80

S/N CKJ1 - Vcc = 4.5V/3.0VS/N CKJ2 - Vcc = 5.0V/3.3V

EEE Links, Vol. 4 No. 3

19

Device Under TestThe devices were in a PQFP208 package and wereactive during irradiation. Upsets and currents weremonitored in real-time with the device being clockedat 1 MHz. The stimulation pattern was a 500 kHzsquare wave. The test pattern used contains 400 flip-flops. The RT54SX16 architecture only has hard-wired flip-flops with the available software; there areno I/O module flip-flops.

Sample devices were taken from a prototype lot, andIDDSTDBY currents were normal, just a few hundredmicroamps. The “p-fuse” was programmed on thesedevices and the TCK pin (an input to the IEEE 1149.1JTAG TAP controller) was not active for runs withS/N MKJ1 and MKJ2; it was active at 6 kHz forMKJ3. The date code was 9733 with the chip alsomarked as PO6GNC WFR #7,8.

Test ResultsThe following table summarizes the device, bias con-ditions, and irradiations.

S/N Lot TCKBias

(Volts)

TotalDose

kRads

(Si)

UpsetsFluence(p/cm2)

MKJ1 PrototypeD/C 9733

Off 4.5/3.0 75.4 2 1.2 x 1012

MKJ2 PrototypeD/C 9733

Off 4.5/3.0 75.4 4 1.2 x 1012

MKJ3 PrototypeD/C 9733

6 kHz 5.0/3.3 103.1 2 1.6 x 1012

Three devices were irradiated, two with worst-casebiases of 4.5V and 3.0V and the other with a nominalbiases of 5.0V and 3.3V. An estimate of the cross-sections can be computed as 6.3 x 10-15 cm2/flip-flopat the worst-case voltage and as 3.1 x 10-15 cm2/flip-flop at nominal supply voltages. Obviously, with thelow error counts, more devices would be needed toget an accurate cross-section.

There was no clock upset detected in any of the de-vices and no upsets were detected in the JTAG TAPcontroller.

The device’s total dose performance was good, fal-ling into the rad-tolerant range. The curves for S/NMKJ1 and S/N MKJ2 are made by plotting static cur-rents at the end of each proton run, with the symbolsrepresenting each step. The curve for S/N MKJ3 is

the delta current recorded during the run. The doserate was high at about 250 kRads (Si) / hour. Onlymoderate (< 1.5 mA) changes in the 5V bias currentswere observed for S/N MKJ1 and S/N MKJ2. ForS/N MKJ3, which had the higher total dose, the 5Vbias current increased to 1.1 mA after 67 kRads (Si)and to 8.1 mA after 103 kRads (Si). Note that furtherexperiments on this part type has shown lot splitswith > 100 kRads (Si) total dose capability.

SUMMARY OF PROTON TEST ON THE CHIPEXPRESS QYH530 AT INDIANA UNIVERSITY

JUNE, 1998Prepared by: R. Katz, NASA/GSFC

Date: June 17, 1998

Test FacilityThe Chip Express QYH530 was tested at the IndianaUniversity Cyclotron Facility (IUCF). The protonenergy was 193 MeV and the flux was set at ap-proximately 1 x 109 p/cm2/sec. The total fluence foreach device was determined by the total dose re-sponse of the device and it’s affect on the currentdraw; details for each device including bias are givenin the tables below. The device was irradiated nor-mal to the beam.

Device Under TestThe devices were in a PGA180 package and were ac-tive during irradiation. Upsets and currents weremonitored in real-time with the device being clockedat 1 MHz. The stimulation pattern was a 500 kHzsquare wave. The test pattern used contains 1200 flip-flops. The QYH500 architecture only has routed flip-flops; there are no hard-wired or I/O module flip-flops.

RT54SX16 (Experimental) Proton TestIndiana University, June, 1998

193 MeV, 109 p/cm2/SecNASA/GSFC

kRads (Si)

0 10 20 30 40 50 60 70 80

Del

ta I C

C3.

3 (m

A)

0

20

40

60

80

100

S/N MKJ1, Vcc = 4.5V/3.0V, staticS/N MKJ2, Vcc = 4.5V/3.0V, staticS/N MKJ3, Vcc = 5.0V/3.3V, delta ICC, dynamic

EEE Links, Vol. 4 No. 3

20

Sample devices were taken from two lots, a “DITS-2”flight lot and a production lot used for shielding ex-periments; no radiation shields were used on any ofthe devices in this test. All devices were processedwith Chip Express’ One-Mask technology with nolaser programmed devices tested during these runs.These devices had already been subjected to heavyion tests at Brookhaven National Laboratory.

Test Results

The following table summarizes the device, bias con-ditions, and irradiations.

S/N Lot Bias(Volts)

TotalDosekRads

(Si)

Upsets Fluence(p/cm2)

QYHD1 DITS-2 4.5 18.9 0 0.3 x 1012

QYHD2 DITS-2 3.3 25.1 0 0.4 x 1012

QYHD3 DITS-2 3.3 25.1 0 0.4 x 1012

QYH55 LOT OF 70 3.3 25.1 0 0.4 x 1012

QYH56 LOT OF 70 3.3 25.1 0 0.4 x 1012

Five devices were irradiated, one with a 4.5V biasand four with a 3.3 bias with no upsets for all of theruns. An estimate of an upper bound for the cross-sections can be computed, assuming a single upset,as 0.5 x 10-15 cm2/flip-flop. There was no clock upsetdetected in any of the devices.

The device’s total dose performance was good, eventhough the devices had been previously irradiated.Nevertheless, the following table and figure shows

radiation-tolerant performance. The dose rate washigh at 216 kRads (Si) / hour.

Table 1. Static current after each run in mA.Note: Devices previously irradiated with heavy ions.

6.3 kRads(Si)

12.6 kRads(Si)

18.8 kRads(Si)

25.1 kRads(Si)

QYHD1 0 1.7 31.6QYHD2 0 0.6 8.5 35.9QYHD3 0 0.0 7.3 32.9QYH55 0 0.2 5.1 25.5QYH56 0 0.0 3.3 23.3

SUMMARY OF PROTON TEST ON THE QUICKLOGIC QL3025 AT INDIANA UNIVERSITY

JUNE, 1998Prepared by: R. Katz,

NASA/GSFCDate: June 16, 1998

Test FacilityA pAsic3 QL3025 was tested at the Indiana Univer-sity Cyclotron Facility (IUCF). The proton energywas ~ 193 MeV and the flux was set at approximately1 x 109 p/cm2/sec. The total fluence for the run was5.12 x 1011 p/cm2 corresponding to a total dose of32.1 kRads (Si). The device was irradiated normal tothe beam.

Device Under TestThe device was in a PQFP208 package and was activeduring irradiation. Upsets and currents were moni-tored in real-time with the device active at 1 MHz.The stimulation pattern was a 500 kHz square wave.Both internal hard-wired flip-flops and I/O moduleflip-flops were tested. This pattern contains 500 in-ternal flip-flops with 300 in a TMR configuration and200 in a shift register. 50 I/O module flip-flops weretested.

Test ResultsNo upsets were detected for this one sample, consis-tent with our quick-look heavy ion data, taken at anLET of 18.8 MeV-cm2/mg. The total fluence for theheavy ion data was limited and complicated by thedevice’s latchup characteristics. No evidence oflatchup or any unusual current disturbances wereobserved.

QYH530 193 MeV Proton TestFlux = 1 x 109 p/cm2/SecS/N QYHD2 - DITS-2 Lot

NASA/GSFCJune 17, 1997

kRads (Si)0 5 10 15 20 25

Del

ta I C

C (m

A)

0

10

20

30

40

Note: Device Previously Irradiated for Heavy Ion Testing

EEE Links, Vol. 4 No. 3

21

The device showed a moderate increase in current atapproximately 20 kRads (Si) and a current runawayat approximately 31 kRads (Si). This is thought to bea consequence of a charge pump failure. The totaldose data, shown in the chart below, is comparable toour Cobalt-60 data where the device exhibited run-away at approximately 37 kRads (Si), while dosed atthe relatively low rate of 0.5 kRads (Si)/hour in astatic configuration. Dose rate during the proton ir-radiation was at the much higher rate of ~ 247 kRads(Si)/hour.

Functional Failure of EEPROMs in the Heavy IonEnvironmentIt has been demonstrated that devices, includingEEPROMs, may lose functionality when upset by asingle heavy ion. The Atmel AT28C010 is one exam-ple. Additionally, excess current was observed in thedevice. No permanent damage was detected. For theAT28C010, three types of SEUs were identified. onetype was an upset in the output register, causing aread operation to fail. Additionally, there were twotypes of upsets where the device lost functionalityover multiple cycles and entering a non-operatingstate.

This phenomena was covered in a good overview in“Single Event Functional Interrupt (SEFI) in Micro-circuits,” published in RADECS 97, Proceedings ofthe Fourth European Conference on Radiation and itsEffects on Components and Systems. The authors areR. Koga, S. Penzin (Crain), K. Crawford, and W.Crain from the Aerospace Corporation.

Recently, a similar effect was demonstrated andanalyzed in FPGAs utilizing IEEE 1149.1 JTAG cir-cuitry, in an implementation without the optionalTRST- pin. An application note on use of JTAG is inpreparation and will be published shortly.

Act 1 SEU SummaryThe Act 1 architecture has been fabricated in a num-ber of technologies, many of which are utilized inspace flight hardware. These consist primarily of theMEC foundry 2.0, 1.2, and 1.0 µm devices as well asthe RH1020 built at Lockheed-Martin. The followingchart summarizes the SEU performance of these de-vices. Some other variants are being flown, such asthe TI A1020B, but this is relatively infrequent andthe data is not included here.

Antifuse HardnessThe following chart gives an update on antifusehardness testing. Shown here is data on the RH1020devices as well as prototypes from the SX series ofFPGAs. Please note that these are prototypes usedfor technology assessment and development. Char-acteristics of production devices will differ and theuser should be sure to obtain up-to-date data.

None of the antifuse ‘recipes’ showed any problemsat an LET of 37 MeV-cm2/mg with the ions normal tothe device, which is worst-case for this effect. Notethat the usual cosine law for SEU and SEL do not ap-ply here. Of particular note is antifuse recipe ‘M’,which was hard (four sample devices) at an LET of82.3 MeV-cm2/mg with VDD = 4.0 VDC; maximumrated voltage for this class of device is 3.6 VDC.

QL3025 Proton IrradiationS/N QL6

June, 1998Indiana University Cyclotron

NASA/GSFC

kRads (Si)0 5 10 15 20 25 30 35

I CC

3.3

(mA

)

1

10

100

1000

Act 1 Family SEU Flip-Flop Data

LET (MeV-cm2/mg)0 20 40 60 80 100 120 140

X-S

ec (c

m2 /F

lip-F

lop)

10-10

10-9

10-8

10-7

10-6

10-5

A1020 (2.0 µm)A1020A (1.2 µm)RH1020 (1.0 µm) @ BNL RH1020 (1.0 µm) @ TAMU A1020B (1.0 µm) @ BNLRH1020 (1.0 µm) @ BNL May '98

EEE Links, Vol. 4 No. 3

22

SEU Comparison of 1.0, 0.6, and 0.35 µm Hard-wiredFlip-FlopsThe following chart shows the SEU response of hard-wired flip-flops from an A1280A (5V/1.0 µm) andprototype RT54SX16 (3.3V/0.6 µm) and A54SX16(3.3V/0.35 µm) devices. The hard-wired flip-flopsare dedicated on the chip and are not formed byfeedback connections in the routing channels. Theseare called ‘S-Module flip-flops’ in the A1280A and ‘R-Cell’ in the SX architecture.