EE 5301 – VLSI Design Automation I Part I: IntroductionPart I:...

Transcript of EE 5301 – VLSI Design Automation I Part I: IntroductionPart I:...

1

EE 5301 – VLSI Design Automation I

Part I: IntroductionPart I: Introduction

1

Administrative issues

• Class Time and venue: MW 12:20pm – 1:35pm, ME 108 Web page:

o http://www.ece.umn.edu/class/EE5301 Textbook:

Sadiq M. Sait, Habib Youssef, "VLSI Physical Design Automation: Theory and Practice", World Scientific Publishing Company,1999.

G d• Grades 30% homework (~5 homeworks) 20% each, two midterms

o Tentative dates: Mon Oct 22, Wed Nov 26 30% mini-projects (~2 mini-projects)

o Includes oral presentation for the second Programming required!

2

Administrative issues (contd.)

• Personnel Instructor: Sachin Sapatnekar

o Email: [email protected]

o Phone: (612) 625-0025o Office: 4-153 EE/CScio Office hours: MW 11am-noon, or by appointment

TA: TBDo Email: [email protected]

o Phone: (612) 62x xxxxo Office: x-xxx EE/CScio Office hours: TBD, or by appointment

3

2

Administrative issues (cont.)

• Policies Electronic submission of homework preferred

o Must be received by the due date

o If you submit a hardcopy, it must be in before class starts

o You will lose 10% of the total score for each day or part thereof

• Example: If the HW is graded out of 100 and you are 30 hours late, you automatically lose 20 points

Zero tolerance for cheating

Collaboration OK, copying NOT OK

No extra work for extra credit

Check class web pages regularly, students are responsible for checking discussion threads and announcements regularly

Subscribe to the class mailing list (instructions on the web page)

4

Online slides

• Slides are posted on the web Handouts posted as .pdf files Powerpoint slides provided too

o NOTE: some slides are animated (like this one)o Click on the slide to see the animationo Click once more.

o Some slides contain text that is not printed in the handouts, but animated. These are left for you to fill out in the handouts. An example is shown below (animated: click to see)

This is a sample text, not printed, but animated

5

What is this course all about?

• Prerequisite C / C++ programming experience

• What is covered? Basic algorithms, complexity theory Integrated circuit (IC) Design flow Computer Aided Design (CAD) tool development for Very Large

Scale Integration (VLSI)Scale Integration (VLSI) Lots of programming!

• Next slides: Overview of IC design steps Related courses at U of M Outline of this course

6

3

The overall IC industry

7

IC products• Processors

CPU, DSP, Controllers• Memory chips

RAM, ROM, EEPROM• Analog

Mobile communication,audio/video processing

• Programmable PLA, FPGA

• Embedded systems Used in cars, factories Network cards

• System-on-chip (SoC)

Boom!8

The inverted pyramid

Electronic Systems > $1 Trillion

[©Keutzer]

Semiconductor > $220 B

CAD $4 B

9

4

Semiconductor industry growth rates

Source: http://www.icinsight.com/ (McClean Report)

[©Bazargan] 10

More demand for EDACAE =

Compute

Source: http://www.edat.com/edac

er Aided Engineering

[©Bazargan] 11

Growth in system size

CAGR = Com

poun

Source: http://www.edat.com/edac

nd Annual Growth Rate

[©Bazargan] 12

5

Evolution of the transistor

Transistor

http://ww

w.nobe

/poster/2000/kilb y

Early IC

Vacuum tube

(http://www.pbs.org/transistor/teach/teacherguide_html/lesson1.html)

l.se/physics/educationaly.htm

l

Modern IC

13

Acronyms, acronyms everywhere..

• SSI (small scale integration)• MSI (medium scale integration)• LSI (large scale integration)• VLSI (very large scale integration)• …

14

Example: Intel processor sizes

Intel386TM DXProcessor

Intel486TM DXProcessor

1.5 1.0 0.8 0.6 0.35 0.25Silicon ProcessTechnology

Source: http://www.intel.com/

Processor

Pentium® Processor

Pentium® Pro &Pentium® II Processors

15

6

Moore’s law

[intel.com]

16

The Moore’s law article

Electronics, Vol. 38, No. 8, Apr 19, 1965

17

Feature size trends

• Recent history0.8m0.5m0.35m0.25m0.18m0.13m90nm

65nm45nm

• Projected technologies 32nm22nm16nm

• 0.7x per generation, 0.5x every two generations

[R. Saleh]

18

7

Starting up a technology node

19

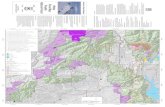

The International Technology Roadmap for Semiconductors (ITRS) [public.itrs.org]

YearTech Node(nm)

Num of

Tran

Num Wire Level

f(MHz)

Vdd

(V)Power(W)(nm) Tran Level

2001 130 97M 8 1.7 1.2 1302003 100 153M 8 3.1 1.0 1502005 80 243M 10 5.2 0.9 1702007 65 386M 10 6.7 0.7 1902010 45 773M 10 11.5 0.6 2182013 32 1.55G 11 19.3 0.5 2512016 22 3.09G 11 28.8 0.4 288

20

ITRS: Chip frequencies

Clock speed GHz

57

9

11

[©Keutzer]

01

3

1997 1999 2001 2003 2006 2009 2012

On-chip, local clock, high performance

On-chip, global clock, high performance

21

8

The role of design automation

22

Tera-scale integration effects

• Exponential increase in device complexity Increasing with Moore's law (or faster)!

• More complex system contexts System contexts in which devices are deployed (e.g.

cellular radio) are increasing in complexity

• Require exponential increases in design productivity

Complex

productivity

[©Keutzer]

We have exponentially more transistors!

xity

23

Nanometer-scale effects

• Smaller geometries are causing a wide variety of effects that we have largely ignored in the past: Cross-coupled capacitances Signal integrity Wire resistance effects Wire inductance effects

DSM Effects

Wire inductance effects Increased leakage Quantum effects Reliability problems…

[©Keutzer]

Design of each transistor is getting more difficult!

s

24

9

Heterogeneity on chip

• Greater diversity of on-chip elements Processors Software Memory Analog

• “more than Moore” technologies

Heterogeneity

• more than Moore technologies

[©Keutzer]

More transistors doing different things!

25

Stronger market pressures

• Decreasing design window• Lower tolerance for design

revisions

Time-to-market

[©Keutzer]

Exponentially more complex, greater design risk, greater variety, and a smaller design window!

26

A Quadruple-Whammy

k

Tera-scale integration

[©Keutzer]

Time-to-market

Nanometer-scale

Effects

Heterogeneity

27

10

Productivitygap

How are we doing?

oduc

tivity

/ St

aff .

Mon

th

10,000

100,000

1,000,000

10,000,000

100,000,000

sist

ors

per c

hip

(K)

1,000

10,000

100,000

1,000,000

10,000,00058% / Yr. compound

complexity growth rate

g p

Role of EDA: close the productivity gap[©Keutzer]

Source:SEMATECH

Pro

Tran

s. /

10

100

1,000

,

Logi

c tra

ns

10

100

,

1981

1985

1989

1993

1997

2001

2005

2009

21% / Yr. compoundproductivity growth rate

28

Evolution of the EDA industry

Results(design productivity)

Synthesis – Cadence, Synopsys

What’s next?

[©Keutzer]

Effort(EDA tool effort)McKinsey S-Curve

Transistor entry – Calma, Computervision, Magic

Schematic entry – Daisy, Mentor, Valid

29

The IC design cycle

30

11

IC design steps (cont.)

SpecificationsSpecifications High levelHigh-levelDescription

FunctionalDescriptionFunctionalDescription

BehavioralVHDL, C

StructuralVHDL

Figs. [©Sherwani] 31

PhysicalDesign

TechnologyMa i g

Synthesis

IC design steps (contd.)

SpecificationsSpecifications High levelHigh-levelDescription

FunctionalDescriptionFunctionalDescription

Packaging Fabri-cation

Design MappingPlaced

& RoutedDesign

X=(AB*CD)+(A+D)+(A(B+C))

Y = (A(B+C)+AC+D+A(BC+D))

Figs. [©Sherwani]

Gate levelGate-levelDesign Description

LogicDescription

32

The big picture: IC design methods

Full Custom

Standard Cell

DesignMethods

Cost /Development

Time

Quality # Companiesinvolved

ASIC – StandardCell Design

Standard CellLibrary Design

RTL-Level Design

[©Bazargan] 33

12

Optimization: Levels of abstraction

• Algorithmic Encoding data, computation

scheduling, balancing delays of components, etc.

• Gate-level Reduce fan-out, capacitance Gate duplication, buffer insertion ve

ness

deta

il

p ,

• Layout / Physical-Design Move cells/gates around to shorten

wires on critical paths Abut rows to share power / ground

linesEf

fect

iv

Leve

l of d

[©Bazargan] 34

Full custom designStructural/RTL Description

Mem

Ctrl

Comp.Unit

RegFile

Component Design

...

Layouts [© Prentice Hall]Floorplan [©Sherwani]

Place & Route

A/DPLA

I/Ocomp

RAM

35

Full custom design example (simplified)

PLA I/Ocomp

Metal1

Via

Metal2

I/O Pad

A/D

RAM

Glue logic(standard

cell design)

Macrocell

design

[©Sherwani]

36

13

ASIC designStructural/

RTL Description

Mem

Ctrl

Comp.Unit

RegFile

HDL ProgrammingP_Inp: process (Reset, Clock)begin

if (Reset = '1') thensum <= ( others => '0' );input_nums_read <= '0';sum_ready <= '0';

add82 : kadd8 port map (a => add i1, b => add i2,a > add_i1, b > add_i2,ci => carry, s => sum_o);

Mult_i1 <= sum_o(7 downto 0);

Floorplan [©Sherwani]C DA B

Cell library

D C C B

A C C

D C D B

BCCC

37

ASIC (Standard Cell) design example (simplified)

D C C B

A C C

CellMetal1 Metal2GNDVDD

C C

D C D B

BCCC

C DA B

Cell library

Placement [©Sherwani]

38

How does this course fit into the curriculum?

• VLSI related courses:

VLSI CAD VLSI Design Others

EE 4301Digital Design

With ProgrammableLogic

EE 5323VLSI Design I

EE 5301VLSI Design

Automation I

EE 5329VLSI Digital

Signal ProcessingSystems

EE 5333Analog

Integrated CircuitDesign

EE 5549Digital

Signal ProcessingStructures for VLSI

EE 5324VLSI Design II

EE 5302VLSI Design

Automation II

39

14

Course outline

• Basic algorithms and complexity theory Circuit representations Classes of problems (P, NP) Classes of algorithms (dynamic programming, network flow,

greedy, linear programming, etc.) Graph algorithms

[©Bazargan] 40

Course outline (contd.)

• Global / detailed routing Maze routing, line-search, Steiner trees, etc.

• Partitioning FM, KL, hMetis algorithms

• Floorplanning Slicing, non-slicing floorplans

S l d l fl l l h Simulated annealing floorplanning algorithms

• Placement / Packing Force-directed Simulated annealing Quadratic placement

[©Bazargan] 41

To Probe Further...

• International Technology Roadmap for Semiconductors (ITRS) http://public.itrs.net/

• SEMATECH http://www.sematech.org/

• TextbookCh Chapter 1

[©Bazargan] 42