Dual-Phase, Quick-PWM Controllers for IMVP-IV CPU Core Power...

Transcript of Dual-Phase, Quick-PWM Controllers for IMVP-IV CPU Core Power...

General DescriptionThe MAX1987/MAX1988 are dual-phase, Quick-PWM™,step-down controllers for IMVP-IV™ CPU core supplies.Dual-phase operation reduces input ripple currentrequirements and output voltage ripple, while easingcomponent selection and layout difficulties. The Quick-PWM control scheme provides instantaneous response tofast load-current steps. The MAX1987/MAX1988 includeactive voltage positioning with adjustable gain and offset,reducing power dissipation and bulk output capacitancerequirements.

The MAX1987/MAX1988 are intended for two differentnotebook CPU core applications: stepping down thebattery directly or stepping down the 5V system supplyto create the core voltage. The single-stage conversionmethod allows these devices to directly step down high-voltage batteries for the highest possible efficiency.Alternatively, two-stage conversion (stepping down the5V system supply instead of the battery) at higherswitching frequency provides the minimum possiblephysical size.

The MAX1987/MAX1988 meet the IMVP-IV specifica-tions and can directly interface with the CPU power-good signals from the VCCP and VCCMCH rails withinthe system. The switching regulator features power-upsequencing, automatically ramping up to the Intel-specified boot voltage. The MAX1987/MAX1988 alsofeature independent four-level logic inputs for settingthe boot voltage (B0 to B2) and the suspend voltage(S0 to S2).

The MAX1987/MAX1988 include output undervoltageprotection, thermal protection, and system power-OK(SYSPOK) input. When any of these protection featuresdetect a fault, the controller shuts down. Additionally,the MAX1987 includes overvoltage protection.

The MAX1987/MAX1988 are available in a low-profile48-pin 7mm 7mm Thin QFN package.

ApplicationsIMVP-IV Notebook Computers

Multiphase CPU Core Supply

Voltage-Positioned Step-Down Converters

Servers/Desktop Computers

Features♦ Dual-Phase, Quick-PWM Controllers

♦ ±0.75% VOUT Accuracy Over Line, Load, andTemperature

♦ Active Voltage Positioning with Adjustable Gainand Offset

♦ 6-Bit On-Board DAC (16mV Increments)

♦ 0.492V to 1.708V Output Adjust Range

♦ Selectable 200kHz/300kHz/550kHz SwitchingFrequency

♦ 2V to 28V Battery Input Voltage Range

♦ Adjustable Slew Rate Control

♦ Drives Large Synchronous Rectifier MOSFETs

♦ Output Overvoltage Protection (MAX1987 Only)

♦ Undervoltage and Thermal Fault Protection

♦ IMVP-IV Power Sequencing and Timing

♦ Selectable Boot and Suspend Voltages

♦ Low-Profile 7mm 7mm 48-Pin Thin QFNPackage

MA

X1

98

7/M

AX

19

88

Dual-Phase, Quick-PWM Controllers for IMVP-IVCPU Core Power Supplies

________________________________________________________________ Maxim Integrated Products 1

Ordering Information

19-2559; Rev 0; 7/02

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim’s website at www.maxim-ic.com.

Typical Operating Circuit appears at end of data sheet.

PART TEMP RANGE PIN-PACKAGE

MAX1987ETM -40°C to +100°C 48 Thin QFN 7mm 7mm

MAX1988ETM -40°C to +100°C 48 Thin QFN 7mm 7mm

VDD

DLM

LXMBSTM

D1

D2D3

D5D4

D0

DHMB0B1B2S0

S1S2

VCC

REFILIM

TONTIME 1

2

3

4

5

6

7

8

9

10

11

12

36

35

34

33

32

31

30

29

28

27

26

25

CCI

FBOA

IN-

OAIN

+PS

I

IMVP

OKSY

SOK

NEG

POS

CCV

GND

CSN

CMN

CMP

SUS

V+ BSTS

LXS

DHS

PGND

DLS

CSP

7mm x 7mm THIN QFN

MAX1987MAX1988

TOP VIEW

48 47 46 45 44 43 42 41 40 39 38 37

13 14 15 16 17 18 19 20 21 22 23 24

SHDN

CLKE

N

DD0

DPSL

P

Pin Configuration

Quick-PWM is a trademark of Maxim Integrated Products, Inc.

IMVP-IV is a trademark of Intel Corp.

CONFIDENTIAL INFORMATION—RESTRICTED TO INTEL IMVP LICENSEES

PRELIMINARY

PRELIMINARY

MA

X1

98

7/M

AX

19

88

Dual-Phase, Quick-PWM Controllers for IMVP-IVCPU Core Power Supplies

2 _______________________________________________________________________________________

ABSOLUTE MAXIMUM RATINGS

ELECTRICAL CHARACTERISTICS(Circuit of Figure1, V+ = 15V, VCC = VDD = VSHDN = VTON = VDPSLP = VPSI = VB1 = VOAIN- = 5V, VB2 = 2V, VFB = VCMP = VCMN =VCSP = VCSN = VOAIN+ = VNEG = VPOS = 1.26V, VD4 = VD3 = VD2 = 1.0V, VSUS = VD5 = VD1 = VD0 = VS0 = VS1 = VS2 = VB0 = 0, TA = 0°C to +85°C, unless otherwise specified.)

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functionaloperation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure toabsolute maximum rating conditions for extended periods may affect device reliability.

V+ to GND..............................................................-0.3V to +30VVCC to GND..............................................................-0.3V to +6VVDD to PGND............................................................-0.3V to +6VPSI, SUS, IMVPOK, CLKEN, DPSLP,

SYSOK, D0–D5 to GND........................................-0.3V to +6VILIM, FB, POS, NEG, CCV, CCI, REF, OAIN+,

OAIN- to GND.........................................-0.3V to (VCC + 0.3V)CMP, CSP, CMN, CSN to GND ..................-0.3V to (VCC + 0.3V)DDO, TON, TIME, B0, B1, B2,

S0, S1, S2 to GND..................................-0.3V to (VCC + 0.3V)SHDN to GND (Note 1)...........................................-0.3V to +18VDLM, DLS to PGND....................................-0.3V to (VDD + 0.3V)BSTM, BSTS to GND ..............................................-0.3V to +36V

DHM to LXM ...........................................-0.3V to (VBSTM + 0.3V)LXM to BSTM............................................................-6V to +0.3VDHS to LXS..............................................-0.3V to (VBSTS + 0.3V)LXS to BSTS .............................................................-6V to +0.3VGND to PGND .......................................................-0.3V to +0.3VREF Short-Circuit Duration (TA = +70°C)...................ContinuousContinuous Power Dissipation

48-Pin QFN (derate 26.3mW/°C above +70°C) ...........2.105WOperating Temperature Range ...........................-40°C to +85°CJunction Temperature ......................................................+150°CStorage Temperature Range .............................-65°C to +150°CLead Temperature (soldering, 10s) .................................+300°C

Note 1: SHDN may be forced to 12V, for the purpose of debugging prototype boards using the no-fault test mode, which disablesfault protection and disables overlapping operation.

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

PWM CONTROLLER

Battery voltage, V+ 2 28Input-Voltage Range

VCC, VDD 4.5 5.5V

DAC codes from1.276V to 1.708V

-0.75 +0.75

DAC codes from0.844V to 1.260V

-1.25 +1.25DC Output-Voltage Accuracy(Note 2)

V+ = 4.5V to 28V,includes loadregulation error

DAC codes from0.492V to 0.828V

-3.00 +3.00

%

Line Regulation Error VCC = 4.5V to 5.5V, V+ = 4.5V to 28V 5 mV

IFB FB -2 +2Input Bias Current

IPOS, INEG POS, NEG -0.2 +0.2µA

POS, NEG Common-Mode Range DPSLP = GND 0 2 V

POS, NEG Differential Range VPOS - VNEG , DPSLP = GND -200 +200 mV

POS, NEG Offset Gain AOS∆VFB/(VPOS - VNEG),(VPOS - VNEG) = 100mV, DPSLP = GND

0.95 1.00 1.05 mV/mV

POS, NEG Enable Time tOS

Measured from the time DPSLP goes low tothe time in which POS, NEG affect a changein the set point (VDAC)

0.1 µs

640kHz nominal, RTIME = 23.5kΩ 580 640 700

320kHz nominal, RTIME = 47kΩ 295 320 345TIME Frequency Accuracy fTIME

64kHz nominal, RTIME = 235kΩ 58 64 70

kHz

CONFIDENTIAL INFORMATION—RESTRICTED TO INTEL IMVP LICENSEES

PRELIMINARY MA

X1

98

7/M

AX

19

88

Dual-Phase, Quick-PWM Controllers for IMVP-IVCPU Core Power Supplies

_______________________________________________________________________________________ 3

ELECTRICAL CHARACTERISTICS (continued)(Circuit of Figure1, V+ = 15V, VCC = VDD = VSHDN = VTON = VDPSLP = VPSI = VB1 = VOAIN- = 5V, VB2 = 2V, VFB = VCMP = VCMN =VCSP = VCSN = VOAIN+ = VNEG = VPOS = 1.26V, VD4 = VD3 = VD2 = 1.0V, VSUS = VD5 = VD1 = VD0 = VS0 = VS1 = VS2 = VB0 = 0, TA = 0°C to +85°C, unless otherwise specified.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

TON = REF(550kHz)

155 180 205

TON = open(300kHz)

320 355 390On-Time (Note 3) tONV+ = 12V,VFB = VCCI = 1.2V

TON = VCC(200kHz)

475 525 575

ns

TON = REF (550kHz) 330 375Minimum Off-Time (Note 3) tOFF(MIN)

TON = VCC or open (200kHz or 300kHz) 435 500ns

DDO Delay Time tDDO

Measured from the time FB reaches thevoltage set by S0 to S2. Clock speed set byRTIME.

32 clks

SKIP Delay Time tSKIP

Measured from the time when DDO isasserted to the time in which the controllerbegins pulse-skipping operation

30 clks

BIAS AND REFERENCE

Quiescent Supply Current (VCC) ICCMeasured at VCC, FB forced above theregulation point

1.70 2.70 mA

Quiescent Supply Current (VDD) IDDMeasured at VDD, FB forced above theregulation point

<1 5 µA

Quiescent Battery SupplyCurrent (V+)

IV+ Measured at V+ 25 50 µA

Shutdown Supply Current (VCC) Measured at VCC, SHDN = GND 2 5 µA

Shutdown Supply Current (VDD) Measured at VDD, SHDN = GND <1 5 µA

Shutdown Battery SupplyCurrent (V+)

Measured at V+, SHDN = GND,VCC = VDD = 0 or 5V

<1 5 µA

Reference Voltage VREF VCC = 4.5V to 5.5V, IREF = 0 1.990 2.000 2.010 V

Reference Load Regulation ∆VREF IREF = -10µA to +100µA -10 +10 mV

FAULT PROTECTION

Output Overvoltage ProtectionThreshold (MAX1987 Only)

VOVP Measured at FB 1.95 2.00 2.05 V

Output Overvoltage PropagationDelay (MAX1987 Only)

tOVP FB forced above 2.05V 10 µs

Output Undervoltage ProtectionThreshold

VUVLOMeasured at FB with respect to unloadedoutput voltage

67 70 73 %

Output Undervoltage PropagationDelay

tUVP FB forced 2% below trip threshold 10 µs

CONFIDENTIAL INFORMATION—RESTRICTED TO INTEL IMVP LICENSEES

PRELIMINARY

MA

X1

98

7/M

AX

19

88

Dual-Phase, Quick-PWM Controllers for IMVP-IVCPU Core Power Supplies

4 _______________________________________________________________________________________

ELECTRICAL CHARACTERISTICS (continued)(Circuit of Figure1, V+ = 15V, VCC = VDD = VSHDN = VTON = VDPSLP = VPSI = VB1 = VOAIN- = 5V, VB2 = 2V, VFB = VCMP = VCMN =VCSP = VCSN = VOAIN+ = VNEG = VPOS = 1.26V, VD4 = VD3 = VD2 = 1.0V, VSUS = VD5 = VD1 = VD0 = VS0 = VS1 = VS2 = VB0 = 0, TA = 0°C to +85°C, unless otherwise specified.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Lower threshold(undervoltage)

-13 -10 -7

IMVPOK, CLKEN Threshold

VSYSPOK = 5V;measured at FB withrespect to unloadedoutput voltage

Upper threshold(overvoltage)

+7 +10 +13

%

CLKEN Delay tCLKENFB in regulation, measured from the risingedge of SYSPOK

30 50 90 µs

Output Fault, IMVPOK, andCLKEN Transition Blanking Time

tBLANK

Measured from the time when FB reachesthe voltage set by the DAC code, clockspeed set by RTIME (Note 4)

32 clks

IMVPOK Delay tIMVPOKFB in regulation, measured from the fallingedge of CLKEN

3 5 7 ms

IMVPOK, CLKEN Output LowVoltage

ISINK = 3mA 0.3 V

IMVPOK, CLKEN LeakageCurrent

High state, IMVPOK, CLKEN forced to 5.5V 1 µA

VCC Undervoltage LockoutThreshold

VUVLO

(VCC)

Rising edge, hysteresis = 90mV, PWMdisabled below this level

4.0 4.2 4.4 V

Thermal Shutdown Threshold TSHDN Hysteresis = 15°C 160 °C

CURRENT LIMIT AND BALANCE

Current-Limit Threshold Voltage(Positive, Default)

VLIMIT CMP - CMN, CSP - CSN; ILIM = VCC 27 30 33 mV

VILIM = 1V 47 50 53Current-Limit Threshold Voltage(Positive, Adjustable)

VLIMITCMP - CMN,CSP - CSN VILIM = 1.5V 72 75 78

mV

Current-Limit Threshold Voltage(Negative)

VLIMIT(NEG)

CMP - CMN, CSP - CSN; ILIM = VCC,SUS = GND, and DPSLP = PSI = VCC

-30 -36 -42 mV

Current-Limit Threshold Voltage(Zero-Crossing)

VZEROCMP - CMN, CSP - CSN; SUS = VCC orDPSLP = GND or PSI = GND

1.5 mV

CMP, CMN, CSP,CSN Input Ranges

0 2 V

CMP, CMN, CSP,CSN Input Current

VCSP = VCSN = 0 to 5V -2 +2 µA

ILIM Input Current IILIM VILIM = 0 to 5V 0.1 200 nA

Current-Limit Default SwitchoverThreshold

ILIM 3VCC -

1VCC -0.4

V

Current-Balance Offset VOS(IBAL)

(VCMP - VCMN) - (VCSP - VCSN);ICCI = 0, -20mV < (VCMP - VCMN) <+20mV,0.5V < VCCI < 2.8V

-2.0 +2.0 mV

CONFIDENTIAL INFORMATION—RESTRICTED TO INTEL IMVP LICENSEES

PRELIMINARY MA

X1

98

7/M

AX

19

88

Dual-Phase, Quick-PWM Controllers for IMVP-IVCPU Core Power Supplies

_______________________________________________________________________________________ 5

ELECTRICAL CHARACTERISTICS (continued)(Circuit of Figure1, V+ = 15V, VCC = VDD = VSHDN = VTON = VDPSLP = VPSI = VB1 = VOAIN- = 5V, VB2 = 2V, VFB = VCMP = VCMN =VCSP = VCSN = VOAIN+ = VNEG = VPOS = 1.26V, VD4 = VD3 = VD2 = 1.0V, VSUS = VD5 = VD1 = VD0 = VS0 = VS1 = VS2 = VB0 = 0, TA = 0°C to +85°C, unless otherwise specified.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Current-BalanceTransconductance

gM(IBAL) 400 µS

GATE DRIVERS

DH_ Gate-Driver On-Resistance RON(DH) BST_ - LX_ forced to 5V 1.0 4.5 ΩHigh state (pullup) 1.0 4.5

DL_ Gate-Driver On-Resistance RON(DL)Low state (pulldown) 0.4 2.0

Ω

DH_ Gate-Driver Source/SinkCurrent

IDHDH_ forced to 2.5V,BST_ - LX_ forced to 5V

1.6 A

DL_ Gate-Driver Sink Current IDL(SINK) DL_ forced to 5V 4 A

DL_ Gate-Driver Source Current ID L( S OU RC E ) DL_ forced to 2.5V 1.6 A

DL_ rising 35Dead Time tDEAD

DH_ rising 26ns

VOLTAGE-POSITIONING AMPLIFIER

Input Offset Voltage VOS -1.5 +1.5 mV

Input Bias Current IBIAS OAIN+, OAIN- 0.1 200 nA

Op Amp Disable Threshold OAIN- 3VCC -

1VCC -0.4

V

Common-Mode Input-VoltageRange

VCM Guaranteed by CMRR test 0 2.5 V

Common-Mode Rejection Ratio CMRR VOAIN+ = VOAIN- = 0 to 2.5V 70 100 dB

Power-Supply Rejection Ratio PSRR VCC = 4.5V to 5.5V 75 100 dB

Large-Signal Voltage Gain AOA RL = 1kΩ to VCC/2 70 112 dB

VCC - VFBH 77 300Output-Voltage Swing

(VOAIN+ - VOAIN-) ≥ 10mV,RL = 1kΩ to VCC/2

VFBL 47 200mV

Input Capacitance 11 pF

Gain-Bandwidth Product 3 MHz

Slew Rate 0.3 V/µs

Capacitive Load Stability No sustained oscillations 400 pF

LOGIC AND I/O

Logic-Input High Voltage VIH SUS, DPSLP, SHDN, SYSPOK 2.4 V

Logic-Input Low Voltage VIL SUS, DPSLP, SHDN, SYSPOK 0.8 V

Logic-Input Current SUS, DPSLP, SHDN, SYSPOK -1 +1 µA

CONFIDENTIAL INFORMATION—RESTRICTED TO INTEL IMVP LICENSEES

PRELIMINARY

MA

X1

98

7/M

AX

19

88

Dual-Phase, Quick-PWM Controllers for IMVP-IVCPU Core Power Supplies

6 _______________________________________________________________________________________

ELECTRICAL CHARACTERISTICS (continued)(Circuit of Figure1, V+ = 15V, VCC = VDD = VSHDN = VTON = VDPSLP = VPSI = VB1 = VOAIN- = 5V, VB2 = 2V, VFB = VCMP = VCMN =VCSP = VCSN = VOAIN+ = VNEG = VPOS = 1.26V, VD4 = VD3 = VD2 = 1.0V, VSUS = VD5 = VD1 = VD0 = VS0 = VS1 = VS2 = VB0 = 0, TA = 0°C to +85°C, unless otherwise specified.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

SHDN No-Fault Threshold To enable no-fault mode 12 15 V

1V Logic-Input High Voltage D0–D5, PSI 0.7 V

1V Logic-Input Low Voltage D0–D5, PSI 0.3 V

DAC Input Current D0–D5, PSI -1 +1 µA

Driver Disable Output HighVoltage

DDO, ILOAD = 1mA 2.4 V

Driver Disable Output LowVoltage

DDO, ILOAD = 1mA 0.3 V

High VCC - 0.4

Open 3.15 3.85

REF 1.65 2.35Four-Level Input Logic Levels

TON, S0 to S2,B0 to B2

Low 0.5

V

Four-Level Input CurrentTON, S0 to S2, B0 to B2 forced toGND or VCC

-4 +4 µA

ELECTRICAL CHARACTERISTICS(Circuit of Figure 1, V+ = 15V, VCC = VDD = VSHDN = VTON = VDPSLP = VPSI = VB1 = VOAIN- = 5V, VB2 = 2V, VFB = VCMP = VCMN =VCSP = VCSN = VOAIN+ = VNEG = VPOS = 1.26V, VD4 = VD3 = VD2 = 1.0V, VSUS = VD5 = VD1 = VD0 = VS0 = VS1 = VS2 = VB0 = 0, TA = -40°C to +100°C, unless otherwise specified.) (Note 5)

PARAMETER SYMBOL CONDITIONS MIN MAX UNITS

PWM CONTROLLER

Battery voltage, V+ 2 28Input-Voltage Range

VCC, VDD 4.5 5.5V

DAC codes from1.276V to 1.708V

-1.00 +1.00

DAC codes from0.844V to 1.260V

-1.50 +1.50DC Output-Voltage Accuracy(Note 2)

V+ = 4.5V to 28V,includes loadregulation error

DAC codes from0.492V to 0.828V

-3.5 +3.5

%

POS, NEG Offset Gain AOFF∆VFB/(VPOS - VNEG),(VPOS - VNEG) = 100mV, DPSLP = GND

0.95 1.05 mV/mV

640kHz nominal, RTIME = 23.5kΩ 580 700

320kHz nominal, RTIME = 47kΩ 295 345TIME Frequency Accuracy fTIME

64kHz nominal, RTIME = 235kΩ 58 70

kHz

TON = REF (550kHz) 155 205

TON = open (300kHz) 320 390On-Time (Note 3) tONV+ = 12V,VFB = VCCI = 1.2V

TON = VCC (200kHz) 475 575

ns

CONFIDENTIAL INFORMATION—RESTRICTED TO INTEL IMVP LICENSEES

PRELIMINARY MA

X1

98

7/M

AX

19

88

Dual-Phase, Quick-PWM Controllers for IMVP-IVCPU Core Power Supplies

_______________________________________________________________________________________ 7

ELECTRICAL CHARACTERISTICS (continued)(Circuit of Figure 1, V+ = 15V, VCC = VDD = VSHDN = VTON = VDPSLP = VPSI = VB1 = VOAIN- = 5V, VB2 = 2V, VFB = VCMP = VCMN =VCSP = VCSN = VOAIN+ = VNEG = VPOS = 1.26V, VD4 = VD3 = VD2 = 1.0V, VSUS = VD5 = VD1 = VD0 = VS0 = VS1 = VS2 = VB0 = 0, TA = -40°C to +100°C, unless otherwise specified.) (Note 5)

PARAMETER SYMBOL CONDITIONS MIN MAX UNITS

TON = REF (550kHz) 375Minimum Off-Time(Note 3)

tOFF(MIN) TON = VCC or open(200kHz or 300kHz)

500ns

BIAS AND REFERENCE

Quiescent Supply Current (VCC) ICCMeasured at VCC, FB forced above theregulation point

3.00 mA

Quiescent Supply Current (VDD) IDDMeasured at VDD, FB forced above theregulation point

30 µA

Quiescent Battery SupplyCurrent (V+)

IV+ Measured at V+ 50 µA

Shutdown Supply Current (VCC) Measured at VCC, SHDN = GND 20 µA

Shutdown Supply Current (VDD) Measured at VDD, SHDN = GND 20 µA

Shutdown Battery SupplyCurrent (V+)

Measured at V+, SHDN = GND,VCC = VDD = 0 or 5V

20 µA

Reference Voltage VREF VCC = 4.5V to 5.5V, IREF = 0 1.985 2.015 V

FAULT PROTECTION

Output Overvoltage ProtectionThreshold (MAX1987 Only)

Measured at FB 1.95 2.05 V

Output Undervoltage ProtectionThreshold

Measured at FB with respect to unloadedoutput voltage

67 73 %

Lower threshold(undervoltage)

-13 -7

IMVPOK, CLKEN Threshold

VSYSPOK = 5V;measured at FB withrespect to unloadedoutput voltage

Upper threshold(overvoltage)

7 13

%

CLKEN Delay tCLKENFB in regulation, measured from the risingedge of SYSPOK

30 µs

IMVPOK Delay tIMVPOKFB in regulation, measured from the fallingedge of CLKEN

3 ms

VCC Undervoltage LockoutThreshold

VUVLO

(VCC)

Rising edge, hysteresis = 90mV, PWMdisabled below this level

3.95 4.45 V

CURRENT LIMIT AND BALANCE

Current-Limit Threshold Voltage(Positive, Default)

VLIMIT CMP - CMN, CSP - CSN; ILIM = VCC 25 35 mV

VILIM = 1V 45 55Current-Limit Threshold Voltage(Positive, Adjustable)

VLIMITCMP - CMN,CSP - CSN VILIM = 1.5V 70 80

mV

CONFIDENTIAL INFORMATION—RESTRICTED TO INTEL IMVP LICENSEES

PRELIMINARY

MA

X1

98

7/M

AX

19

88

Dual-Phase, Quick-PWM Controllers for IMVP-IVCPU Core Power Supplies

8 _______________________________________________________________________________________

ELECTRICAL CHARACTERISTICS (continued)(Circuit of Figure 1, V+ = 15V, VCC = VDD = VSHDN = VTON = VDPSLP = VPSI = VB1 = VOAIN- = 5V, VB2 = 2V, VFB = VCMP = VCMN =VCSP = VCSN = VOAIN+ = VNEG = VPOS = 1.26V, VD4 = VD3 = VD2 = 1.0V, VSUS = VD5 = VD1 = VD0 = VS0 = VS1 = VS2 = VB0 = 0, TA = -40°C to +100°C, unless otherwise specified.) (Note 5)

PARAMETER SYMBOL CONDITIONS MIN MAX UNITS

Current-Limit Threshold Voltage(Negative)

VLIMIT

(NEG)

CMP - CMN, CSP - CSN; ILIM = VCC,SUS = GND and DPSLP = VCC

-27 -45 mV

Current-Balance Offset VOS(IBAL)

(VCMP - VCMN) - (VCSP - VCSN); ICCI = 0,-20mV < (VCMP - VCMN) < 20mV,0.5V < VCCI < 2.8V

-3 +3 mV

GATE DRIVERS

DH_Gate-Driver On-Resistance R ON(DH) BST_ - LX_forced to 5V 4.5 ΩHigh state (pullup) 4.5

DL_Gate-Driver On-Resistance R ON(DL)Low state (pulldown) 2.0

Ω

VOLTAGE-POSITIONING AMPLIFIER

Input Offset Voltage VOS -2.5 +2.5 mV

Common-Mode InputVoltage Range

VCM Guaranteed by CMRR test 0 2.5 V

VCC - VFBH 300Output-Voltage Swing

(VOAIN+ - VOAIN-) ≥ 10mV,RL = 1kΩ to VCC/2 VFBL 200

mV

LOGIC AND I/O

Logic-Input High Voltage VIH SUS, DPSLP, SHDN, SYSPOK 2.4 V

Logic-Input Low Voltage VIL SUS, DPSLP, SHDN, SYSPOK 0.8 V

1V Logic-Input High Voltage D0–D5, PSI 0.7 V

1V Logic-Input Low Voltage D0–D5, PSI 0.3 V

High VCC - 0.4

Open 3.15 3.85

REF 1.65 2.35Four-Level Input Logic Levels

TON, S0 to S2,B0 to B2

Low 0.5

V

Note 2: DC output accuracy specifications refer to the trip level of the error amplifier. The output voltage has a DC regulation higherthan the trip level by 50% of the output ripple. When pulse-skipping, the output rises by approximately 1.5% when transition-ing from continuous conduction to no load.

Note 3: On-time and minimum off-time specifications are measured from 50% to 50% at the DHM and DHS pins, with LX_ forced toGND, BST_ forced to 5V, and a 500pF capacitor from DH_ to LX_ to simulate external MOSFET gate capacitance. Actual in-circuit times can be different due to MOSFET switching speeds.

Note 4: The output fault-blanking time is measured from the time when FB reaches the regulation voltage set by the DAC code.During power-up, the regulation voltage is set by the boot DAC code (B0 to B2). During normal operation (SUS = GND), theregulation voltage is set by the VID DAC inputs (D0–D5). During suspend mode (SUS = VCC), the regulation voltage is setby the suspend DAC inputs (S0 to S2).

Note 5: Specifications to TA = -40°C to +100°C are guaranteed by design and are not production tested.

CONFIDENTIAL INFORMATION—RESTRICTED TO INTEL IMVP LICENSEES

PRELIMINARY

MA

X1

98

7/M

AX

19

88

Dual-Phase, Quick-PWM Controllers for IMVP-IVCPU Core Power Supplies

_______________________________________________________________________________________ 9

OUTPUT VOLTAGE vs. LOAD CURRENT(VOUT = 1.356V)

MAX

1987

/88

toc0

1

LOAD CURRENT (A)

OUTP

UT V

OLTA

GE (V

)

302010

1.20

1.25

1.30

1.35

1.40

1.150 40

EFFICIENCY vs. LOAD CURRENT(VOUT = 1.356V)

MAX

1987

/88

toc0

2

LOAD CURRENT (A)

EFFI

CIEN

CY (%

)

101

60

70

80

90

100

500.1 100

VIN = 12V

VIN = 8V

VIN = 20V

PSI = GNDPSI = VCC

OUTPUT VOLTAGE vs. LOAD CURRENT(VOUT = 0.844V)

MAX

1987

/88

toc0

3

LOAD CURRENT (A)

OUTP

UT V

OLTA

GE (V

)

252015105

0.75

0.78

0.80

0.83

0.85

0.88

0.730 30

EFFICIENCY vs. LOAD CURRENT(VOUT = 0.844V)

MAX

1987

/88

toc0

4

LOAD CURRENT (A)

EFFI

CIEN

CY (%

)

101

60

70

80

90

100

500.1 100

VIN = 12V

VIN = 8V

VIN = 20V

PSI = GNDPSI = VCC

OUTPUT VOLTAGE vs. LOAD CURRENT(VOUT = 0.748V)

MAX

1987

/88

toc0

5

LOAD CURRENT (A)

OUTP

UT V

OLTA

GE (V

)

15105

0.68

0.69

0.70

0.71

0.72

0.73

0.74

0.75

0.76

0.77

0.670 20

SUS = VCC

EFFICIENCY vs. LOAD CURRENT(VOUT = 0.748V)

MAX

1987

/88

toc0

6

LOAD CURRENT (A)

EFFI

CIEN

CY (%

)

101

60

70

80

90

100

500.1 100

VIN = 12V

VIN = 8V

VIN = 20V

PSI = GNDPSI = VCC

-5

-2

-3

-4

0

-1

4

3

2

1

5

-40 -20 0 20 40 60 80 100

REFERENCE VOLTAGE SHIFTvs. TEMPERATURE

MAX

1987

/88

toc0

7

TEMPERATURE (°C)

∆VRE

F (m

V)

SWITCHING FREQUENCYvs. LOAD CURRENT

MAX

1987

/88

toc0

8

LOAD CURRENT (A)

SWIT

CHIN

G FR

EQUE

NCY

(kHz

)

302010

100

200

300

400

00 40

FORCED-PWM (VPSI = 5V)

SKIP MODE (VPSI = 0)

220

240

280

260

300

320

0 105 15 20 25 30

SWITCHING FREQUENCYvs. INPUT VOLTAGE

MAX

1987

/88

toc0

9

INPUT VOLTAGE (V)

FREQ

UENC

Y (k

Hz)

IOUT = 20A

NO LOAD

Typical Operating Characteristics(Circuit of Figure 1, V+ = 12V, VCC = VDD = 5V, SUS = GND, SHDN = DPSLP = PSI = VCC, B0 to B2 set for 1.372V, S0 to S2 set for0.748V, TA = +25°C, unless otherwise specified.)

CONFIDENTIAL INFORMATION—RESTRICTED TO INTEL IMVP LICENSEES

PRELIMINARY

MA

X1

98

7/M

AX

19

88

Dual-Phase, Quick-PWM Controllers for IMVP-IVCPU Core Power Supplies

10 ______________________________________________________________________________________

OUTPUT OFFSET VOLTAGE vs.POS-NEG DIFFERENTIAL VOLTAGE

MAX

1987

/88

toc1

4

POS-NEG DIFFERENTIAL VOLTAGE (mV)

OUTP

UT O

FFSE

T VO

LTAG

E (m

V)

4002000-200-400

-400

-200

0

200

400

600

-600-600 600

60

-400.1 10 100 10001 10,000

VOLTAGE-POSITIONING AMPLIFIERGAIN AND PHASE vs. FREQUENCY

-20

-10

0

-30

MAX1987/88 toc18

FREQUENCY (kHz)

GAIN

(dB)

PHAS

E (D

EGRE

ES)

10

20

30

40

50

180

-180

-108

-72

-36

-144

0

36

72

108

144

GAIN

PHASE

Typical Operating Characteristics (continued)(Circuit of Figure 1, V+ = 12V, VCC = VDD = 5V, SUS = GND, SHDN = DPSLP = PSI = VCC, B0 to B2 set for 1.372V, S0 to S2 set for0.748V, TA = +25°C, unless otherwise specified.)

200

240

220

280

260

320

300

340

-40 0 20-20 40 60 80 100

SWITCHING FREQUENCYvs. TEMPERATURE

MAX

1987

/88

toc1

0

TEMPERATURE (°C)

FREQ

UENC

Y (k

Hz)

NO LOAD

20A NO LOAD

VOUT = 1.356V35

36

38

37

39

40

-40 0-20 20 40 60 80 100

OUTPUT CURRENT AT CURRENT LIMITvs. TEMPERATURE

MAX

1987

/88

toc1

1

TEMPERATURE (°C)

MAX

IMUM

LOA

D CU

RREN

T (A

)

0

20

60

40

80

100

0 105 15 20 25 30

NO LOAD SUPPLY CURRENTvs. INPUT VOLTAGE

(FORCED-PWM MODE)

MAX

1987

/88

toc1

2

INPUT VOLTAGE (V)

SUPP

LY C

URRE

NT (m

A)

ICC + IDD

I+

PSI = VCC

0

0.5

1.5

1.0

2.0

2.5

0 105 15 20 25 30

NO LOAD SUPPLY CURRENTvs. INPUT VOLTAGE(PULSE SKIPPING)

MAX

1987

/88

toc1

3

INPUT VOLTAGE (V)

SUPP

LY C

URRE

NT (m

A)

ICC + IDD

I+

PSI = GND

0

10

20

30

40

50

0.834 0.839 0.844 0.849 0.854

0.844V OUTPUT-VOLTAGE DISTRIBUTION

MAX

1987

/88

toc1

5

OUTPUT VOLTAGE (V)

SAM

PLE

PERC

ENTA

GE (%

)

0

5

15

10

20

25

1.995 1.9991.997 2.001 2.003 2.005

REFERENCE VOLTAGE DISTRIBUTION

MAX

1987

/88

toc1

6

REFERENCE VOLTAGE (V)

SAM

PLE

PERC

ENTA

GE (%

)

0

10

5

20

15

25

30

0.98 1.000.99 1.01 1.02

POS-NEG OFFSET GAINDISTRIBUTION

MAX

1987

/88

toc1

7

POS-NEG OFFSET GAIN

SAM

PE P

ERCE

NTAG

E (%

)

CONFIDENTIAL INFORMATION—RESTRICTED TO INTEL IMVP LICENSEES

PRELIMINARY

MA

X1

98

7/M

AX

19

88

Dual-Phase, Quick-PWM Controllers for IMVP-IVCPU Core Power Supplies

______________________________________________________________________________________ 11

VPS AMPLIFIER OFFSET VOLTAGEvs. COMMON-MODE VOLTAGE

MAX

1987

/88

toc1

9

COMMON-MODE VOLTAGE (V)

OFFS

ET V

OLTA

GE (µ

V)

4321

20

40

60

80

100

120

140

160

180

00 5

VPS AMPLIFIERDISABLED

POWER-UP SEQUENCEMAX1987/88 toc21

100µs/div

0A

B

C

D

5V

0

5V

0

0

5V

BOOT

VID

A. VSHDN = 0 TO 5V, 5V/divB. VOUT = 0 TO 1.372V TO 0.844V, 500mV/divC. CLKEN, 5V/divD. DDO, 5V/div RLOAD = 80mΩ

SOFT-STARTMAX1987/88 toc22

100µs/div

0A

B

C

D

5V

0

10A

0

0

BOOT

VID

A. VSHDN = 0 TO 5V, 5V/divB. VOUT = 0 TO 1.372V TO 0.844V, 500mV/divC. ILM, 10A/divD. ILS, 10A/div RLOAD = 80mΩ

SYSTEM POWER-OKMAX1987/88 toc23

20µs/div

0

A

B

C

D

5V

0

5V

BOOT(1.372V)

HIGH FREQ VID(1.356V)

LOW FREQ VID(0.844V)

A. VSYSPOK = 0 TO 5V, 5V/divB. HIGH FREQ: VOUT = 1.356V, 200mV/divC. LOW FREQ: VOUT = 0.844V, 200mV/divD. CLKEN, 5V/div

IMVPOK DELAYMAX1987/88 toc24

1ms/div

0

0

A

B

C

D

5V

0

0

5V

5V

BOOT(1.372V)

A. VSHDN = 0 TO 5V, 5V/divB. VOUT = 0 TO 0.844V, 1V/divC. CLKEN, 5V/divD. IMVPOK, 5V/div

Typical Operating Characteristics (continued)(Circuit of Figure 1, V+ = 12V, VCC = VDD = 5V, SUS = GND, SHDN = DPSLP = PSI = VCC, B0 to B2 set for 1.372V, S0 to S2 set for0.748V, TA = +25°C, unless otherwise specified.)

0

0.2

0.6

0.4

0.8

1.0

INDUCTOR CURRENT DIFFERENCEvs. LOAD CURRENT

MAX

1987

/88

toc2

0

LOAD CURRENT (A)

I L(CS

) - I L

(CM

) (A)

0 2010 30 40

PSI = GNDPSI = VCC

CONFIDENTIAL INFORMATION—RESTRICTED TO INTEL IMVP LICENSEES

PRELIMINARY

MA

X1

98

7/M

AX

19

88

Dual-Phase, Quick-PWM Controllers for IMVP-IVCPU Core Power Supplies

12 ______________________________________________________________________________________

SHUTDOWN SEQUENCEMAX1987/88 toc25

40µs/div

00.84V

0

0

A

B

C

D

E

5V

5V

05V

05V

A. VSHDN = 5V TO 0, 5V/divB. VOUT = 0.844V TO 0, 500mV/divC. CLKEN, 5V/divD. IMVPOK, 5V/divE. DDO, 5V/div RLOAD = 80mΩ

SOFT SHUTDOWNMAX1987/88 toc26

40µs/div

0

0.84V

0

A

B

C

D

5V

0

0

A. VSHDN = 5V TO 0, 5V/divB. VOUT = 0.844V TO 0, 500mV/divC. ILM, 10A/divD. ILS, 10A/div RLOAD = 80mΩ

LOAD TRANSIENT(VOUT = 1.356V)

MAX1987/88 toc27

40µs/div

0

1.356V

A

B

C

D

25A

0

0

A. IOUT = 0 TO 25A, 20A/divB. VOUT = 1.356V TO 1.281V, 50mV/divC. ILM, 10A/divD. ILS, 10A/div

LOAD TRANSIENT(VOUT = 0.844V)

MAX1987/88 toc28

40µs/div

0

0.844V

A

B

C

D

10A

0

0

A. IOUT = 0 TO 10A, 10A/divB. VOUT = 0.844V TO 0.814V, 20mV/divC. ILM, 10A/divD. ILS, 10A/div

ENTERING DEEP-SLEEP MODEMAX1987/88 toc29

20µs/div

0

1.350V

1.318V

A

B

C

D

5V

0

0

A. VDPSLP = 5V TO 0, 5V/divB. VOUT = 1.350V TO 1.318V, 50mV/divC. LXM, 10V/divD. LXS, 10V/div SUS = GND, IOUT = 1A

EXITING DEEP-SLEEP MODEMAX1987/88 toc30

20µs/div

0

1.351V

1.318V

A

B

C

D

5V

0

0

A. VDPSLP = 0 TO 5V, 5V/divB. VOUT = 1.318V TO 1.351V, 50mV/divC. LXM, 10V/divD. LXS, 10V/div SUS = GND, IOUT = 1A

Typical Operating Characteristics (continued)(Circuit of Figure 1, V+ = 12V, VCC = VDD = 5V, SUS = GND, SHDN = DPSLP = PSI = VCC, B0 to B2 set for 1.372V, S0 to S2 set for0.748V, TA = +25°C, unless otherwise specified.)

CONFIDENTIAL INFORMATION—RESTRICTED TO INTEL IMVP LICENSEES

PRELIMINARY

MA

X1

98

7/M

AX

19

88

Dual-Phase, Quick-PWM Controllers for IMVP-IVCPU Core Power Supplies

______________________________________________________________________________________ 13

DEEP-SLEEP TRANSITIONMAX1987/88 toc31

40µs/div

0

1.350V1.318V

A

B

C

D

5V

0

0

A. VDPSLP = 5V TO 0, 5V/divB. VOUT = 1.350V TO 1.318V, 50mV/divC. ILM, 10A/divD. ILS, 10A/div SUS = GND, IOUT = 1A

ENTERING SUSPEND MODEMAX1987/88 toc32

40µs/div

0

0.751V

1.318V

A

B

C

D

5V

0

0

A. VSUS = 0 TO 5V, 5V/divB. VOUT = 1.318V TO 0.751V, 500mV/divC. LXM, 10V/divD. LXS, 10V/div DPSLP = GND, IOUT = 1.0A

EXITING SUSPEND MODEMAX1987/88 toc33

40µs/div

0

0.751V

1.318V

A

B

C

D

5V

0

0

A. VSUS = 5V TO 0, 5V/divB. VOUT = 0.751V TO 1.318V, 500mV/divC. LXM, 10V/divD. LXS, 10V/div DPSLP = GND, IOUT = 1A

SUSPEND TRANSITIONMAX1987/88 toc34

100µs/div

0

0.751V

1.318V

A

B

C

D

5V

0

0

A. VSUS = 0 TO 5V, 5V/divB. VOUT = 1.318V TO 0.751V, 500mV/divC. ILM, 10A/divD. ILS, 10A/div DPSLP = GND, IOUT = 1A

MAX1987/88 toc35

20µs/div

0

1.356V

A

B

C

D

5V

0

0

A. VPSI = 5V TO 0, 5V/divB. VOUT = 1.356V, 50mV/divC. LXM, 10V/divD. LXS, 10V/div IOUT = 1A

PSI TRANSITION

Typical Operating Characteristics (continued)(Circuit of Figure 1, V+ = 12V, VCC = VDD = 5V, SUS = GND, SHDN = DPSLP = PSI = VCC, B0 to B2 set for 1.372V, S0 to S2 set for0.748V, TA = +25°C, unless otherwise specified.)

CONFIDENTIAL INFORMATION—RESTRICTED TO INTEL IMVP LICENSEES

PRELIMINARY

MA

X1

98

7/M

AX

19

88

Dual-Phase, Quick-PWM Controllers for IMVP-IVCPU Core Power Supplies

14 ______________________________________________________________________________________

Pin Description

MAX1987/88 toc37

20µs/div

0

1.356V

1.228V

A

B

C

D

1V

0

0

A. VD3 = 0 TO 1V, 1V/divB. VOUT = 1.356V TO 1.228V, 100mV/divC. ILM, 10A/divD. ILS, 10A/div

DYNAMIC VID TRANSITION(D3 = 128mV)

Typical Operating Characteristics (continued)(Circuit of Figure 1, V+ = 12V, VCC = VDD = 5V, SUS = GND, SHDN = DPSLP = PSI = VCC, B0 to B2 set for 1.372V, S0 to S2 set for0.748V, TA = +25°C, unless otherwise specified.)

MAX1987/88 toc36

20µs/div

0

1.356V

1.340V

A

B

C

D

1V

0

0

A. VD0 = 0 TO 1V, 1V/divB. VOUT = 1.356V TO 1.340V, 20mV/divC. ILM, 10A/divD. ILS, 10A/div

DYNAMIC VID TRANSITION(D0 = 16mV)

PIN NAME FUNCTION

1 TIMESlew-Rate Adjustment Pin. Connect a resistor from TIME to GND to set the internal slew-rate clock. A 235kΩto 23.5kΩ resistor sets the clock from 64kHz to 640kHz, fSLEW = 320kHz × 47kΩ/RTIME.

2 TONOn-Time Selection Control Input. This four-level input sets the K-factor value (Table 3) used to determine theDH on-time (see the On-Time One-Shot section): GND = 1000kHz (untested), REF = 550kHz,open = 300kHz, VCC = 200kHz per phase

3, 4, 5B0, B1,

B2

Boot-Mode Voltage Select Inputs. B0 to B2 are four-level digital inputs that select the boot-mode VID code(Table 6) for the boot-mode multiplexer inputs. During power-up, the boot-mode VID code is delivered to theDAC (see the Internal Multiplexers section).

6, 7, 8S0, S1,

S2

Suspend-Mode Voltage Select Inputs. S0 to S2 are four-level digital inputs that select the suspend-mode VIDcode (Table 5) for the suspend-mode multiplexer inputs. If SUS is high, the suspend-mode VID code isdelivered to the DAC (see the Internal Multiplexers section), overriding any other voltage setting (Figure 9).

9 SHDN

Shutdown Control Input. This input cannot withstand the battery voltage. Connect to VCC for normaloperation. Connect to ground to put the IC into its 1µA shutdown state. During the transition from normaloperation to shutdown, the output voltage is ramped down at the output voltage slew rate programmed bythe TIME pin. In shutdown mode, DLM and DLS are forced to VDD to clamp the output to ground. ForcingSHDN to 12V~15V disables both overvoltage protection and undervoltage protection circuits, disablesoverlap operation, and clears the fault latch. Do not connect SHDN to >15V.

10 REF2V Reference Output. Bypass to GND with a 0.22µF or greater ceramic capacitor. The reference can source100µA for external loads. Loading REF degrades output-voltage accuracy according to the REF loadregulation error.

11 ILIMCurrent-Limit Adjustment. The current-limit threshold defaults to 30mV if ILIM is connected to VCC. Inadjustable mode, the current-limit threshold voltage is precisely 1/20th the voltage seen at ILIM over a200mV to 1.5V range. The logic threshold for switchover to the 30mV default value is approximately VCC - 1V.

CONFIDENTIAL INFORMATION—RESTRICTED TO INTEL IMVP LICENSEES

PRELIMINARY MA

X1

98

7/M

AX

19

88

Dual-Phase, Quick-PWM Controllers for IMVP-IVCPU Core Power Supplies

______________________________________________________________________________________ 15

Pin Description (continued)

PIN NAME FUNCTION

12 VCCAnalog Supply Voltage Input for PWM Core. Connect VCC to the system supply voltage (4.5V to 5.5V) with aseries 10Ω resistor. Bypass to GND with a 1µF or greater ceramic capacitor, as close to the IC as possible.

13 GND Analog Ground. Connect the MAX1987/MAX1988s’ exposed pad to analog ground.

14 CCVVoltage Integrator Capacitor Connection. Connect a 47pF to 1000pF (270pF typ) capacitor from CCV toanalog ground (GND) to set the integration time constant.

15 POSFeedback Offset Adjust Positive Input. The output shifts by 100% (typ) of the differential input voltageappearing between POS and NEG when DPSLP is low. The common-mode range of POS and NEG is 0 to2V. POS and NEG should be generated from resistor-dividers from the output.

16 NEGFeedback Offset Adjust Negative Input. The output shifts by 100% (typ) of differential input voltageappearing between POS and NEG when DPSLP is low. The common-mode range of POS and NEG is 0 to2V. POS and NEG should be generated from resistor-dividers from the output.

17 CCICurrent Balance Compensation. Connect a 470pF capacitor between CCI and FB (see the Current BalanceCompensation section). An additional 470kΩ to 1MΩ resistor between CCI and FB for low-frequencyoperation.

18 FBFeedback Input. FB is internally connected to both the feedback input and the output of the voltage-positioning op amp (Figure 2). Connect a resistor between FB and OAIN- (Figure 1) to set the voltage-positioning gain (see the Setting Voltage Positioning section).

19 OAIN-

Dual-Mode Op Amp Inverting Input and Op Amp Disable Input. When using the internal op amp foradditional voltage-positioning gain (Figure 1), connect to the negative terminal of the current-sense resistorthrough a 1.0kΩ ±1% resistor as described in the Setting Voltage Positioning section. Connect OAIN- to VCCto disable the op amp. The logic threshold to disable the op amp is approximately VCC - 1V.

20 OAIN+Op Amp Noninverting Input. When using the internal op amp for additional voltage-positioning gain(Figure 1), connect to the positive terminal of the current-sense resistor through a resistor as described in theSetting Voltage Positioning section.

21 PSIPower-Status Indicator Input. When PSI is pulled low, the MAX1987/MAX1988 immediately enter pulse-skipping operation, blank the IMVPOK output high, and blank the CLKEN output low.

22 SYSPOK

System Power-Good Input. Primarily, SYSPOK serves as the wired NOR junction of the open-drain power-good signals for the VCCP and VCCMCH supplies. A falling edge on SYSPOK shuts down theMAX1987/MAX1988 and sets the fault latch. Toggle SHDN or cycle VCC power below 1V to restart thecontroller.

23 IMVPOK

Open-Drain Power-Good Output. After output voltage transitions, except during power-up and power-down,if OUT is in regulation, then IMVPOK is high impedance. IMVPOK is high impedance whenever the slew ratecontrol is active (output voltage transitions). IMVPOK is forced low in shutdown. A pullup resistor on IMVPOKcauses additional finite shutdown current. IMVPOK also reflects the state of SYSPOK and includes a 3ms(min) delay for power-up.

24 CLKENClock Enable Logic Output. This inverted logic output indicates when SYSPOK is high and the output voltagesensed at FB is in regulation. CLKEN is forced low during VID transitions.

25–30 D5–D0

Low-Voltage VID DAC Code Inputs. D0 is the LSB, and D5 is the MSB of the internal 6-bit VID DAC (Table 4).The D0–D5 inputs do not have internal pullups. These 1.0V logic inputs are designed to interface directly withthe CPU. In all normal active modes (modes other than suspend mode and boot mode), the output voltage isset by the VID code indicated by the D0–D5 logic-level voltages on D0–D5. In suspend mode (SUS = high),the decoded state of the four-level S0 to S2 inputs sets the output voltage. In boot mode (see the Power-UpSequence section), the decoded state of the four-level B0 to B2 inputs set the output voltage.

CONFIDENTIAL INFORMATION—RESTRICTED TO INTEL IMVP LICENSEES

PRELIMINARY

MA

X1

98

7/M

AX

19

88

Dual-Phase, Quick-PWM Controllers for IMVP-IVCPU Core Power Supplies

16 ______________________________________________________________________________________

Pin Description (continued)

PIN NAME FUNCTION

31 DDO

Driver-Disable Output. This TTL logic output can be used to disable the driver outputs on slave-switchingregulator controllers, such as the MAX1980—forcing a high-impedance condition and making it possible forthe MAX1987/MAX1988 master controller to operate in low-current SKIP mode. DDO goes low 32 RTIMEclock cycles after the MAX1987/MAX1988 complete a transition to the suspend mode or deep-sleep voltage(see the Low-Power Pulse Skipping section). Another 32 clock cycles later, the MAX1987/MAX1988 enterautomatic pulse-skipping operation.

32 BSTMMain Boost Flying Capacitor Connection. An optional resistor in series with BSTM allows the DHM pullupcurrent to be adjusted.

33 LXM Main Inductor Connection. LXM is the internal lower supply rail for the DHM high-side gate driver.

34 DHM Main High-Side Gate-Driver Output Swings LXM to BSTM

35 DLMMain Low-Side Gate Driver Output. DLM swings from PGND to VDD. DLM is forced high after theMAX1987/MAX1988 power down (SHDN = GND) or when the MAX1987 detects an overvoltage fault. TheMAX1988 does not include overvoltage protection.

36 VDDSupply Voltage Input for the DLM and DLS Gate Drivers. Connect to the system supply voltage (4.5V to5.5V). Bypass VDD to PGND with a 2.2µF or greater ceramic capacitor, as close to the IC as possible.

37 PGND Power Ground. Ground connection for the low-side gate drivers DLM and DLS.

38 DLSSecondary Low-Side Gate Driver Output. DLS swings from PGND to VDD. DLS is forced high after theMAX1987/MAX1988 power down (SHDN = GND) or when the MAX1987 detects an overvoltage fault. TheMAX1988 does not include overvoltage protection.

39 DHS Secondary High-Side Gate-Driver Output Swings LXS to BSTS

40 LXS Secondary Inductor Connection. LXS is the internal lower supply rail for the DHS high-side gate driver.

41 BSTSSecondary Boost Flying Capacitor Connection. An optional resistor in series with BSTS allows the DHS pullupcurrent to be adjusted.

42 V+Battery Voltage Sense Connection. Used only for PWM one-shot timing. DH_ on-time is inversely proportionalto input voltage over a range of 2V to 28V.

43 SUS

Suspend-Mode Control Input. When SUS is high, the regulator slews to the suspend voltage level. This levelis set with four-level logic signals at the S0 to S2 inputs. 32 clock cycles after the transition to the suspend-mode voltage is completed, DDO goes low (see the Low-Power Pulse Skipping section). Another 32 clockcycles later, the MAX1987/MAX1988 are allowed to enter pulse-skipping operation.

44 DPSLP

Deep-Sleep Control Input. When DPSLP is low, the system enters the deep-sleep state and the regulatorapplies the appropriate deep-sleep offset. The MAX1987/MAX1988 add the offset measured at the POS andNEG pins to the output. 32 clock cycles after the deep-sleep transition is completed, DDO goes low (see theLow-Power Pulse Skipping section). Another 32 clock cycles later, the MAX1987/MAX1988 are allowed toenter pulse-skipping operation.

45 CMP Main Inductor Positive Current-Sense Input

46 CMN Main Inductor Negative Current-Sense Input

47 CSN Secondary Inductor Negative Current-Sense Input

48 CSP Secondary Inductor Positive Current-Sense Input

CONFIDENTIAL INFORMATION—RESTRICTED TO INTEL IMVP LICENSEES

PRELIMINARY MA

X1

98

7/M

AX

19

88

Dual-Phase, Quick-PWM Controllers for IMVP-IVCPU Core Power Supplies

______________________________________________________________________________________ 17

Table 1. Component Selection for Standard Multiphase Applications (Figure 1)DESIGNATION COMPONENT

Input Voltage Range* 7V to 24V

VID Output Voltage (D5–D0) 1.356V (D5–D0 = 010110)

Boot Voltage (B0 to B2) 1.372V (B2 = REF, B1 = REF, B0 = REF)

Suspend Voltage (S0 to S2) 0.748V (S2 = VCC, S1 = VCC, S0 = GND)

Deep-Sleep Offset Voltage (POS, NEG) 2.7%

Maximum Load Current (typ) 40A

Inductor (LM, LS)0.6µHPanasonic ETQP1H0R6BFA or Sumida CDEP134H-0R6

Switching Frequency 300kHz (TON = float)

High-Side MOSFET (NH, per phase) Fairchild (2) FDS6694 or Siliconix (2) Si4860DY

Low-Side MOSFET (NL, per phase) Fairchild (2) FDS6688 or Siliconix (2) Si4362DY

Input Capacitance (CIN)(6) 10µF, 25VTaiyo Yuden TMK432BJ106KM or TDK C4532X5R1E106M

Output Capacitance (COUT)(3) 470µF, 2.5V Sanyo 2R5TPD470M or(4) 330µF, 2.5V Panasonic EEFUEOD33IXR

Current-Sense Resistor (RSENSE, per phase)1.5mΩPanasonic ERJM1WTJ1M5U

*Input voltages less than 7V require additional input capacitance.

Table 2. Component SuppliersMANUFACTURER PHONE WEBSITE

BI Technologies 714-447-2345 (USA) www.bitechnologies.com

Central Semiconductor 631-435-1110 (USA) www.centralsemi.com

Coilcraft 800-322-2645 (USA) www.coilcraft.com

Coiltronics 561-752-5000 (USA) www.coiltronics.com

Fairchild Semiconductor 888-522-5372 (USA) www.fairchildsemi.com

International Rectifier 310-322-3331 (USA) www.irf.com

Kemet 408-986-0424 (USA) www.kemet.com

Panasonic 847-468-5624 (USA) www.panasonic.com

Sanyo65-281-3226 (Singapore)

408-749-9714 (USA)www.secc.co.jp

Siliconix (Vishay) 203-268-6261 (USA) www.vishay.com

Sumida 408-982-9660 (USA) www.sumida.com

Taiyo Yuden03-3667-3408 (Japan)408-573-4150 (USA)

www.t-yuden.com

TDK847-803-6100 (USA)

81-3-5201-7241 (Japan)www.component.tdk.com

Toko 858-675-8013 (USA) www.tokoam.com

CONFIDENTIAL INFORMATION—RESTRICTED TO INTEL IMVP LICENSEES

MA

X1

98

7/M

AX

19

88

Dual-Phase, Quick-PWM Controllers for IMVP-IVCPU Core Power Supplies

18 ______________________________________________________________________________________

PRELIMINARY

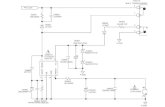

OFF

ON

BSTM

DHM

LXM

DLM

VDDVCC

D0D1

D3D4

FB

DAC INPUTS(1V LOGIC)

REF

CREF0.22µF

CCCV270pF

PGND

V+

CCV

NEG

CCI

S0S1SUSPEND INPUTS

(FOUR-LEVEL LOGIC)

POS

CSP

ILIM

TIME

SUS

PSI

MODECONTROL

C3100pF

RTIME28kΩ

R8100kΩ

POWER GROUND

ANALOG GROUND

GND

D5

S2

B0B1BOOT INPUTS

(FOUR-LEVEL LOGIC)B2

OAIN-

OAIN+

CMN

CMP

IMVPOK

SYSPOK

R12100kΩ

R13100kΩ

R11100kΩ

C21µF

TONFLOAT(300kHz)

POW

ER-G

OOD

LOGI

C SI

GNAL

S

R2750Ω

R31.0kΩ

CCCI470pF

R930.1kΩ

INPUT*8V TO 24V

LM

CIN

NH(M)

NL(M)

RCM

CBST(M)0.1µF

R1010Ω

5V BIASSUPPLY

C12.2µF

DDO

SHDN

DPSLP

CLKEN

MAX1987MAX1988

LS

CIN

NH(S)

NL(S)

RCS

CBST(S)0.1µF

BSTDIODES

R11.5kΩ

R7100kΩ R4

750Ω

R51.0kΩ

R62.74kΩ

CSN

BSTS

DHS

LXS

DLS

RCCI1MΩ

OUTPUT

COUT

COUT

*LOWER INPUT VOLTAGESREQUIRE ADDTIONALINPUT CAPACITANCE

D2

R144.7kΩ

C44.7nF

Figure 1. Standard Application Circuit (Master)

CONFIDENTIAL INFORMATION—RESTRICTED TO INTEL IMVP LICENSEES

Detailed Description5V Bias Supply (VCC and VDD)

The MAX1987/MAX1988 require an external 5V bias sup-ply in addition to the battery. Typically, this 5V bias sup-ply is the notebook’s 95% efficient 5V system supply.Keeping the bias supply external to the IC improves effi-ciency and eliminates the cost associated with the 5V lin-ear regulator that would otherwise be needed to supplythe PWM circuit and gate drivers. If standalone capabilityis needed, the +5V bias supply can be generated withan external linear regulator.

The 5V bias supply must provide VCC (PWM controller)and VDD (gate-drive power), so the maximum currentdrawn is:

IBIAS = ICC + fSW (QG(LOW) + QG(HIGH))

= 10mA to 100mA (typ)

where ICC is 1.7mA (typ), fSW is the switching frequency,and QG(LOW) and QG(HIGH) are the MOSFET data sheet’stotal gate-charge specification limits at VGS = 5V.

V+ and VDD can be connected together if the inputpower source is a fixed 4.5V to 5.5V supply. If the 5Vbias supply is powered up prior to the battery supply,the enable signal (SHDN going from low to high) mustbe delayed until the battery voltage is present to ensurestartup.

Free-Running, Constant On-Time PWMController with Input Feedforward

The Quick-PWM control architecture is a pseudo-fixed-frequency, constant-on-time, current-mode regulatorwith voltage feedforward (Figure 2). This architecturerelies on the output filter capacitor’s ESR to act as thecurrent-sense resistor, so the output ripple voltage pro-vides the PWM ramp signal. The control algorithm issimple: the high-side switch on-time is determined sole-ly by a one-shot whose period is inversely proportionalto input voltage, and directly proportional to output volt-age and the difference between the main and sec-ondary inductor currents (see the On-Time One-Shotsection). Another one-shot sets a minimum off-time. Theon-time one-shot is triggered if the error comparator islow, the low-side switch currents are below the current-limit threshold, and the minimum off-time one-shot hastimed out. The controller maintains 180° out-of-phaseoperation by alternately triggering the main and sec-ondary phases after the error comparator drops belowthe output voltage set point.

On-Time One-Shot (TON)The core of each phase contains a fast, low-jitter,adjustable one-shot that sets the high-side MOSFET’son-time. The one-shot for the main phase simply variesthe on-time in response to the input and feedback volt-ages. The main high-side switch on-time is inverselyproportional to the input voltage as measured by the V+input, and proportional to the feedback voltage (VFB):

where K is set by the TON pin-strap connection (Table3) and 0.075V is an approximation to accommodate theexpected drop across the low-side MOSFET switch.

The one-shot for the secondary phase varies the on-time in response to the input voltage and the differencebetween the main and secondary inductor currents.Two identical transconductance amplifiers integrate thedifference between the master and slave current-sensesignals. The summed output is internally connected toCCI, allowing adjustment of the integration time con-stant with a compensation network connected betweenCCI and FB. The resulting compensation current andvoltage are determined by the following equations:

where ZCCI is the impedance at the CCI output.

The secondary on-time one-shot uses this integratedsignal (VCCI) to set the secondary high-side MOSFETson-time. When the main and secondary current-sensesignals (VCM = VCMP - VCMN and VCS = VCSP - VCSM)become unbalanced, the transconductance amplifiersadjust the secondary on time, which increases ordecreases the secondary inductor current until the cur-rent-sense signals are properly balanced:

This algorithm results in a nearly constant switching fre-quency and balanced inductor currents, despite thelack of a fixed-frequency clock generator. The benefitsof a constant switching frequency are twofold: first, the

t KV V

V

KV V

VK

I Z

V

Main On time Secondary Current

Balance Correction

ON NDCCI

IN

FB

IN

CCI CCI

IN

( ).

.

( ) (

)

20 075

0 075

=+

=+

+

= +−

I g V V g V V

V V I ZCCI M CMP CMN M CSP CSN

CCI FB CCI CCI

== +

− − −( ) ( )

tK V V

VON MAINFB

IN( )

( . )= +0 075

MA

X1

98

7/M

AX

19

88

Dual-Phase, Quick-PWM Controllers for IMVP-IVCPU Core Power Supplies

______________________________________________________________________________________ 19

PRELIMINARYCONFIDENTIAL INFORMATION—RESTRICTED TO INTEL IMVP LICENSEES

MA

X1

98

7/M

AX

19

88 frequency can be selected to avoid noise-sensitive

regions such as the 455kHz IF band; second, theinductor ripple-current operating point remains relative-ly constant, resulting in easy design methodology andpredictable output-voltage ripple. The on-time one-shots have good accuracy at the operating pointsspecified in the Electrical Characteristics (±10% at200kHz and 300kHz, ±12% at 550kHz). On-times atoperating points far removed from the conditions speci-fied in the Electrical Characteristics can vary over awider range. For example, the 550kHz setting typicallyruns about 10% slower with inputs much greater than12V due to the very short on-times required.

On-times translate only roughly to switching frequencies.The on-times guaranteed in the Electrical Characteristicsare influenced by switching delays in the external high-side MOSFET. Resistive losses, including the inductor,both MOSFETs, output capacitor ESR, and PC boardcopper losses in the output and ground tend to raisethe switching frequency at higher output currents. Also,the dead-time effect increases the effective on-time,reducing the switching frequency. It occurs only inPWM mode (SUS = low, DPSLP = low) and duringdynamic output voltage transitions when the inductorcurrent reverses at light or negative load currents. Withreversed inductor current, the inductor’s EMF causesLX to go high earlier than normal, extending the on-timeby a period equal to the DH-rising dead time. For loadsabove the critical conduction point, where the dead-time effect is no longer a factor, the actual switchingfrequency (per phase) is:

where VDROP1 is the sum of the parasitic voltage dropsin the inductor discharge path, including synchronousrectifier, inductor, and PC board resistances; VDROP2 isthe sum of the parasitic voltage drops in the inductorcharge path, including high-side switch, inductor, andPC board resistances; and tON is the on-time as deter-mined above.

Current BalanceWithout active current-balance circuitry, the currentmatching between phases depends on the MOSFETs’on-resistance (RDS(ON)), thermal ballasting, on-/off-timematching, and inductance matching. For example, vari-ation in the low-side MOSFET on-resistance (ignoringthermal effects) results in a current mismatch that isproportional to the on-resistance difference:

Thermal ballasting as the loaded MOSFETs heat upactually improves the current balance. The strongerMOSFET (the phase with the lower RDS(ON)) pulls morecurrent, which heats up the MOSFET more than theother phase, increasing the thereby reducing the currentmismatch. Taking thermal effects into account, the on-resistance of the switching MOSFETs can be determinedby the following equation:

where RTA(25) is the on-resistance at room temperature,IL is the inductor current through the MOSFET, RθJA(°C/W) is the junction-to-ambient thermal resistance ofthe MOSFET package, and ∆RTEMPCO (0.5%/°C) is thetemperature coefficient of the MOSFET. Thermal ballast-ing can typically reduce the current mismatch by asmuch as a third. Unfortunately, mismatches between on-times, off-times, and inductor values increase the worst-case current imbalance making it impossible topassively guarantee accurate current balancing.

The MAX1987/MAX1988 integrate the differencebetween the current-sense voltages and adjusts the on-time of the secondary phase to maintain current bal-ance. The current balance now relies on the accuracyof the current-sense resistors instead of the inaccurate,thermally sensitive on-resistance of the low-side trackingMOSFETs. With active current balancing, the currentmismatch is simply determined by the current-senseresistor values and the offset voltage of the transconduc-tance amplifiers:

where RSENSE = RCM = RCS and VOS(IBAL) is the current-balance offset specification in the ElectricalCharacteristics.

I I IV

ROS BAL LM LSOS IBAL

SENSE( )

( )= =−

RR

R I R RDS ON

TA

TA L JA TEMPCO( )

( )

( )(=

−

25

2521 θ ∆

I I IRRMAIN ND MAINMAIN

ND− −=

22

1

fV V

t V V VSWOUT DROP

ON IN DROP DROP=

+( )+ −

1

1 2( )

Dual-Phase, Quick-PWM Controllers for IMVP-IVCPU Core Power Supplies

20 ______________________________________________________________________________________

PRELIMINARY

TONCONNECTION

FREQUENCYSETTING

(kHz)

K-FACTOR(µs)

MAXK-FACTORERROR (%)

VCC 200 5 ±10

Float 300 3.3 ±10

REF 550 1.8 ±12.5

GND 1000 1.0 ±12.5

Table 3. Approximate K-Factor Errors

CONFIDENTIAL INFORMATION—RESTRICTED TO INTEL IMVP LICENSEES

The worst-case current mismatch occurs immediatelyafter a load transient due to inductor value mismatchesresulting in different dI/dt for the two phases. The time ittakes the current-balance loop to correct the transientimbalance depends on the mismatch between theinductor values and switching frequency.

Dual 180° Out-of-Phase Operation The two phases in the MAX1987/MAX1988 operate 180°out-of-phase to minimize input and output filteringrequirements, reduce electromagnetic interference (EMI),and improve efficiency. This effectively lowers componentcount—reducing cost, board space, and componentpower requirements—making the MAX1987/MAX1988ideal for high-power, cost-sensitive applications.

Typically, switching regulators provide transfer powerusing only one phase instead of dividing the poweramong several phases. In these applications, the inputcapacitors must support high-instantaneous currentrequirements. The high RMS ripple current can lowerefficiency due to I2R power loss associated with theinput capacitor’s effective series resistance (ESR).Therefore, the system typically requires several low-ESR input capacitors in parallel to minimize input volt-age ripple, to reduce ESR-related power losses, and tomeet the necessary RMS ripple-current rating.

With the MAX1987/MAX1988, the controller shares thecurrent between two phases that operate 180° out-of-phase, so the high-side MOSFETs never turn on simulta-neously during normal operation. The instantaneousinput current of either phase is effectively halved, result-ing in reduced input-voltage ripple, ESR power loss, andRMS ripple current (see the Input Capacitor Selectionsection). Therefore, the same performance can beachieved with fewer or less expensive input capacitors.

Transient Overlap OperationWhen a transient occurs, the response time of the con-troller depends on how quickly it can slew the inductorcurrent. Multiphase controllers that remain 180° out-of-phase when a transient occurs actually respond slowerthan an equivalent single-phase controller. In order toprovide fast transient response, the MAX1987/MAX1988 support a phase overlap mode that allowsthe individual phases to operate simultaneously whenheavy load transients are detected, effectively reducingthe response time. After either high-side MOSFET turnsoff, if the output voltage does not exceed the regulationvoltage when the minimum off-time expires, the con-troller simultaneously turns on both high-side MOSFETsduring the next on-time cycle. This maximizes the totalinductor current slew rate. The phases remain over-

lapped until the output voltage exceeds the regulationvoltage after the minimum off-time expires.

After the phase overlap mode ends, the controller automat-ically begins with the opposite phase. For example, if thesecondary phase provided the last on-time pulse beforeoverlap operation began, the controller starts switchingwith the main phase when overlap operation ends.

Integrator Amplifiers/Output Voltage Offsets

Two transconductance amplifiers provide a fine adjust-ment to the output regulation point (Figure 2). Oneamplifier forces the DC average of the feedback volt-age to equal the VID DAC setting. The second amplifieris used to create small positive or negative offsets fromthe VID DAC setting, using the POS and NEG pins.

The feedback amplifier integrates the feedback volt-age, allowing accurate DC output voltage regulationregardless of the output ripple voltage. The feedbackamplifier has the ability to shift the output voltage by±8%. The differential input voltage range is at least±80mV total, including DC offset and AC ripple. Theintegration time constant can be set easily with onecapacitor at the CCV pin. Use a capacitor value of47pF to 1000pF (270pF typ).

The POS/NEG amplifier is used to add small offsets tothe VID DAC setting in deep-sleep mode (DPSLP =low). The offset amplifier is summed directly with thefeedback voltage, making the offset gain independentof the DAC code. This amplifier has the ability to offsetthe output by ±200mV. To create an output offset, biasPOS and NEG to a voltage (typically VOUT or REF) with-in their 0 to 2V common-mode range, and offset themfrom one another with a resistive divider (Figure 1). IfVPOS is higher than VNEG, then the output is shifted inthe positive direction. If VNEG is higher than VPOS, thenthe output is shifted in the negative direction. The out-put offset equals the voltage difference from POS toNEG.

Forced-PWM Operation (Normal Mode)During normal mode, when the CPU is actively running(SUS = low, DPSLP = high, PSI = high), the MAX1987/MAX1988 operate with the low-noise forced-PWM con-trol scheme. Forced-PWM operation disables the zero-crossing comparator, forcing the low-side gate-drivewaveform to constantly be the complement of the high-side gate-drive waveform. The benefit of forced-PWMmode is to keep the switching frequency fairly constant.

Forced-PWM operation comes at a cost: the no-load 5Vbias supply current remains between 10mA to 100mA,depending on the external MOSFETs and switching

MA

X1

98

7/M

AX

19

88

Dual-Phase, Quick-PWM Controllers for IMVP-IVCPU Core Power Supplies

______________________________________________________________________________________ 21

PRELIMINARYCONFIDENTIAL INFORMATION—RESTRICTED TO INTEL IMVP LICENSEES

MA

X1

98

7/M

AX

19

88

Dual-Phase, Quick-PWM Controllers for IMVP-IVCPU Core Power Supplies

22 ______________________________________________________________________________________

MAX1987MAX1988

CSN

CSP

CMP

CMN

VCC

REF

GND

CCV

POS

NEG

FB

OAIN+

OAIN-

TIME

6 BITSBLANK

SKIP

ILIM

19R

R

REF(2.0V)

SHDN

REF

Gm

Gm

DPSLP

R-2RDAC

INTERNAL MULTIPLEXERS, MODECONTROL, AND SLEW-RATE CONTROL

B0 T

O B2

S0 T

O S2

D0–D

5

SUS

SYSP

OK

PSI

DD0

0.9 x REF 1.1 x REF

SYSPOK

CLKEN

IMVPOK

STARTUPDELAY

Q

QT

CMP

CMN

SKIP

FAULT

1.5mV

S

R

Q

R

S

Q

MAIN

MAIN

ON-TIMEONE-SHOT

TRIGQ

ON-TIME

ONE-SHOT

TRIGQ

BSTM

TON

V+

CCI

DHM

LXM

VDD

DLM

PGND

MAIN PHASEDRIVERS

TRIGQ

ONE-SHOT

MINIMUMOFF-TIME

SECONDARY PHASEDRIVERS

FB

Gm

Gm

CMP

CSP

CMN

CSN

BSTS

DHS

LXS

DLS

Figure 2. MAX1987/MAX1988 Functional Diagram

CONFIDENTIAL INFORMATION—RESTRICTED TO INTEL IMVP LICENSEES

frequency. To maintain high efficiency under light-loadconditions, the MAX1987/MAX1988 automatically switchto the low-power pulse-skipping control scheme afterentering suspend or deep-sleep mode.

During output voltage and mode transitions (PSI =high), the MAX1987/MAX1988 use forced-PWM opera-tion to ensure fast, accurate transitions. Since forced-PWM operation disables the zero-crossing comparator,the inductor current reverses under light loads, quicklydischarging the output capacitors. The controller main-tains forced-PWM operation for 32 clock cycles (set byRTIME) after the controller sets the last DAC code valueto guarantee the output voltage settles properly beforeentering pulse-skipping operation.

Low-Power Pulse SkippingDuring deep-sleep mode (DPSLP = low), low-powersuspend (SUS = high), or pulse-skipping override mode(PSI = low), the MAX1987/MAX1988 use an automaticpulse-skipping control scheme, alternately switchingboth phases in order to maintain the current balance.

For deep-sleep mode, when the CPU pulls DPSLP low,the MAX1987/MAX1988 shift the output voltage toincorporate the offset voltage set by the POS and NEGinputs (Figure 3). 32 RTIME clock cycles after DPSLPgoes low, the controller pulls the driver-disable output(DDO) low. An additional 30 RTIME clock cycles later,the MAX1987/MAX1988 enter low-power operation,allowing automatic pulse skipping under light loads.When the CPU drives DPSLP high, the MAX1987/MAX1988 immediately enter forced-PWM operation,force DDO high, and eliminate the output offset, slew-ing the output to the operating voltage set by theD0–D5 inputs. When either DPSLP transition occurs,the MAX1987/MAX1988 force IMVPOK high andCLKEN low for 32 RTIME clock cycles.

When entering suspend mode (SUS driven high), theMAX1987/MAX1988 slew the output down to the sus-pend output voltage set by S0 to S2 inputs (Figure 4).32 RTIME clock cycles after the slew-rate controllerreaches the last DAC code (see the Output VoltageTransition Timing section), the DDO is asserted low.After an additional 30 RTIME clock cycles, theMAX1987/MAX1988 enter low-power operation, allow-ing pulse skipping under light loads. When the CPUpulls SUS low, the MAX1987/MAX1988 immediatelyenter forced-PWM operation, force DDO high, and slewthe output up to the operating voltage set by the D0–D5inputs. When either SUS transit ion occurs, theMAX1987/MAX1988 blank IMVPOK and CLKEN, pre-venting IMVPOK from going low and CLKEN from goinghigh. The blanking remains active until the slew rate

controller has reached the last DAC code and 32 addi-tional RTIME clock pulses have passed.

When PSI is pulled low, the MAX1987/MAX1988 over-ride forced-PWM operation and use the automaticpulse-skipping control scheme regardless of the stateof the SUS and DPSLP control inputs. Once PSI ispulled low, the controller asserts the driver-disable out-put (DDO = low), forces IMVPOK high, and forcesCLKEN low. When PSI is used during mode transitions,the constant IMVPOK and CLKEN blanking allowsindefinite settling times.

In applications with more than two phases, the driver-disable signal is used to force one or more slave regula-tors into a high-impedance state. When the master’sDDO output is driven low, the slave controller with driverdisable (MAX1980) forces its DL(SLAVE) and DH(SLAVE)gate drivers low, effectively disabling the slave con-troller. Disabling the slave controller allows theMAX1987/MAX1988 to enter low-power pulse skippingoperation under low-power conditions, improving light-load efficiency. When DDO is driven high, the slave con-troller (MAX1980) enables the drivers, allowing normalforced-PWM operation. For detailed operation with slavecontrollers, refer to the MAX1980 data sheet.

Automatic Pulse-Skipping SwitchoverIn skip mode (PSI = low, SUS = high, or DPSLP = low),an inherent automatic switchover to PFM takes place atlight loads (Figure 5). This switchover is affected by acomparator that truncates the low-side switch on time atthe inductor current’s zero crossing. The zero-crossingcomparator senses the inductor current across the cur-rent-sense resistors. Once VC_P - VC_N drops below1.5mV (typ), the comparator forces DL_ low (Figure 2).This mechanism causes the threshold between pulse-skipping PFM and nonskipping PWM operation to coin-cide with the boundary between continuous anddiscontinuous inductor-current operation. The PFM/PWMcrossover occurs when the load current of each phase isequal to 1/2 the peak-to-peak ripple current, which is afunction of the inductor value (Figure 6). For a batteryinput range of 7V to 20V, this threshold is relatively con-stant, with only a minor dependence on the input voltagedue to the typically low duty cycles.

The total load current at the PFM/PWM crossoverthreshold (ILOAD(SKIP)) is approximately:

where K is the on-time scale factor (Table 3).

IV K

LV V

VLOAD SKIPOUT IN OUT

IN( ) =

−

MA

X1

98

7/M

AX

19

88

Dual-Phase, Quick-PWM Controllers for IMVP-IVCPU Core Power Supplies

______________________________________________________________________________________ 23

PRELIMINARYCONFIDENTIAL INFORMATION—RESTRICTED TO INTEL IMVP LICENSEES

MA

X1

98

7/M

AX

19

88

Dual-Phase, Quick-PWM Controllers for IMVP-IVCPU Core Power Supplies

24 ______________________________________________________________________________________

VOUT

TIMECLOCK

IMVPOK

LX_

PULSESKIPPING

AUTOMATIC PULSE-SKIPPING

SWITCHOVER

OUTPUT TRANSITIONAND SETTLING

OUTPUT TRANSITIONAND SETTLING

DPSLP

DDO

CLKEN

tDD0 = 32 CLKS tSKIP = 30 CLKS tBLANK = 32 CLKS

IMVPOK AND CLKENBLANKING

IMVPOK AND CLKENBLANKING

VPOS - VNEG OFFSET

Figure 3. MAX1987/MAX1988 Deep Sleep Transition

SUS

VOUT

TIMECLOCK

IMVPOK

LX_

PULSESKIPPING

AUTOMATIC PULSE-SKIPPING

SWITCHOVER

OUTPUT SETTLINGOUTPUTTRANSITION

OUTPUT SETTLINGOUTPUTTRANSITION

OUTPUT SET BY S0 TO S2

OUTPUT SET BY D0–D5

CLKEN

DDO

16mV PER RTIME CYCLE

tBLANK = 32 CLKStSKIP = 30 CLKS tSLEWtSLEW tDD0 = 30 CLKS

IMVPOK AND CLKENBLANKING

IMVPOK AND CLKENBLANKING

Figure 4. MAX1987/MAX1988 Suspend Transition

CONFIDENTIAL INFORMATION—RESTRICTED TO INTEL IMVP LICENSEES

For example, in the standard application circuit thisbecomes:

The switching waveforms can appear noisy and asyn-chronous when light loading activates pulse-skippingoperation, but this is a normal operating condition thatresults in high light-load efficiency. Trade-offs betweenPFM noise and light-load efficiency are made by varyingthe inductor value. Generally, low inductor values pro-duce a broader efficiency vs. load curve, while highervalues result in higher full-load efficiency (assuming thatthe coil resistance remains fixed) and less output volt-age ripple. Penalties for using higher inductor valuesinclude larger physical size and degraded load-tran-sient response, especially at low-input voltage levels.

Current-Limit CircuitThe current-limit circuit employs a unique “valley” cur-rent-sensing algorithm that uses current-sense resistorsfrom CMP to CMN and from CSP to CSN as the current-sensing elements (Figure 1). If the current-sense signalof the selected phase is above the current-limit thresh-old, the PWM controller does not initiate a new cycle(Figure 2) until the inductor current of the selectedphase drops below the valley current-limit threshold.When either phase trips the current limit, both phasesare effectively current limited since the interleaved con-troller does not initiate a cycle with either phase.

Since only the valley current is actively limited, theactual peak current is greater than the current-limitthreshold by an amount equal to the inductor ripplecurrent. Therefore, the exact current-limit characteristicand maximum load capability are a function of the cur-rent-sense resistance, inductor value, and battery volt-age. When combined with the undervoltage protectioncircuit, this current-limit method is effective in almostevery circumstance.

There is also a negative current limit that preventsexcessive reverse inductor currents when VOUT is sink-ing current. The negative current-limit threshold is set toapproximately 120% of the positive current limit, andtherefore tracks the positive current limit when ILIM isadjusted. When a phase drops below the negative cur-rent limit, the controller immediately activates an on-time pulse—DL_ turns off, and DH_ turns on—allowingthe inductor current to remain above the negative cur-rent threshold.

The current-limit threshold is adjusted with an externalresistive voltage-divider at ILIM. The current-limit thresh-old voltage adjustment range is from 10mV to 75mV. Inthe adjustable mode, the current-limit threshold voltageis precisely 1/20th the voltage seen at ILIM. The thresh-old defaults to 30mV when ILIM is connected to VCC.The logic threshold for switchover to the 30mV defaultvalue is approximately VCC - 1V.

Carefully observe the PC board layout guidelines toensure that noise and DC errors do not corrupt the cur-rent-sense signals seen by the current-sense inputs(CMP, CMN, CSP, CSN).

MOSFET Gate Drivers (DH, DL)The DH_ and DL_ drivers are optimized for drivingmoderately sized, high-side and larger, low-side powerMOSFETs. This is consistent with the low duty factorseen in the notebook CPU environment, where a largeVIN - VOUT differential exists. An adaptive dead-timecircuit monitors the DL_ output and prevents the high-side FET from turning on until DL_ is fully off. There must

1 3 3 30 6

12 1 312

6 4. .

..

.V s

HV V

VA

× µµ

=−

MA

X1

98

7/M

AX

19

88

Dual-Phase, Quick-PWM Controllers for IMVP-IVCPU Core Power Supplies

______________________________________________________________________________________ 25

PRELIMINARY

INDU

CTOR

CUR

RENT

ILOAD = IPEAK/2

ON-TIME0 TIME

IPEAKL

VBATT - VOUT∆i∆t

=

Figure 5. Pulse-Skipping/Discontinuous Crossover Point

INDU

CTOR

CUR

RENT

ILIMIT(VALLEY) = ILOAD(MAX) 2 - LIR

2η( )

TIME0

IPEAK

ILOAD

ILIMIT

Figure 6. “Valley” Current-Limit Threshold Point

CONFIDENTIAL INFORMATION—RESTRICTED TO INTEL IMVP LICENSEES

MA

X1

98