Diseño de sistemas digitales.1 Lectura 7: Manejo de interrupciones y excepciones Adapted from: Mary...

-

Upload

berengaria-portales -

Category

Documents

-

view

8 -

download

2

Transcript of Diseño de sistemas digitales.1 Lectura 7: Manejo de interrupciones y excepciones Adapted from: Mary...

Diseño de sistemas digitales.1

Lectura 7: Manejo de interrupciones

y excepciones

Adapted from:

Mary Jane Irwin ( www.cse.psu.edu/~mji )

www.cse.psu.edu/~cg431

[Original from Computer Organization and Design,

Patterson & Hennessy, © 2005, UCB]

Diseño de sistemas digitales.2

Componentes fundamentales de un computador

Procesador

Control

Flujo de datos

Memoria

Dispositivos

Input

Output

Métricas importantes para una sistema entrada/salida (I/O)

Desempeño Compatibilidad Escalabilidad y diversidad Formalidad (protocolo) Costo, tamaño, peso

Diseño de sistemas digitales.3

Dispositivos de entrada/salida Los dispositivos de entrada son muy diversos en:

Comportamiento– Entrada, salida o almacenamiento Partner – Humano o máquina Velocidad de datos– la velocidad pico a la cual los datos

pueden ser transferidas entre un dispositivo E/S y la memoria principal o el procesador

Dispositivo Comportamiento

Partner Data rate (Mb/s)

Teclado entrada Humano 0.0001

Mouse entrada Humano 0.0038

Impresora laser salida Humano 3.2000

Display gráfico salida Humano 800.0000-8000.0000

Red/LAN Entrada o salida

maquina 100.0000-1000.0000

Disco magnético almacenamiento

maquina 240.0000-2560.0000

Rango de 8 órdenes de

magnitud

Diseño de sistemas digitales.4

Comunicación de los dispositivos de E/S y el procesador

Como el procesador maneja los dispositivos de E/S Instrucciones especiales de E/S

- Se deben especificar el dispositivo y el comando Dispositivo de E/S mapeado por memoria

- Partes de las direcciones de la memoria de alto nivel están designadas para cada dispositivo de entrada/salida E/S (I/O)

- La lectura y escritura en dichas posiciones de memoria son interpretadas como comandos por dichos dispositivos de E/S

- Carga/almacenamiento en dichos espacios de memora designados a los dispositivos de E/S es solamente realizada por el Sistema Operativo (OS)

Como se comunica el dispositivo de E/S con el procesador Polling – El procesador periodicamente realiza un chequeo del estatus

del dispositivo de E/S para determinar su necesidad de servicio- El procesador está totalmente en control- Sin embargo realiza todo el

trabajo- Puede gastarse innecesariamente una cantidad considerable de tiempo de

procesador debido a las diferencias de velocidad. Manejo de interrupciones– El dispositivo de E/S realiza una interrupción

al procesador para indicarle su necesidad de atención.

Diseño de sistemas digitales.5

(Ejemplo) E/S en SPIM

Processor

Control

F. datosMemoria

Dispositivos

Rx

Tx

SPIM soporta un dispositivo de E/S mapeado por memoria – una terminal con dos unidades independientes

El receptor lee caracteres desde el teclado El transmisor escribe caracteres en la pantalla

Diseño de sistemas digitales.6

Repaso: Configuración de memoria MIPS (spim)Memory

230

words

0000 0000

f f f f f f f c

UserCode

Reserved

Static data

Mem Map I/O

0040 0000

1000 00001000 8000 ( 1004 0000)

7f f e f f fcStack

Dynamic data

$sp

$gp

PC

Kernel Code & Data 8000 0080

Diseño de sistemas digitales.7

Control de recepción de terminal (entrada) con SPIM

La terminal de entrada es controlada por medio de dos registros de memoria mapeados para el dispositivo. (cada registro se encuentra en una ubicación de memoria especial)

unused

0

ready(read only)

1

interrupt enable

Control de recepción(0xffff0000)

unused

07

Byte recibido(read only)

Dato recibido(0xffff0004)

Diseño de sistemas digitales.8

Control de la terminal de salida con SPIM

La terminal de salida es controlada por dos registros mapeados en la memoria (cada registro aparece en una dirección especial de memoria)

unused

0

ready(read only)

1

Habilitación de interrupción

Control de transmisión(0xffff0008)

unused

07

Byte transmitido

Dato transmitido(0xffff000c)

Diseño de sistemas digitales.9

Interrupciones de E/S Una interrupción de E/S es usada como señal de petición de servicio

Puede tener diferentes niveles de urgencia (debido a que su atención podría ser prioritaria)

Necesita de alguna manera trasladar la identidad del dispositivo que genera la interrupción.

Una interrupción de E/S es una ejecución de una instrucción de escritura asincrona

Una interrupción de E/S no está asociada con ninguna instrucción y no provoca que ninguna instrucción deje de completarse

- Se puede elegir un punto de conveniencia para ejecutar la interrupción Ventaja

El progreso de la ejecución del programa del usuario es solamente parada (halted) durante la transferencia de datos de E/S desde/hacia el usuario desde el espacio en memoria

Desventaja – hardware especial es necesario para Causar la interrupción (Dispositivo de E/S) Detectar una interrupción y salvar la información adecuada para poder

reanudar el programa después de haber servido la interrupción (procesador)

Diseño de sistemas digitales.11

Manejo de interrupción para entrada

memoria

userprogram

1. Interrupción entrada

2.1 salvar PC

Procesador

ReceptorMemoria

addsubandorbeq

lbusb...jr

2.2 salto a la rutina de servicio de la interrupción

2.4 retorno al programa original

Teclado

2.3 servicio de interrupción

Rutina de servicio deinterrupción de entrada

Diseño de sistemas digitales.12

Manejo de interrupción para entrada en SPIM

1. El receptor indica con una interrupción que hay una entrada de un nuevo caracter desde el teclado en el registro de recepción de datos

- La escritura en el registro de recepción de datos (Receiver data register) cambia el estado del “ready bit” de dicho registro a 1

2. El programa en ejecución responde a la interrupción tranfiriendo el control a la rutina de servicio de la interrupción que copia el caracter de entrada en la espacio de memoria del usuario

- La lectura del registro de recepción de datos hace “reset” del “ready bit” del registro de control de datos (cambia su valor de nuevo a 0 )

unused

readyinterrupt enable

Receiver control(0xffff0000)

unused

received byte

Receiver data(0xffff0004)

65

1 10

Diseño de sistemas digitales.14

Interrupt Driven Output

Procesador

TrnsmttrMemoria

Pantalla

addsubandorbeq

lbusb...jr

memoria

Programaoriginal

1.Interrupciónde salida

2.1 salvar PC

Rutina deservicio deinterrupciónde salida

2.2 salto arutina de servicio de interrupción

2.4 retornoal programaoriginal

2.3 servicio de interrupcion

Diseño de sistemas digitales.15

Manejo de interrupción para salida en SPIM1. El transmisor indica con una interrupción que ha sido de

manera exitosa mostrado el caracter en el registro de transmisión de datos (Transmiter data register) en la pantalla (display)

- La lectura del “Transmitter data register” cambia el valor del “ready bit” de dicho registro a 1

2. El programa del usuario responde a dicha interrupción tranfiriendo control a la rutina de servicio de la interrupción que escribe el siguiente caracter al la salida desde el espacio de memoria del usuar2io al registro de transmisión de datos

- La escritura al “Transmitter data register” hace “reset” del “ready bit” de dicho registro a 0

unused

readyinterrupt enable

Transmitter control(0xffff0008)

unused

transmitted byte

Transmitter data(0xffff000c)

65

1 10

Diseño de sistemas digitales.16

Excepciones en General

Excepción = transferencias de control no programadas

El sistema entra en acción para manajar la excepción- Debe guardar la dirección la intrucción interrumpida o la

próxima por ejecutar y salvar (y reestablecer) el estado de usuario

Retorna el control al programa en ejecución después del manejo de la excepción

user program

normal control flow:

sequential, jumps,

branches, calls, returns

Manejo de excepcióndel sistemaExcepción

Retorno Desde excepción

Diseño de sistemas digitales.17

Dos tipos de excepciones Interrupciones

Causadas por eventos externos (tales como peticiones de dispositivos de E/S)

Ejecución de programa asíncrona Pueden ser manejadas entre las instrucciones Simplemente suspenden y restablecen el programa en

ejecución (user program)

Trampas (Traps) (Excepciones) Causadas por eventos internos

- Condiciones de excepción (e.g., sobreflujo (overflow) aritmético, instrucción indefinida.)

- errores (e.g., fallo de hardware, error de paridad de memoria)- fallos (e.g., non-resident page – page fault)

Sincrónicas respecto a la ejecución del programa La condición debe ser remediada por el manejador de traps La instrucción debe ser reintentada (o simulada) y el programa

continuar o ser abortado

Diseño de sistemas digitales.18

Adiciones al set de instrucciones MIPS para el manejo de excepciones

El coprocesador 0 almacena la información que el software necesita para manejar las excepciones

EPC (registro 14) – mantiene el valor de la dirección+4 de la instrucción que fue ejecutada cuando la excepción ocurrió

Status (registro 12) – mascara de trampa/interrupción y bits de habilitación (enable)

- Intr Mask = 1 bit por cada uno de los 6 niveles de excepciones de hardware y los 2 niveles de exepciones de nivel de software for each of 6 hardware and (1 activa excepciones en ese nivel)

- User mode = 0 si está corriendo en “kernel mode” cuando la excepción occurre; 1 si se está corriendo en modo usuario (fijo en 1 en SPIM)

- Excp level = normalmente 1 (excepciones desabilitadas) después de que una excepción occurre; debe ser “reseteado” por el manejo de la excepción (exception handler) cuando finaliza

- Intr enable = 1 si las excepciones están habilitadas; 0 si están desabilitadas

15 8 4 1 0

Intr Mask

Intr enableUser modeExcp level

Diseño de sistemas digitales.19

Addiciones al ISA de MIPS, Con’t BadVAddr (registro 8) – dir de memoria cuando la referencia pasó Cause (registro 13) – tipo de excepción y “pending bits”

- Pending: bit activados si la excepción ocurrie pero no ha sido servida todavía

– Maneja casos donde más de una excepción occurre al mismo tiempo, o graba peticiones de excepción cuando las excepciones están desabilitadas

- Codificación de excepciones: codígos para causas de excepción– 0 (INT) Interrupción externa (petición de dispositivo de E/S)– 4 (AdEL) trampa (trap) para error de direccionamiento (load o instr fetch)– 5 (AdES) trampa para error de direccionamiento (store)– 6 (IBE) error de bus o fetch de instrucción– 7 (DBE) error de bus en obtención (load) o almacenamiento (store) de

datos– 8 (Sys) trampa de llamada de sistema (syscall)– 9 (Bp) trampa de punto de quiebre (breakpoint)– 10 (RI) intrucción de trampa reservada (o indefina)– 12 (Ov) trampa para sobreflujo aritmético (overflow)

15 8

Pending

6 2

Code

Diseño de sistemas digitales.20

Adiciones al ISA de MIPS ISA para interrupciones de E/S

Las señales de control escriben el EPC (EPCWrite), causa (CauseWrite), y estatus

El Hardware almacena el tipo de interrupción en “Cause” Se modifica la máquina de estados finita para que:

La dirección del “interrupt handler” (8000 0180hex) pueda ser almacenada en el registro PC, por lo que debe ser incrementado el tamaño del multiplexor PC (PC mux)

Y salvar la dirección de la próxima instrucción en EPC

Diseño de sistemas digitales.22

Address

Read Data(Instr. or Data)

Memory

PC

Write Data

Read Addr 1

Read Addr 2

Write Addr

Register

File

Read Data 1

Read Data 2

ALU

Write Data

IRM

DR

AB

AL

Uo

ut

SignExtend

Shiftleft 2 ALU

control

Shiftleft 2

ALUOpControl

IRWriteMemtoReg

MemWriteMemRead

IorD

PCWrite

PCWriteCond

RegDstRegWrite

ALUSrcAALUSrcB

zero

PCSource

1

1

1

1

1

10

0

0

0

0

0

2

2

3

4

Instr[5-0]

Instr[25-0]

PC[31-28]

Instr[15-0]

Instr[3

1-2

6]

32

3

EP

C

8000 0180

Ca

us

e

CauseWrite

EPCWriteInterrupt

Flujo de datos multiciclo modificado para interrupciones

Diseño de sistemas digitales.24

Maquina de estados modificada para interr.IorD = 0

MemRead;IRWriteALUSrcA = 0ALUsrcB = 01ALUOp = 00

PCSource = 00PCWrite

ALUSrcA = 0ALUSrcB = 11ALUOp = 00

ALUSrcA = 1ALUSrcB = 10ALUOp = 00

ALUSrcA = 1ALUSrcB = 00ALUOp = 10

ALUSrcA = 1ALUSrcB = 00ALUOp = 01

PCSource = 01PCWriteCond

PCSource = 10PCWrite

MemReadIorD = 1

MemWriteIorD = 1

RegDst = 1RegWrite

MemtoReg = 0

RegDst = 0RegWrite

MemtoReg = 1

Start

Instr Fetch Decode

Write Back

Memory Access

Execute

(Op = R-

type)

(Op =

beq)

(Op = lw or

sw) (Op = j)

(Op = lw)(Op = sw)

0 1

2

3

4

5

6

7

8 9

Interruptpending?

CauseWriteEPCWrite;PCWriteIntrOrExcp = 0PCSource = 11

11

Diseño de sistemas digitales.25

Ejemplo de una rutina de servicio de interrupción para E/S.ktext 0x80000180sw $t0, save0 #save working reg’s. . .mfc0 $k0, $13 #move Cause into

$k0mfc0 $k1, $14 #move EPC into $k1sgt $t0, $k0, 0x00 #is it an

interrupt?bgtz $t0, excpt

intrpt: li $t0, 0xffff0000lw $t1, 0($t0) #test Receiver

control beq $t1, $0, tstout # for input ready

inpt: lb $v0, 4($t0) #input char. into $v0tstout: lw $t1, 8($t0) #test Trans. control

beq $t1, $0, excpt # for output readysb $v1, c($t0) #output char. from

$v1j done #

excpt: . . . #code to handle excptsaddiu $k1, $k1, 4 #do not re-execute

# faulting instrdone: lw $t0, save0 #restore working reg’s

. . .eret #return to user

code.kdata

save0: .word 0. . .

Diseño de sistemas digitales.26

Adiciones al ISA de MIPS para trampas Instrucciones especiales para manejo de trampas

lwc0 y swc0 – para obtener (guardar) un word del espacio de memoria en un registro del coprocesador 0

mfc0 and mtc0 – para mover desde (hacia) un registro del coprocesador 0 hacia (desde) un registro del procesador

eret – retorno desde excepción (return from exception) (limpia el bit EXC del “Status register” y produce un salto a la instrucción a la que apunta EPC)

Las señales de control escriben en EPC (EPCWrite & IntrOrExcp), Cause (CauseWrite), Status, & BadVAddr

Hardware almacena el tipo de trampa en “Cause” Modificación adicional a la máquina de estados finita de tal

manera que: Para las trampas, se almacena la dirección de la instrucción actual

en el EPC, por lo que se debe deshacer el PC = PC + 4 hecho en el proceso de fetch

15 8 4 1 0

Intr Mask

Intr enableUser modeExcp level

Diseño de sistemas digitales.28

Flujo de datos multiciclomodificado para trampas

Address

Read Data(Instr. or Data)

Memory

PC

Write Data

Read Addr 1

Read Addr 2

Write Addr

Register

File

Read Data 1

Read Data 2

ALU

Write Data

IRM

DR

AB

AL

Uo

ut

SignExtend

Shiftleft 2 ALU

control

Shiftleft 2

ALUOpControl

IRWriteMemtoReg

MemWriteMemRead

IorD

PCWrite

PCWriteCond

RegDstRegWrite

ALUSrcAALUSrcB

zero

PCSource

1

1

1

1

1

10

0

0

0

0

0

2

2

301

Instr[5-0]

Instr[25-0]

PC[31-28]

Instr[15-0]

Instr[3

1-2

6]

32

3

EP

C

8000 0180

Ca

us

e

CauseWrite

1

0

EPCWrite

IntrOrExcp

Interrupt

4

Diseño de sistemas digitales.29

Como el control detecta dos trampas Instrucción indefinida (Undefined instruction) (RI) – detecta

cuando no hay un nuevo estado definido a partir del estado 1 del valor del código de operación

Define el nuevo valor de estado para todo los valores de operacion diferentes a lw, sw, R-type, jmp, and beq como el nuevo estado 10

Sobreflujo aritmético (overflow) (OVF) – La señal de “overflow” de la ALU es usada en el estado 6 (si no se quiere completar el RegWrite) o en el estado 7 para especificar el proximo correcto nuevo estado

Se necesita modificar la máquina de estados de una manera similar para las trampas restantes

El desafio consiste en el manejo de las interacciones entre las intrusciones y los eventos que causan excepciones para que la lógica de control se mantenga relativamente pequeña y rápida

- Interacciones de nivel complejo son el aspecto más desafiante del diseño de hardware, especialmente para procesadores “pipelined”

Diseño de sistemas digitales.31

IorD = 0MemRead;IRWrite

ALUSrcA = 0ALUsrcB = 01ALUOp = 00

PCSource = 00PCWrite

ALUSrcA = 0ALUSrcB = 11ALUOp = 00

ALUSrcA = 1ALUSrcB = 10ALUOp = 00

ALUSrcA = 1ALUSrcB = 00ALUOp = 10

ALUSrcA = 1ALUSrcB = 00ALUOp = 01

PCSource = 01PCWriteCond

PCSource = 10PCWrite

MemReadIorD = 1

MemWriteIorD = 1

RegDst = 1RegWrite

MemtoReg = 0

RegDst = 0RegWrite

MemtoReg = 1

Start

Instr Fetch Decode

Write Back

Memory Access

Execute

(Op = R-

type)

(Op =

beq)

(Op = lw or

sw) (Op = j)

(Op = lw)(Op = sw)

0 1

2

3

4

5

6

7

8 9

(Op = other)

CauseWriteALUSrcA =0

ALUSrcB = 01ALUOp = 01

EPCWrite;PCWriteIntrOrExcp = 1PCSource = 11

Overflow

No Overflow

10

Interruptpending?

CauseWriteEPCWrite;PCWriteIntrOrExcp = 0PCSource = 11

11

Modificación de máquina de estados (trampas)

Diseño de sistemas digitales.32

Ejemplo de rutina de servicio de trampa.kdata

s1: .word 0s2: .word 0

.ktext 0x80000180move $k1, $at # Save $atsw $v0, s1 # Not re-entrant and we can't trust

$spsw $a0, s2mfc0 $k0, $13 # Save Cause

sgt $v0, $k0, 0x00 # ignore interrupt exceptions bgtz $v0, ret addu $0, $0, 0

li $v0, 4 # syscall 4 (print_str)la $a0 __m1_syscallli $v0, 1 # syscall 1 (print_int)

srl $a0, $k0, 2 # shift Cause regsyscallli $v0, 4 # syscall 4 (print_str)lw $a0, __excp($k0)syscallbne $k0, 0x18, ok_pc # Bad PC requires special checks

. . .ok_pc:li $v0, 4 # syscall 4 (print_str)

la $a0, __m2_syscallmtc0 $0, $13 # Clear Cause register

ret:lw $v0, s1lw $a0, s2

move $at, $k1 # Restore $atmfc0 $k0, $14 # read EPCaddiu $k0, $k0, 4 # EPC = EPC +4

mtc0 $k0, $14 # to return to next instructioneret # Return from exception handler

Diseño de sistemas digitales.33

Problemas de interconectividad para sistemas de E/S

Memoriacache

Memory - I/O Bus

MainMemory

I/OController

Disk Disk

I/OController

I/OController

Terminal Network

Señales de interrupción

Usualmente existe más de un dispositivo de E/S en el sistema conectado al procesador via un bus

Cada dispositivo de E/S es controlado por un controlador de E/S (I/O Controller)

Procesador

bus

Diseño de sistemas digitales.34

Buses Un bus es un canal de comunicación compartido (un único

conjunto de cables usado para conectar multiples subsistemas) que necesita soportar un rango de dispositivos con latencias y velocidades de tranferencias de magnitud altamente variable

Ventajas- Versatil – nuevos dispositivos pueden ser facilmente añadidos y

movidos entre sistemas computacionales que utilizar en mismo estándar de bus

- Bajo costo – un único conjunto de cables compartido en multiples vías

Desventajas- Crea un cuello de botella en las comunicaciones– el ancho de

banda del bus limita la máxima capacidad de tramisión de E/S (throughput)

La velocidad máxima del bus es altamente limitada por La longitud del bus El numero de dispositivos en dicho bus

Diseño de sistemas digitales.35

Mediciones del desempeño de E/S Ancho de banda de E/S (throughput) – magnitud de la

imformación que puede ser puesta en la entrada (o salida) y comunicada a través de una interconexión (tal como un bus) al procesador/memoria (dispositivo de E/S) por unidad de tiempo1. ¿Que tanta información se puede mover a través del sistema

en un cierto tiempo?2. ¿Cuantas operaciones de E/S se pueden realizar por unidad

de tiempo?

Tiempo de respuesta para E/S (latencia) – el tiempo total que toma completar una operación de entrada o salida Es una métrica de desempeño especialmente importante en

sistemas en tiempo real

Muchas aplicaciones requieren ambos: alto ancho de banda y pequeños tiempos de respuesta

Diseño de sistemas digitales.36

Tipos de Buses Bus entre el procesador y la memora (propietario)

Corto y de alta velocidad Ajustado al sistema de memoria para maximizar el ancho de

banda entre el procesador y la memoria Optimizado para transferencias de blocks en cache

Bus de E/S (estandar industrial, ej., SCSI, USB, Firewire) Usualmente es largo y más lento Necesita ajustarse a un rango muy alto de dispositivos de E/S Se conecta al bus entre el procesador y la memoria o al

“backplane bus” Backplane bus (industry standard, e.g., ATA, PCIexpress)

El “backplane” es una estructura interconectada a lo interno del chasis

Es usado como un bus intermediario para la conección de buses de E/S al bus entre el procesador y la memoria

Diseño de sistemas digitales.37

Ejemplo: Los buses del Pentium 4

System Bus (“Front Side Bus”): 64b x 800 MHz (6.4GB/s), 533 MHz, or 400 MHz

2 serial ATAs:

150 MB/s

8 USBs: 60 MB/s

2 parallel ATA: 100 MB/s

Hub Bus: 8b x 266 MHz

Memory Controller Hub (“Northbridge”)

I/O Controller Hub (“Southbridge”)

Gbit ethernet: 0.266 GB/sDDR SDRAM

Main Memory

Graphics output: 2.0 GB/s

PCI: 32b x 33 MHz

Diseño de sistemas digitales.38

El ancho de banda del Bus determina

El ancho de banda del bus está determinado por: El hecho de si el mismo es síncrono o asíncrono y las

características de temporización del protocolo utilizado El ancho del bus (el número de líneas de datos) El hecho de que el bus soporte transferencias de bloques de

datos o solamente una palabra (word) por vez

Firewire USB 2.0

Tipo I/O I/O

Lineas de datos 4 2

Clocking Asynchronous Synchronous

Max # devices 63 127

Máximo largo 4.5 meters 5 meters

Ancho de banda pico

50 MB/s (400 Mbps)

100 MB/s (800 Mbps)

0.2 MB/s (low) 1.5 MB/s (full) 60 MB/s (high)

Diseño de sistemas digitales.39

Transición en la tecnología de los buses Existe una transición de las compañias desde los buses

sincronos, paralelos y anchos, a buses asíncronos y angostos

Interferencia electromagnética de los cables y variaciones en la temporización dificultan el uso de 16 a 64 cables en paralelo a altas frecuencias de reloj (ej., ~400 MHz) por lo que las compañias están en transición hacia buses con pocos cables de una via corriendo a altas tasas de tranferencia de reloj (~2 GHz)

PCI PCIexpress ATA Serial ATA

Total # wires 120 36 80 7

# data wires 32 – 64 (2-way)

2 x 4 (1-way)

16 (2-way)

2 x 2 (1-way)

Clock (MHz) 33 – 133 635 50 150

Peak BW (MB/s)

128 – 1064 300 100 375 (3 Gbps)

Diseño de sistemas digitales.40

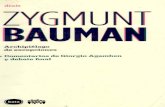

ATA Cable Sizes

Serial ATA cables (red) are much thinner than parallel ATA cables (green)