Design Tradeoffs of Long Links in Hierarchical Tiled Networks-on-Chip Group Research 1 QNoC.

-

Upload

trevor-scott -

Category

Documents

-

view

213 -

download

0

Transcript of Design Tradeoffs of Long Links in Hierarchical Tiled Networks-on-Chip Group Research 1 QNoC.

Design Tradeoffs of Long Links in Hierarchical Tiled Networks-on-

Chip

Ran Manevich, Leon Polishuk, Israel Cidon, and Avinoam Kolodny.

Module

Module Module

Module Module

Module Module

Module

Module

Module

Module

ModuleGroup

Research

Electrical Engineering DepartmentTechnion – Israel Institute of Technology

Haifa, Israel

1

QNoC

Hierarchical NoCs

Hybrid Ring/Mesh S. Bourduas and, Z. Zilic, “Latency reduction of global traffic in wormhole-routed meshes using hierarchical rings for global routing.” ASAP 2007.

PyraMesh R. Manevich, I Cidon and, A. Kolodny. “Handling global

traffic in future CMP NoCs” SLIP 2012.

2

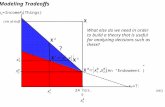

Hierarchical NoCs lower hop distances

2D Mesh

14 Hops

PyraMesh

10 Hops

3

Max. Hop distance vs. Number of Modules

# of Modules

# of Modl sog ule

Go Go

Hierarchical

NoCs!!!

LONG LINKSWho is right?

4

Parallel link delay model

Elmore’s delay:

20.5wired RCl

[ / mm] [F/ mm], [ ],R C l mm

Repeated wire [Bakoglu - 1990]:

0

, 0 00.7 0.4 0.7wire repeated R R

R

R C R Cd l hS C hS C

hS

R

0 0

[repeaters / mm], h Bakoglu 's optimal repeater size

S repeater size normalized to h

R ,C input C and output R of min size inverter

20.5 wired RCl

5

Links delay in 16x16 hierarchical NoC

300 mm2 die

Short1 mm

Medium1.9 mm

Long3.4 mm

16x16 Mesh. 8x8, 4x4 Upper Levels

Elmore’s Delay – Unrepeated, min. size global links (ITRS):

29 nm Technology

Short: 0.11nsMedium: 0.41nsLong: 1.31ns

12X

~17mm

LONG LINKS

6

Adjusting delay of parallel links

Wire sizing: Lower RC delay by changing wire pitch (S and W).

Repeaters insertion: Lower wire delay by inserting repeaters.

7

Wire design parameters

ΛW – Scaling of W vs. min. size global wire [ITRS].

Parameter Range

ΛW [1..50]

ΛS [1..50]

ρ [0..10]

SR [0..1]

ΛS – Scaling of S vs. min. size global wire

ρ - Density of repeaters per millimeter

SR – Repeaters’ size normalized to Bakolu’s optimal size

8

Cost of adjusted links

Wiring Cost -

Power Cost -

Unified cost function -

. ,wire

Cwire

PP

P

Adjusted Wire

Min Global Wire ITRS

C CCF W P 1, , 0

. ,C

Pitch

Pitch

Adjusted WireW

Min Global Wire ITRS

WC = 1 WC = 2

Min. Pitc

h

2X Min. Pitch

WE USE0.5

9

Finding lowest cost wires for target frequency

Parameter Range

ΛW [1..50]

ΛS [1..50]

ρ [0..10]

SR [0..1]

1. Shuffle multiple design configurations (Monte-Carlo).

2. For the target frequency, place each configuration on “Cost Function (CF)-Link Length” plane.

3. Lowest cost configurations along the Pareto curve.

10

Lowest cost links – 29nm-8nm technology nodes

Max. achievable single cycle

lengths – 29nm

Max. achievable single cycle

lengths – 20nm

11

Max. achievable link length for different target

frequencies

3.4 mm

Hierarchical NoCs with single-cycle long links are

feasible at practical frequencies – it’s all a matter of cost. 1

2

Back to our example

1 mm 1.9 mm 3.4 mm

29nm, 17nm, 10nm Technology nodes

1 GHz – 5GHz Target frequencies.

Delay of wires at:

Cost of adjusting wires to:

13

Our example – Delays of NoC wires before

adjustements

1 GHz

2 GHz

5 GHz3 GHz

4 GHz

14

Costs of adjusting wires to 1GHz

15

<1%

Cost Function (CF) [%]

1 GHz

Costs of adjusting wires to 2GHz

2 GHz

Cost Function (CF) [%]<1% 11%

16

Costs of adjusting wires to 3GHz

3 GHz

Cost Function (CF) [%]<1% 6% >1% 4% 39%

17

Costs of adjusting wires to 4GHz

4 GHz

Cost Function (CF) [%]>1% 19% 84%>1% 1% 19%>1% 3%

18

Costs of adjusting wires to 5GHz

5 GHz

Cost Function (CF) [%]1% 36% 164

%>1% 4% 39%>1% 6%1%

19

Definition of cost overhead of adjusting long wires

In our example (CF = Cost Function, l = length ):

Total cost of adjusted wires

Total cost of minimum size wiresOverhead

long – 3.4mmmed – 1.9mmshort – 1mm

( ) ( ) ( ) ( ) ( ) ( )

( ) ( ) ( )

CF short l short CF med l med CF long l long

l short l med l long

Overhead

20

Total length of each kind of links – our 16x16 NoC

Hierarchical NoCs - Few long wires -

Low overhead of adjusting them not to be a bottleneck.21

Cost overhead of adjusting long wires – our 16x16 NoC

65 nm28 nm

28 nm 22

Conclusions

• Long links in hierarchical NoCs: Are a minority. Are not that long! LONGER ≠ LONG Can be adjusted for single cycle at practical

target frequencies with low system costs.

Multi-cycle

long links

Single-cycle long

links

LONG LINKS

Go Go

Hierarchi

cal

NoCs!!!

23

LONG

NOT THAT LONG !

LONG

LONG

Thank You!

24