Design Metrics CMOS Inverter

-

Upload

pramod-srinivasan -

Category

Documents

-

view

230 -

download

1

Transcript of Design Metrics CMOS Inverter

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 1/40

Digital Design Digital Design

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 2/40

Nitin Chaturvedi Nitin Chaturvedi

OutlinesOutlines

Historical Perspectives Historical Perspectives Progresses in Semiconductor Industry

Digital Design Metrics

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 3/40

Nitin Chaturvedi Nitin Chaturvedi

OutlinesOutlines

Historical Perspectives Progresses in Semiconductor Industry

Digital Design Metrics Digital Design Metrics

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 4/40

Nitin Chaturvedi Nitin Chaturvedi

“Microscopic Problems”

• Ultra-high speed design• Interconnect

• Noise, Crosstalk

• Reliability, Manufacturability

• Power Dissipation

• Clock distribution.

Everything Looks a Little DifferentEverything Looks a Little Different

“Macroscopic Issues”

• Time-to-Market• Millions of Gates

• High-Level Abstractions

• Reuse & IP: Portability

• Predictability

• etc.

……and There’s a Lot of Them!and There’s a Lot of Them!

DSMDSM 1/DSM1/DSM

??

Major Challenges in Digital Designs Major Challenges in Digital Designs

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 5/40

Nitin Chaturvedi Nitin Chaturvedi

Design in Deep Submicron Design in Deep Submicron

Design in the deep submicron (DSM) era createsnew challenges

Devices become somewhat different

Global clocking becomes more challenging Interconnect effects play a more significant role

Power dissipation may be thethe limiting factor

We must understand and be able to designdigital ICs in advanced technologies (at or below

180 nm)

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 6/40

Nitin Chaturvedi Nitin Chaturvedi

How to evaluate performance of a digital circuit(gate, block, …)?

Cost (Yield)Cost (Yield)

Reliability (Noise Immunity) Reliability (Noise Immunity) Scalability (Fan-In, Fan-out)Scalability (Fan-In, Fan-out)

Speed (delay, operating frequency)Speed (delay, operating frequency)

Power dissipationPower dissipation

Energy to perform a function Energy to perform a function

Design Metrics Design Metrics

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 7/40

Nitin Chaturvedi Nitin Chaturvedi

NRE NRE (non-recurrent engineering)(non-recurrent engineering) costs design time and effort, mask generation

one-time cost factor

Recurrent Recurrent costs silicon processing, packaging, test

proportional to volume

proportional to chip area

Cost of Integrated CircuitsCost of Integrated Circuits

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 8/40

Nitin Chaturvedi Nitin Chaturvedi

NRE Cost is increasing NRE Cost is increasing

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 9/40

Nitin Chaturvedi Nitin Chaturvedi

From http://www.amd.com

Going up to 12” (30cm)Going up to 12” (30cm)

Die Cost Die Cost

Single DieSingle Die

WaferWafer

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 10/40

Nitin Chaturvedi Nitin Chaturvedi

Fabrication capital cost per transistor (Moore’s law)Fabrication capital cost per transistor (Moore’s law)

0.00000010.00000010.0000010.000001

0.000010.00001

0.00010.0001

0.0010.001

0.010.01

0.10.111

19821982 19851985 19881988 19911991 19941994 19971997 20002000 20032003 20062006 20092009 20122012

CostCost(¢-per-transistor)(¢-per-transistor)

YearYear

Cost Per Transistor Cost Per Transistor

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 11/40

Nitin Chaturvedi Nitin Chaturvedi

Yield Yield

Y =No . of good chips per waferTotal number of chips per wafer

´ 100

Die cost=Wafer cost

Dies per wafer ´ Die yield

Dies per wafer= p ´ ( Wafer diameter/2 )2

Die area−

p ´ Wafer diameter

√ 2 ´ Die area

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 12/40

Nitin Chaturvedi Nitin Chaturvedi

ChipChip MetalMetallayerslayers

LineLine width width

WaferWafercostcost

Def./Def./cmcm22

Area Area mmmm22

Dies/Dies/ wafer wafer

YieldYield DieDiecostcost

386DX386DX 2 0.90 $900 1.0 43 360 71% $4

486 DX2486 DX2 3 0.80 $1200 1.0 81 181 54% $12

Power PCPower PC601601

4 0.80 $1700 1.3 121 115 28% $53

HP PA 7100HP PA 7100 3 0.80 $1300 1.0 196 66 27% $73

DEC Alpha DEC Alpha 3 0.70 $1500 1.2 234 53 19% $149

SuperSuperSparcSparc

3 0.70 $1700 1.6 256 48 13% $272

PentiumPentium 3 0.80 $1500 1.5 296 40 9% $417

Some Examples (in 1994)Some Examples (in 1994)

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 13/40

Nitin Chaturvedi Nitin Chaturvedi

i (t )

Inductive couplingInductive coupling Capacitive couplingCapacitive coupling

v(t )

Power and groundPower and ground

noisenoise

V DD

Reliability Reliability

Noise in Digital Integrated Circuits

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 14/40

Nitin Chaturvedi Nitin Chaturvedi

V(x)V(x)

V(y)V(y)

VOH

VOL

VVMM

VOH

VOL

f

V(y)=V(x)V(y)=V(x)

Switching Threshold Switching Threshold

Nominal Voltage LevelsNominal Voltage Levels

VOH = f (VOL)

VOL = f (VOH)

VM = f (VM)

Voltage Transfer CharacteristicsVoltage Transfer Characteristics

DC Operations DC Operations

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 15/40

Nitin Chaturvedi Nitin Chaturvedi

V V ILIL

V V IHIH

V V inin

Slope = -1Slope = -1

Slope = -1Slope = -1

V V OLOL

V V OHOH

V V out out

““00”” V V OLOL

V V ILIL

V V IH IH

V V OH OH

UndefinedUndefined

RegionRegion

““11””

Mapping between Analog and Digital Mapping between Analog and Digital

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 16/40

Nitin Chaturvedi Nitin Chaturvedi

Noise margin highNoise margin high

Noise margin lowNoise margin low

Undefined RegionUndefined Region

Gate OutputGate Output Gate InputGate Input

V V IH IH

V V ILIL

"1""1"

"0""0"

V V OH OH

V V OLOL

NMNM HH

NMNM LL

Definition of Noise Margins Definition of Noise Margins

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 17/40

Nitin Chaturvedi Nitin Chaturvedi

Key Reliability Properties Key Reliability Properties Absolute noise margin values are deceptive.

A floating node is more easily disturbed than a nodedriven by a low impedance (in terms of voltages)

Noise Immunity is the more important metric

The capability to suppress noise sourcesThe capability to suppress noise sources(Regenerative property)(Regenerative property)

Key metric:

Noise transfer functions,

Output impedance of the driver, and

Input impedance of the receiver.

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 18/40

Nitin Chaturvedi Nitin Chaturvedi

A chain of invertersA chain of inverters

vv00 vv11 vv22 vv33 vv44 vv55 vv66

Regenerative Property Regenerative Property

Ability to recover a corrupted signal Ability to recover a corrupted signal

to a well-defined digital signal to a well-defined digital signal

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 19/40

Nitin Chaturvedi Nitin Chaturvedi

Regenerative Property I Regenerative Property I

RegenerativeRegenerative

Vout Vout

vv00vv22

vv

11

vv33

f(v) f(v)

f f inv inv (v) (v)

Vin Vin

Non-RegenerativeNon-Regenerative

Vout Vout

vv00 vv22

vv

11

vv33 f(v) f(v)

f f inv inv (v) (v)

Vin Vin

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 20/40

Nitin Chaturvedi Nitin Chaturvedi

N N

Fan-outFan-out N N Fan-inFan-in M M

M M

Fan-in and Fan-out Fan-in and Fan-out

Indirectly define scalabilityIndirectly define scalability

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 21/40

Nitin Chaturvedi Nitin Chaturvedi

CMOS Inverter CMOS Inverter

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 22/40

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 23/40

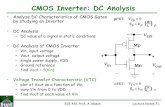

VTC DESIGN ISSUESVTC DESIGN ISSUES

STATIC POWER CONSUMPTION FULL LOGIC LEVELS

SHARP TRANSITION

SWITCHING THRESHOLD→ NOISE

MARGINS

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 24/40

PRACTICAL VTC PRACTICAL VTC

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 25/40

FIVE CRITICAL VOLTAGES FIVE CRITICAL VOLTAGES

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 26/40

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 27/40

Noise Margins Noise Margins

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 28/40

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 29/40

Static characteristicsStatic characteristics

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 30/40

Operating regionsOperating regions

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 31/40

V V OH OH

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 32/40

V V OLOL

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 33/40

V V IL IL

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 34/40

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 35/40

V V IH IH

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 36/40

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 37/40

V V thth -switching threshold -switching threshold

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 38/40

7/29/2019 Design Metrics CMOS Inverter

http://slidepdf.com/reader/full/design-metrics-cmos-inverter 39/40