Cryo and AFE IIt Update

description

Transcript of Cryo and AFE IIt Update

Cryo and AFE IIt Update

MICE Collaboration MeetingOctober 22, 2005

RALA. Bross

Cryo Update I

The cryo-system for the VLPCs has been operated extremely reliably and stably from May through the end of the KEK TB

However, it was felt that the thermal-link design could be made more robust

A bolted concept has now been detailed and will be used in all subsequent systems

The drawing package has been “marked-up” for update The drawing package is currently in the Fermilab drafting

queue. There are a few outstanding issues that still need some

thought Is the top plate stiff enough against atmospheric pressure? Can the new thermal link design permit non-positive

clamping of the cassette so that a cassette could be removed from the cryostat without having to break the cryo-vacuum

Cryo Update II

AFE IIt Update

The AFE IIt prototypes (10) have arrived and are under test

The production run of Tript chips is complete, and approximately 8200 die have been packaged. Enough for about 500 boards

AFE IIt

AFE IIt test Status

The AFE IIt board test is making very good progress All power applied (AFEI power supply values) 1553 communications functional JTAG programming chain working RT1553 FPGA operating properly PIC microcontroller operating properly using new C code (at least for

those tests we have performed so far) HELPER FPGA operating properly for the functions we have checked so

far CLOCKGEN FPGA operating properly, clocks being generated, phase

control from the PC, through 1553 is working properly. Program and read the FLASH memory Use the FLASH to program the DFPGAs Use the FLASH to program the AFPGAs ADC for measuring bias and temp is working Bias DACs, heater DACs are working

Next Steps Test the slow communications to AFPGAs and DFPGAs Apply power to TriP-t chips and ADCs Run the TriP-t and ADCs through the ACQUIRE/DIGITIZE/READOUT cycle

Lots of FPGA programming to Do!

TriPt

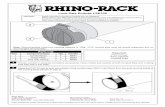

We now have all the packaged TriPts that will be needed Preliminary testing:

Linearity problem at small charge input has indeed been fixed

A-pulse, Ch 6

900

1050

1200

1350

1500

1650

1800

1950

2100

2250

2400

0 20 40 60 80 100 120 140 160 180 200

Qin [fC]

A ou

tput

[mV]

A pulse output, Ch 6

980

1000

1020

1040

1060

1080

1100

1120

1140

1160

1180

1200

0.0 2.0 4.0 6.0 8.0 10.0 12.0 14.0 16.0 18.0 20.0

Qin [fC]

A ou

tput

[mV]

TriPt II

Bandwidth performance looks good

Measuring risetime. G=0111, R1=130, R5=255, 110mA

1000103510701105

114011751210124512801315

1350138514201455

0 10 20 30 40 50 60 70 80 90 100 110 120 130 140

t integration (nS)

Amp

outp

ut (m

V)

C10, Qin=10fC

C10, Qin=40fC

C16

C22

7 bit ilne

55nS for better than 7bit accuracy

TriPt III

Discriminator Performance as expected Likely not an issue with MICE

Turn on curves for all 32 ch

0

10

20

30

40

50

60

70

80

90

100

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

Qin (fC)

Effic

ency

(%)

Ch1 Ch2

Ch3 Ch4

Ch5 Ch6

Ch7 Ch8

Ch9 Ch10

Ch11 Ch12

Ch13 Ch14

Ch15 Ch16

Ch17 Ch18

Ch19 Ch20

Ch21 Ch22

Ch23 Ch24

Ch25 Ch26

Ch27 Ch28

Ch29 Ch30

Ch31 Ch32

TriPt IV

TDC Gain has large spread

This was expected and can be taken out (calibration) off-line

TDC gain

0

1

2

3

4

5

6

7

8

9

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32

Ch number

TDC

gain

[mV/

ns]

T pulse output vs injection time

950

1150

1350

1550

1750

1950

0 10 20 30 40 50 60 70 80 90 100 110 120 130 140 150

T inject before end of window [ns]

T pu

lse

outp

ut [m

V]

TriPt V

Time-walk as expected.

TAC output as a function of Qin

1550157516001625165016751700172517501775180018251850

10 20 30 40 50 60 70 80

Qin [fC]

T-pu

lse

outp

ut [m

V]

Ch1Ch11Ch21Ch31

Issues that will Need some Thought

AFE IIt board temperature and bias calibration Does MICE need a test stand (like D0 has) to do this

operation? LED pulser data

Plan to dismount wavguides and mount a LED pulser or excite the fibers with blue LEDs?

New LVSB Board AVNET (timing) board incorporated into LVSB or

possibly the AFE IIt can be programmed to take over the functionality of the AVNET board

Rate If we keep analog and timing information we are limited to:

1/(150 X 19 ns) 350 muons per msec of spill– It is possible that clever (extreme) programming of the AFE IIt can

push this up a bit – 400-450 or so. If we drop analog and timing and only use discriminators,

we can run at 7 MHz.