Control Components 0

-

Upload

ancient-hermit -

Category

Documents

-

view

218 -

download

0

Transcript of Control Components 0

-

8/13/2019 Control Components 0

1/29

Control and Control Components

Introduction

Software application similar to familiar nested Russian dolls

As weve observed earlier

Application written in some high level programming language

C, C++, C#, JavaMade up of 10s to 1000s lines of code

From implementation language

Each line of code in high-level language

Made up of several lines of target machines assembly language

The machines instruction set

Each line of assembly instruction in instruction set

Made up of several lines of machine code

That is sequences of control statements collections of 1s and 0s

Manipulating sets of registers to affect instruction

Have looked atInstruction sets

Registers and register transfer notation

Now begin to bring pieces together

Objective now

How are such control statements registers and other components

Managed to ensure proper execution of each instruction

Repeating from earlier discussion

Can partition most digital systems into two major types of modules

Datapath

Performs data processing operations

Have studied this component

Control Unit

Specifies and controls sequencing of data processing operations

Sends control signals

To datapath unit to activate operations

Receives status information from datapath

Will now examine this piece

We observe that each level in described hierarchy

Has an associated level of control

At each level must be able to support

Flow of control within program

Sequential

Branch

Loop

- 1 of 29 -

-

8/13/2019 Control Components 0

2/29

Function call

Movement of data

Between registers

Into and out of memory from or to register

Examine such control shortly

Registers and the Datapath

In earlier discussions of datapath and register transfer level

Have learned that datapath is characterized by

Registers

Operations performed on data contained therein

As observed among typical operations

Load, Store

Transfer data

Shift, CountAdd, Subtract

Earlier we identified such elementary operations as microoperations

Typically performed in parallel

On vector of bits during single clock cycle

The control of movement and processing of stored data along datapath

Denoted register transfer operations

Such operations specified by

Set of registers

Operations performed on stored data Control of associated sequences of operations

Repeating fundamental relationship between

Datapath and underlying control given

From system management point of view

Control signals- binary signals

Activate data processing operations

- 2 of 29 -

-

8/13/2019 Control Components 0

3/29

Status signals- binary signals

Identify state of processing operations

Result == zero

Result produced overflow

Result produced carry

Result negativeUsed to define specific sequence of operations

Control Inputs and Outputs

System level signals

Necessary to affect control

Control unit module(s) can be

NonprogrammableTypically implemented as finite state machine

Collection of such machines

Fundamental Mealy and Moore models

Adequate for

Introducing FSM concepts

Expressing and implementing small designs

However expressive power limited for larger systems

Combinational explosion

When trying to develop input equations

Quickly limits utility

Programmable portion of system comprisesInstructions specify

Operation

Operands

Where they can be found

Where to place result of operation

Instructions found in memory

Address of each temporarily contained in special register

Calledprogram counter

Sequence of instructions called microprogramControl values held in special control memory

Often calledprogram store

Flow of control parallels that of higher-level programmable system

Technique can work for programmable or nonprogrammable design

Control unit may perform one or more microoperations on stored data

- 3 of 29 -

-

8/13/2019 Control Components 0

4/29

Thereby form basis for control

Most modern computing and control systems

Will first do quick review of basic concepts

Then explore how we can put them to work

Machines can be implemented in either software or hardware

Software implementation takes form of

Microprogram

Hardware implementation of such machines avails of

LSI Arrayed logic PLD ROM

Discrete logic

Flow of Control a Quick Review

Lets look at flow of control through several different levels

Will begin at top

With application level

Similar to network hierarchy

Application Level High Level Language

Program control may be

Control of data movementBetween registers

Between

Memory and register

Register and memory

Management of program flow

Sequential

Branch

Loop

Function call

Control of Data Movement

Register to Registeri = j; // behind scenes two variables held in registers

Register to MemorymyDataPtr* = aValue; // myDataPtr value is memory address, aValue held

// in registeraValue = myDataPtr*; // myDataPtr value is memory address aValue held

- 4 of 29 -

-

8/13/2019 Control Components 0

5/29

// in register

Sequentiala = 10;b = 20;c = a + b;

Branchif - else construct

if (a == b)c = d + e;

else

3000 Code3053 Procedu re Call F13054 More Code

5000 F1Procedure Code

5053 Return

c = d - e;

Loopwhile (a < 10){

i = i + 2;a++;

}

Procedure Call

Most complex of flow of control constructs

Not more difficult

More involved

Will include

Procedures

Subroutines

Co-routines

Process

Well consider from high level

Program loaded at address 3000

Code executed until address 3053

Procedure encountered

1. Save return address

Several important things to note

Address saved is 3057

Stack gets

Return address

Parameters

2. Address of procedure 5000 put into PC

3. Instruction at 5000 begins executing

4. Execution continues until 5053

5. Return encountered

Action similar to call

Stack gets

Return values

Stack looses

- 5 of 29 -

-

8/13/2019 Control Components 0

6/29

Return address

6. Return Address put into PC

7. Execution continues at 3057

Had procedure call been encountered in procedure F1

Identical process repeated

Can be repeated multiple timesMust be aware that stack can overflow

If too much pushed on

Begin to loose information

Particularly return address

Assembly Level

Application level flow of control

Implemented by properly sequencing assembly language statements

Similar to application level

Program control may beControl of data movement

Between registers

Between

Memory and register

Register and memory

Management of program flow

Sequential

Branch

Loop

Function call

Register Transfer Level

Application level flow of control

Implemented by properly sequencing

Microprogram language statements

Similar to application and assembly levels

Register View The RTL Architecture

As a first step in working at register level for new designIdentify instruction set format to be supported

Instructions built based upon format

Will choose generic set format discussed earlier

Instruction set will be built /utilize around following instruction formats

- 6 of 29 -

-

8/13/2019 Control Components 0

7/29

Next start with architecture of simple computer in following figure

Assumptions

Well assume only 8 general purpose registers

Typically there will be many more

- 7 of 29 -

-

8/13/2019 Control Components 0

8/29

Model will serve as platform to introduce several important concepts

Specifically will look at

Data flow through system How control scheme affects that flow How control signals generated

How instruction word maps to such control

System has single main bus

Made up of following signals

Data Address Control

Constraints

Only one device can be driving the bus at any time

Multiple devices can be simultaneously listening

Data and instructions held in same physical memoryImplements a von Neumann architecture

From diagram above observe

CPU comprises

Datapath and Control blocks

Datapath Block

Registers R0 R7

General Purpose registers

TR0, TR1

Working registers

Accumulator

Processor register

Holds operands during ALU operations

Accepts input from

Set constants

Bus

Output of ALU via TR1ALU

Arithmetic and Logical Unit

Performs arithmetic and logical operationsAccepts operands from

TR0 working register and accumulator

Control Block

Instruction Register IR

Holds instructions fetched from memoryProgram Counter PC

- 8 of 29 -

-

8/13/2019 Control Components 0

9/29

Identifies the next instruction

To be fetched from memoryInstruction Decoder

Decodes instructions fetched from memory

Control Logic

Based upon decoded instructions controlsTransfers to and from registers

Manages sequences of microinstructions

Time Base

Reference for all system timing

Outside of CPU yet on system bus

Memory

Stores instructions and dataMemory Address Register - MAR

Holds address or instruction or data in memoryMemory Data Register - MDR

Holds data to be read from or written to memory

Instruction execution cycle comprised of 5 basic steps

Fetch Fetch instruction

Decode Decode current instruction

Execute Execute current instruction

Writeback Store any results

Next Compute address of next instruction

Lets walk through instruction cycle for this machineInitially at high level

Fetch

Retrieves instruction from memory

Instruction is stored in binary in memory

Harvard machine

Instruction memory

Princeton machine

Combined instruction and data memory

Specifies operationto be performed by computer

ADD, SHIFT, BRANCH

DecodeInterprets op-code and other bits

Contained in instruction

To know what microoperationsneed to be performed

To accomplish specified operation

Execute

Performs microoperationor sequence of microoperations

- 9 of 29 -

-

8/13/2019 Control Components 0

10/29

Microoperationscontrol necessary register transfers

To accomplish specified operation

Operationthus comprised of set of microoperations

Such a set called microprogram

WritebackOperations complete results must be saved

Perform microoperationor sequence of microoperations

Microoperationscontrol necessary transfers to

Registers

Memory(ies)

Next

Determines next operationto performed

Well look at the sequence of operations

Necessary to execute a simple instruction

From C*xPtr = y;

Assume

Value of xPtr has been loaded into R1

This will be a location in data memory

Value of y has been loaded into R2

In assemblerMOV @R1, R2

This is a move indirect instruction

Use the contents of register R1 as an address in memory Use the contents of R2 as source of data Write that data to memory

From instruction cycle state diagramOperation

Fetch

Place address of instruction from PC onto System Bus

Store contents of System BUS into Memory Address Register

Issue a READ command

WaitPlace contents of memory location into Memory Data Register

Place Memory Data Register onto System Bus

Store contents of System Bus into Instruction Register

Decode

Decode OP Code field

- 10 of 29 -

-

8/13/2019 Control Components 0

11/29

Execute

Place contents of R1 onto System Bus

Store contents of System BUS into Memory Address Register

Place R2 onto System Bus

Store contents of System Bus into Memory Data Register

Issue WRITE to memory

Writeback

No Writeback

Next

Place contents of PC onto System Bus

Store contents of BUS into TR0

Select constant input into Accumulator

Add contents of Accumulator and TR0 in ALU

Place output of ALU into TR1 registerPlace contents of TR1 register onto System Bus

Store contents of System Bus into PC

Lets now express instruction cycle using RTN

Fetch

MARPC

Issue READ operation

Wait

MDRM[MAR] // memory data into MDR

IRMDR

Decode

Decode OP Code field

Execute

MARIR // operand address contained in R1

MDRIR // data contained in R2

Issue WRITE operation // write to memory

- 11 of 29 -

-

8/13/2019 Control Components 0

12/29

Writeback - Memory

No writeback

Next

TR0PC

Select Constant // Select constant #1AConstant

TR1A + TR0

PCTR1

In the earlier discussion of datapath components

Utilized two signals to control

Enabling data into register

Gating data output onto tristate bus

Label these as inand out

Now examine register transfer operations

Expressed in RTN for each phase of instruction cycle

Fetch

PCout, MARin

Issue READ operation

Wait

M[MAR], MDRin // memory data into MDR

MDRout, IRin

DecodeDecode OP Code field

Execute

MARin, R1out, // operand address contained in R1

MDRin, R2out // data contained in R2

Issue WRITE operation

Writeback - Memory

No writeback

Next

PCout, TR0in

Select Constant // Select constant #1

Constant, Ain

A, TR0out,ADD,TR1in

TR1out, PCin,

- 12 of 29 -

-

8/13/2019 Control Components 0

13/29

Implementing the Control

Intuitively each in or out signal in RTN expressions above

Expresses control signal

If could control appropriate subsets of signals

In proper order

Could perform each specified register operation

Such signals could be generated in several different ways

Could easily design finite state machine

Could become cumbersome rather quickly

Another alternative

Consider N bit vector

Each bit in vector expresses state of one of control signals

As in familiar combinational logic signals

Let 1 indicate ON or true and 0 express opposite

Each such vectorCalled control wordor microinstruction

Individual bits represent state of control signal

Technique called microprogram control

Collection of such vectors

Called control store

Lets first examine microprogram control

To see how might apply such techniques to simple computer given above

Microprogram ControlFirst step in implementing microprogram control

Formulating control word

First step in formulating control word

Identifying system constraints

Core constraints

Because have only single bus

Can only have single register driving bus at a time

Can have one register driving and one receiving

Beyond bus

Some actionsMust be able to occur simultaneously

Mux selection control and register in

Cannot or need not be simultaneous

IR input and ALU add operation

- 13 of 29 -

-

8/13/2019 Control Components 0

14/29

Building a Microinstruction

Subject to noted constraints

Can formulate microinstruction

Begin at high level

Form categories of operations

Such categories lead to necessary control signals

Categories

From discussion of datapath components

Can easily identify some common operations

That can potentially lead to required controls

General Purpose Register Output and Input

Memory and Temp Register Output and Input

ALU Function Select

Memory Read and Write commands

Mux Control

Wait for Memory delayFlow Control

Category Members

Based upon above architecture

Can take first cut and potentially necessary control signals

Register Outputs Requires 4 bits

None

R0..R7

PC

MDRTR1

Register Inputs Requires 4 bits

None

R0..R7

PC

IR

Memory and Temp Register Inputs Requires 3 bits

None

MAR

MDR

TR0

Accumulator

ALU Function Select Requires 4 bits

Specify 16 ALU functions

Memory Read and Write Requires 2 bits

None

Read

- 14 of 29 -

-

8/13/2019 Control Components 0

15/29

Write

Mux Control Requires 1 bit

Select Constant

Select Bus / TR1

Wait for Memory Requires 1 bit

NoneWait

Flow Control Requires 1 bit

Continue

End

Microinstruction

Within each of categories

Encode each alternative using simple binary code

Using specified number of bits

For this design control word will be 20 bits

Could easily round to 32 for expansion

Based upon categories identified aboveCan formulate structure of microinstruction

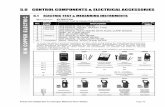

F0 F1 F2 F3 F4 F5 F6 F70000 none 0000 none 000 none 00 none 0000 NOP 0 Sel Const 0 none 0 cont0001 R0out 0001 R0in 001 MARin 01 READ 0001 ADD 1 Sel Bus 1 wait 1 end0010 R1out 0010 R1in 010 MDRin 10 WRITE 0010 SUB0011 R2out 0011 R2in 011 TR0in 0011 MULT0100 R3out 0100 R3in 011 ACCout 0100 DIV0101 R4out 0101 R4in 0101 SHIFTL0110 R5out 0110 R5in 0110 SHIFTR0111 R6out 0111 R6in 0111 1000 R7out 1000 R7in 1000 1001 PCout 1001 PCin 1001 1010 MDRout 1010 IRin 1010 1011 TR0out 1011

1100 1101 1110 1111

Lets now look at microinstruction sequence

To affect execute step from above

From original instruction

From C*xPtr = y;

and again in assemblerMOV @R1, R2 // write contents of R2 to memory location

// identified by R1

Machine instruction format

OP-CODE Operand 2 Operand 1AdxMode

AdxMode

- 15 of 29 -

-

8/13/2019 Control Components 0

16/29

We interpret instruction as follows

Operand 2 is destination

Address mode will be register indirect

Operand 1 is source

Address mode is register direct

Opcode specifies mov operation

We execute mov operation as above

MARin, R1out, // destination adx contained in R1

// Operand2 field in instruction

MDRin, R2out // data contained in R2

// Operand1 field in instruction

Issue WRITE operation

The meaning of each bit pattern has been retained for clarity

In practice each microinstructionWould only comprise the binary bits shown

Finite StateMachine OutputsInputs

Inputs Outputs

Finite State

Machine

State Variables

F0 F1 F2 F3 F4 F5 F6 F70010 R1out 0000 none 001 MARin 00 none 0000 NOP 0 Sel const 0 none 0 cont0011 R2out 0000 none 010 MDRin 10 WRITE 0000 NOP 0 Sel const 0 none 0 cont

Finite State Machine Control

What ever technique used to affect control

Control signals must still be generated

From earlier studies of finite state machines

Our high level block diagram begins with following

Now we have

Set of inputs

Set of outputs

Important to recognize

Outputs may be

State variables

Combinations of state variables

Combinations of

State variables

Inputs

Lets increase the level of detail of out state machine

Well reflect the

Inputs

- 16 of 29 -

-

8/13/2019 Control Components 0

17/29

State variables

Outputs

We see that our state variables

Fed back as inputs to our system

Were now looking at the essence of the strength of the machine

It has the ability to

Recognize the state that it is in

Based upon the values of the state variables

React based upon that information

Decision as to which state to go to next now based upon

The current input

The state that the machine is currently in

Combinational

Logic

Memory

Device

Memory

Device

X0

Xn-1

Z0

Zm-1

Y0(t)

Yp-1

(t)

Y0(t+1)

Yp-1

(t+1)

Lets continue increasing the level of detail

Well increase our view to now includeStorage elements comprising the machine

Combinational logic

Implements output functionality

Input equations to storage elements

Our block diagram now becomes

We now see that we have

n inputs

m outputs

p state variables

Associated with each state variable

We have a memory device

At this point we do not specify the particular type

Working from this model

We can begin to formalize out model of the finite state machine

Our model must reflect

Inputs

OutputsWhich may be a function of

Inputs and State variables

State variables alone

State variables

Movement between statesFinite State Model

Finite State Machine

- 17 of 29 -

-

8/13/2019 Control Components 0

18/29

Also known as finite automaton

Abstract model describing

Sequential machine

Forms basis for understanding and developing

Various computational structures

We now formally define such a finite state machine

We specify the variables

Xi - Represent system n inputs

Zj - Represent system m outputs

Yk - Represent internal p state variables

We define our finite state machine as a quintuple

M = { I, O, S, , }

I - Finite nonempty set or vector of inputsO - Finite nonempty set or vector of outputs

S - Finite nonempty set or vector of states

- Mapping I x S S

1- Mapping I x S O - Mealy Machine

2- Mapping S O - Moore Machine

x is the Cartesian or cross product

The Cartesian product of two vectors

Gives matrix of all possible pairs

Among elements of two vectors

To reflect the different ways of expressing our output

We define

Mealymachine - 1

Output function of

Present state and inputs

Mooremachine - 2Output function of

Present state only

Implementing the Control

From above modelsCould implement necessary control signals

As outputs from an FMS

Either Mealy or Moore model can work

Examine state diagram for Moore model of control

For execute portion of MOV instruction above

From the analysis above

Can segregate control signals into same categories

- 18 of 29 -

-

8/13/2019 Control Components 0

19/29

Use instruction fields to discriminate alternatives

Within categories

Thus state machine can generate input or output enable signals

Instruction field can specify

Which input or output is enabled

Implication of such a design approachMust be state machine for each possible instruction

Nonsequential Control Flow

Implicit in either microprogrammed or finite state scheme

Flow of control sequentially moved from one to next microinstruction

Such an assumption creates two problems

Does not consider branch or jump types of instructions

Either absolute or conditioned

Conditioned cases based upon ALU flag register

Does not recognize that implementations of different microinstructions

May have common blocks of code that can be reused

Prefixing or interspersed within other threads

Second problem duplicates first

Need to jump or branch around differing segments

Flow of control in

Microprogrammed model sequenced by microprogram counter

Analogous to that at machine language level

State machine mode affected by external inputs and state information

To alter flow of control

Microprogrammed model

Must change contents of microprogram counter

State machine model

Must incorporate an edge to incorporate effect of input state

Lets examine microprogrammed model

Nonsequential flow takes two forms

To absolute position

Relative to current position

May be positive or negative

Either case may also be

Qualified

Unqualified

- 19 of 29 -

-

8/13/2019 Control Components 0

20/29

Absolute Control Flow

Absolute control flow implemented

By replacing PC contents with desired location

Effect is to move execution to specified address

Implementation given as

No jump or branchPCPC+1

Jump or branch

UnconditionedPCaddress

Conditioned

Condition falsePCPC+1

Condition truePCaddress

Relative Control Flow

Relative control flow implemented

By algebraically adding offset to PC

Effect is to move forward or backwards

With respect to current position

In contrast to absolute movement

Movement more limited

Implementation given as

No jump or branch

PCPC+1Jump or branch

UnconditionedPCPC+offset

Conditioned

Condition falsePCPC+1

Condition truePCPC+offset

Now need to incorporate flow control information into control word

To do so will add fieldsMust indicate

Jump or branch to be taken

Need two bits

00 no jump or branch

01 jump

10 branch

Conditional or unconditional

- 20 of 29 -

-

8/13/2019 Control Components 0

21/29

Need single bit

0 conditional

1 unconditional

Condition

Assume 4 conditions which implies 2 bits

00 zero01 negative

10 carry11 overflow

F0 F1 F2 F3 F4 F5 F6 F7 F8 F9 F100000 none 0000 none 000 none 00 none 0000 NOP 0 Sel Const 0 none 0 cont 00 no 0 cond 00 zero0001 R0out 0001 R0in 001 MARin 01 READ 0001 ADD 1 Sel Bus 1 wait 1 end 01 jmp 1 ucond 01 neg0010 R1out 0010 R1in 010 MDRin 10 WRITE 0010 SUB 10 br 10 C0011 R2out 0011 R2in 011 TR0in 0011 MULT 11 ovr0100 R3out 0100 R3in 011 ACCout 0100 DIV0101 R4out 0101 R4in 0101 SHFTL0110 R5out 0110 R5in 0110 SHFTR0111 R6out 0111 R6in 0111 1000 R7out 1000 R7in 1000 1001 PCout 1001 PCin 1001 1010 MDRout 1010 IRin 1010

1011 TR0out 1011 1100 1101 1110 1111

With a bit of experience

Lets examine a slightly different architecture

Single Clock Cycle Control

Building on concepts from above

Next machine will be architected as load and store machine

Sometimes also known as register to registermachines

Memory accesses limited to two operations

Load write data from memory to register

Store write data from register to memory

ALU and branch operations

Can only use operands from processor registers

Results must be put in processor registers

Motivation

Movement into and out of memory is expensive operation

Want to limit such movement

Make some other simple modifications to architecture

Implement architecture that fetches and executes

Instruction in single clock cycle

- 21 of 29 -

-

8/13/2019 Control Components 0

22/29

PC updated with each clock cycle

Control implemented as combinational logic

Rather than sequential

Thereby sets pulse width of clock

Modifications will be reflected inRegister set replaced by register file

Bus structure

Will support several local busses

Rather than single system bus

Separate data and instruction memory

Harvard or Aiken architecture

Each has effect of speeding up execution

Datapath

Single clock cycle architecture given in following diagram

Datapath appears on left

Will assume 16-bit data words

Major Blocks

Register file

Contains 8 registers

Control signals derived as outputs from instruction decoder

A adx

B adx

Reg Sel

Write

ALU

Function select

Derived from instruction opcode

From instruction decoder

Multiplexer control

Control signals derived as outputs from instruction decoder

B sel

D sel

Data memory connected to datapath by

Bus A

Provides address for data access

Bus B

Provides data either from

Register file

Constant from instruction

Read / write control

Provide by output from instruction decoder

- 22 of 29 -

-

8/13/2019 Control Components 0

23/29

Control Block

On each cycle

Program counter incremented

Providing address to instruction memory

Instruction

FetchedDecoded

By instruction decoder

Sequential Flow

Executed

Note execution strictly combinational

Nonsequential Flow

Branch

Flags set during previous instruction executionDirect PC to be modified relative to current position

Implemented by adding value to PC

If branch backwards

Offset is negative 2s complement

Jump

PC replaced by value contained on Bus A

Originating in register file

- 23 of 29 -

-

8/13/2019 Control Components 0

24/29

Given goal and architecture

Next step is to identify necessary control signals

As was done with earlier machine

As was done previously such control signals derive fromCurrent instruction

Commands

Sequential

Branch

Jump

State of system following previous instruction

Expressed in values of flags in flag register

Values conditionally direct

Sequential

Branch

Expressed as outputs from instruction decoder block

Necessary Control Signals

As we did earlier

We identify what control signals will be necessary

To manage hardware along datapath

Register File

A address 3

B address 3

Reg Sel 3RW 1

ALU Control

Function Select 4

Assume 16 basic operations

Multiplexer Control

B sel 1

D sel 1

PC Control

Increment / Load 1

Branch / Jump 1

Branch Condition 1

Assume only negative or zero flags

- 24 of 29 -

-

8/13/2019 Control Components 0

25/29

Data Memory

Address 16

Data 16

DMRW 1

Instruction WordBased upon architecture and necessary control signals

Can formulate instruction word

Bus width constraints

Dictate 16 bit instruction word

Register addresses within register file

Dictate 3 bit register addresses

Will support 3 register addresses

Source A address

Source B addressDestination A or B address

Address requirements

Leave 7 bits for opcode

Opcode

When formulating opcode

Identify types of instructions necessary or desired

Register constant operations

Immediate mode types

Register registerRegister direct or indirect types

Load

Store

PC management

Conditional branch

Zero or negative

Unconditional jump

Increment

By default no branch or jump

Decide on format as follows

- 25 of 29 -

-

8/13/2019 Control Components 0

26/29

Instruction Decoder

Based upon such organization and requirements

Formulate instruction decoder output control signals

Instruction Decoder Control Word

Instruction Type Instruction WordBits

19..16 15..13 12..10 9..7 6 5 4 3 2 1 0

15 14 13 12

Funct.Sel12..9

Destadx8..6

Aadx5..3

Badx2..0

Bsel15

Dsel13

RW~14

BRJMP15 14

JMP13

BR12

DMRW

~15 14Register - Register 0 0 0 -Load 0 0 1 -Store 0 1 0 -Register - Constant 1 0 0 -Conditional - Zero 1 1 0 0Conditional - Negative 1 1 0 1Jump 1 1 1 -

Table identifies

Types of instructionsEach type identified by

Most significant 4 bits of instruction word opcode

Bit 15

MS instruction word bit

Distinguishes instruction types that

Access memory

Perform multi register operations

Immediate mode and branch/jump operations

Bit 14

Memory access instructionsDistinguishes load and store operations

Nonmemory access instructions

Identifies branch and jump instructions

Bit 13

Distinguishes data source

ALU or memory

Bit 12

Identifies branch condition

Bits 12..9

Identify the ALU operation to be performed

Datapath component control signals

Derived from most significant 4 opcode bits

Keyed to instruction type

Source and destination registers in register file

Derived from least significant 9 bits of instruction word

- 26 of 29 -

-

8/13/2019 Control Components 0

27/29

Now look at example of representative function type

Instruction word

Decoded control word

Examples

Register ConstantAdd Immediate

Cx = x + 3

AssemblerADI R1, 3; // add 3 to contents of R1

RTLR1R1 + 3

Instruction Word10000010 001 001 011

Control Word0001 001 001 000 1 0 1 0 0 0 0

0001 // bits 12..9 from opcode// assume function sel 0001

001 // destination register R1001 // source A register R1000 // source B register dont care

1 // B sel select constant from instruction0 // D sel dont care1 // RW write back into register file0 // no branch or jump0 // no jump0 // no branch

0 // no write to data memory

Register Register

Load

Cx = *yPtr

AssemblerLD R1, *R2; // load data from memory to contents of R1

RTLR1M[R2]

Instruction Word

00100100 001 010 000 Control Word

0010 001 001 010 1 1 1 0 0 0 00010 // bits 12..9 from opcode

// assume function sel 0010001 // destination register R1001 // source A register R1010 // source B register R2

1 // B sel select register file

- 27 of 29 -

-

8/13/2019 Control Components 0

28/29

1 // D sel select memory out1 // RW write back into register file0 // no branch or jump0 // no jump0 // no branch0 // no write to data memory

Conditional - Zero

Conditional - Zero

Cif(x==0);

AssemblerBRZ R1, $1; // if R1 == 0 branch to label $1

RTLif [R1] = 0 // if contents of R1 == 0 based upon zero flag

// from previous operationPCPC + DEL // value DEL algebraically added to PC

// DEL can be sign extended concatenation of// Dest and B fields// specifies distance forward or backwards from// current location to label $1

if [R1] != 0 // if contents of R1 != 0 based upon zero flag// from previous operation

PCPC + 1 // increment PC

Instruction Word1100100 001 001 010

Control Word0010 001 001 010 1 0 0 1 0 0 0

0100 // bits 12..9 from opcode.. assume function sel 0100001 // destination register field001 // source A register R1010 // source B register field DR + B10

1 // B sel select constant from instruction0 // D sel dont care0 // RW write back into register file1 // branch or jump0 // no jump0 // branch on zero flag0 // no write to data memory

Analysis

Single cycle design

Datapath and control flow reasonableHas some limitations

As observed earlier

Design based upon combinational model

Rather than sequential

Cannot handle various kinds of complex instructions

Examine components along datapath

Longest path comprises

- 28 of 29 -

-

8/13/2019 Control Components 0

29/29

PC

Instruction Memory

Register File Read

B Mux

ALU / Data Memory

Data MuxRegister File Write

Delay along path

Sets minimum period of clock

To increase clock speed can

Decrease delays through component

Eliminate components

Observe

Only using one component along path at a time

As example when ALU being used

Instruction memory sitting idle

If can use multiple components simultaneouslyCan make significant gains in performance

Problem

All components do not have fixed delay

Part variation can lead to wide variation

In end to end path delay

To accommodate would have to consider

Worst case delays through all paths

Not efficient

Will examine ways to deal with such problems next

SummaryHave introduced and explored

Control unit

Designed control scheme based upon

Finite state machine

Microprogrammed control

Applied methodology to two different architectures