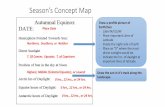

Concept Map

description

Transcript of Concept Map

-

KLU/ECE/2014-15/ODD/Teaching-Learning/FORM-2A(U.G.-T)ECE321 Digital MOS CircuitsUnit 1: Characteristics of MOS Transistors

ECE Department, Kalasalingam UniversityPage 1 of 4

KALASALINGAM UNIVERSITY(Kalasalingam Academy of Research and Education)

Krishnankoil

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

Date:

1. UNIT DETAILS

COURSE CODE/NAME ECE321 Digital MOS Circuits

TOPIC (UNIT) TITLE Unit 1: Characteristics of MOS Transistors

DESCRIPTION

The MOS Field Effect Transistor (MOSFET) is the fundamental building block of MOS and CMOS digitalintegrated circuits. Compared to the bipolar junction transistor (BJT), the MOS transistor occupies arelatively smaller silicon area, and its fabrication involves fewer processing steps. These technologicaladvantages, together with the relative simplicity of MOSFET operation, have helped make the MOStransistor the most widely used switching device in LSI and VLSI circuits. In this unit, we will examine thebasic structure and the electrical behaviour of nMOS (n-channel MOS), as well as pMOS (p- channel MOS)devices. The nMOS transistor is used as the primary switching device in virtually all digital circuitapplications, whereas the pMOS transistor is used mostly in conjunction with the nMOS device in CMOScircuits. However, the basic operation principles of both nMOS and pMOS transistors are very similar toeach other.

DETAILED COURSE TOPICS

This unit starts with a detailed investigation of the basic electrical and physical properties of Metal OxideSemiconductor (MOS) systems, upon which the MOSFET structure is based. We will consider the effects ofexternal bias conditions on charge distribution in the MOS system and on the conductance of free carriers. Itwill be shown that, in field effect devices, the current flow is controlled by externally applied electric fields,

-

KLU/ECE/2014-15/ODD/Teaching-Learning/FORM-2A(U.G.-T)ECE321 Digital MOS CircuitsUnit 1: Characteristics of MOS Transistors

ECE Department, Kalasalingam UniversityPage 2 of 4

and that the operation depends only on the majority carrier flow between two device terminals. Next, thecurrent-voltage characteristics of MOS transistors will be examined in detail, including physical limitationsimposed by small device geometries and various second-order effects observed in MOSFETs. Note thatthese considerations will be particularly important for the overall performance of large-scale digital circuitsbuilt by using small-geometry MOSFET devices.

CONTRIBUTION TOPROFESSIONAL

COMPONENT

Mathematics: 25%Engineering: 25%Basic Sciences: 50%

COURSE OUTCOMES FROMTHIS UNIT

1. Use mathematical methods and circuit analysis models in analysis of CMOS digital electronicscircuits, including logic components and their interconnect

ASSESSMENT TOOLS FORTHIS UNIT Short Answer , Long Answer, Closed Book Test

-

KLU/ECE/2014-15/ODD/Teaching-Learning/FORM-2A(U.G.-T)ECE321 Digital MOS CircuitsUnit 1: Characteristics of MOS Transistors

ECE Department, Kalasalingam UniversityPage 3 of 4

2. CONCEPT MAP

-

KLU/ECE/2014-15/ODD/Teaching-Learning/FORM-2A(U.G.-T)ECE321 Digital MOS CircuitsUnit 1: Characteristics of MOS Transistors

ECE Department, Kalasalingam UniversityPage 4 of 4

3. BOOKS THAT MAY BE REFERRED FOR THIS UNIT

Book Title Author(s) Publisher(s) Edition/Print andYear Chapter(s)# of copies in

Centrallibrary

Dept.library

CMOS Digital Integrated Circuits -Analysis & Design

Sung-Mo Kang &Yusuf Leblebici

Tata McGrawHill 2nd Edition, 2001 1, 2, 3 10 3

Digital Integrated Circuits - A DesignPerspective Jan M Rabaey PHI 2001 3 3 1

4. WEBSITES, ONLINE MATERIALS, E-BOOKS THAT MAY REFERRED FOR THIS UNIT

Unit Topic URL (Address)All topics http://www.seas.upenn.edu/~ese570/MOS transistor theory http://www.cse.wustl.edu/~vgruev/cse/463/index.htm

VTC Parameters - DC Characteristicshttp://ocw.mit.edu/courses/electrical-engineering-and-computer-science/6-374-analysis-and-design-of-digital-integrated-circuits-fall-2003/

Prepared ByCourse CoordinatorName: P. SivakumarSignature with date:

Verified ByModule CoordinatorName: K. JeyaprakashSignature with date:

FOR OFFICE USE ONLYComments (if any):

(Signature of Programme Coordinator with date) (Signature of Head of the Department with date)

-

KLU/ECE/2014-15/ODD/Teaching-Learning/FORM-2A(U.G.-T)ECE321 Digital MOS CircuitsUnit 2: SCALING IN MOSFETS

ECE Department, Kalasalingam UniversityPage 1 of 3

KALASALINGAM UNIVERSITY(Kalasalingam Academy of Research and Education)

Krishnankoil

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERINGDate:

1. UNIT DETAILS

COURSE CODE/NAME ECE321 Digital MOS Circuits

TOPIC (UNIT) TITLE Unit 2: SCALING IN MOSFETS

DESCRIPTION

The design of high-density chips in MOS VLSI (Very Large Scale Integration) technology requires that thepacking density of MOSFETs used in the circuits is as high as possible and, consequently, that the sizes ofthe transistors are as small as possible. The reduction of the size, i.e., the dimensions of MOSFETs, iscommonly referred to as scaling. It is expected that the operational characteristics of the MOS transistor willchange with the reduction of its dimensions. Also, some physical limitations eventually restrict the extent ofscaling that is practically achievable. In this unit, we will examine the constant voltage and constant fieldscaling and scaling issues in interconnects, Latch up in CMOS and methods for preventing latchup. Later wewill discuss about digital MOSFET model, series connection of MOSFETs and body effect.

DETAILED COURSE TOPICSConstant voltage and constant field scaling, Digital MOSFET model, Series connection of MOSFETs, Bodyeffect, Scaling issues in interconnects, Latch up in CMOS and methods for preventing latchup.

CONTRIBUTION TOPROFESSIONAL

COMPONENT

Mathematics: 50%Engineering: 40%Basic Sciences: 10%

COURSE OUTCOMES FROMTHIS UNIT 2. Analyse various scaling in MOSFET and its issues in interconnects

-

KLU/ECE/2014-15/ODD/Teaching-Learning/FORM-2A(U.G.-T)ECE321 Digital MOS CircuitsUnit 2: SCALING IN MOSFETS

ECE Department, Kalasalingam UniversityPage 2 of 3

ASSESSMENT TOOLS FORTHIS UNIT Short Answer , Long Answer, Closed Book Test

2. CONCEPT MAP

-

KLU/ECE/2014-15/ODD/Teaching-Learning/FORM-2A(U.G.-T)ECE321 Digital MOS CircuitsUnit 2: SCALING IN MOSFETS

ECE Department, Kalasalingam UniversityPage 3 of 3

3. BOOKS THAT MAY BE REFERRED FOR THIS UNIT

Book Title Author(s) Publisher(s) Edition/Print andYear Chapter(s)# of copies in

Centrallibrary

Dept.library

CMOS Digital Integrated Circuits -Analysis & Design

Sung-Mo Kang &Yusuf Leblebici

Tata McGrawHill 2nd Edition, 2001 3, 4 10 3

Digital Integrated Circuits - A DesignPerspective Jan M Rabaey PHI 2001 3 3 1

4. WEBSITES, ONLINE MATERIALS, E-BOOKS THAT MAY REFERRED FOR THIS UNIT

Unit Topic URL (Address)All topics http://www.seas.upenn.edu/~ese570/Latch in CMOS http://www.cse.wustl.edu/~vgruev/cse/463/index.htm

Body effecthttp://ocw.mit.edu/courses/electrical-engineering-and-computer-science/6-374-analysis-and-design-of-digital-integrated-circuits-fall-2003/

Prepared ByCourse CoordinatorName:Signature with date:

Verified ByModule CoordinatorName:Signature with date:

FOR OFFICE USE ONLYComments (if any):

(Signature of Programme Coordinator with date) (Signature of Head of the Department with date)

-

KLU/ECE/2014-15/ODD/Teaching-Learning/FORM-2A(U.G.-T)ECE321 Digital MOS Circuits.Unit 3: MOS INVERTERS

ECE Department, Kalasalingam UniversityPage 1 of 4

KALASALINGAM UNIVERSITY(Kalasalingam Academy of Research and Education)

Krishnankoil

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

Date:

1. UNIT DETAILS

COURSE CODE/NAME ECE321 Digital MOS Circuits.

TOPIC (UNIT) TITLE Unit 3: MOS INVERTERS

DESCRIPTION

In this unit, we focus on one single incarnation of the inverter gate, being the static CMOS inverter or theCMOS inverter, in short. This is certainly the most popular at present, and therefore deserves our specialattention. We analyse the gate with respect to the different design metrics:

cost, expressed by the complexity and area integrity and robustness, expressed by the static (or steady-state) behaviour performance, determined by the dynamic (or transient) response energy efficiency, set by the energy and power consumption.

DETAILED COURSE TOPICS

Pseudo NMOS and CMOS inverters Calculation of delay times, Power dissipation for CMOS inverter Design of super buffer Pass transistors and Transmission gates

CONTRIBUTION TOPROFESSIONAL Mathematics: 50%

-

KLU/ECE/2014-15/ODD/Teaching-Learning/FORM-2A(U.G.-T)ECE321 Digital MOS Circuits.Unit 3: MOS INVERTERS

ECE Department, Kalasalingam UniversityPage 2 of 4

COMPONENT Engineering: 50%

COURSE OUTCOMES FROMTHIS UNIT

3. Understand the characteristics of CMOS inverters and the calculation of voltage levels, powerdissipation and delays

ASSESSMENT TOOLS FORTHIS UNIT Short Answer, Long Answer, Assignment

-

KLU/ECE/2014-15/ODD/Teaching-Learning/FORM-2A(U.G.-T)ECE321 Digital MOS Circuits.Unit 3: MOS INVERTERS

ECE Department, Kalasalingam UniversityPage 3 of 4

2. CONCEPT MAP

-

KLU/ECE/2014-15/ODD/Teaching-Learning/FORM-2A(U.G.-T)ECE321 Digital MOS Circuits.Unit 3: MOS INVERTERS

ECE Department, Kalasalingam UniversityPage 4 of 4

3. BOOKS THAT MAY BE REFERRED FOR THIS UNIT

Book Title Author(s) Publisher(s) Edition/Print andYear Chapter(s)# of copies in

Centrallibrary

Dept.library

CMOS Digital Integrated Circuits -Analysis & Design

Sung-Mo Kang &Yusuf Leblebici Tata McGraw Hill 2nd Edition, 2001 5, 6, 7 10 3

Digital Integrated Circuit Design Ken Martin Oxford Univ. Press 2003 4, 5 3 1

4. WEBSITES, ONLINE MATERIALS, E-BOOKS THAT MAY REFERRED FOR THIS UNIT

Unit Topic URL (Address)All topics http://www.seas.upenn.edu/~ese570/Static Characteristics http://www.cse.wustl.edu/~vgruev/cse/463/index.htm

Prepared ByCourse CoordinatorName:Signature with date:

Verified ByModule CoordinatorName:Signature with date:.

FOR OFFICE USE ONLYComments (if any):

(Signature of Programme Coordinator with date) (Signature of Head of the Department with date)

-

KLU/ECE/2014-15/ODD/Teaching-Learning/FORM-2A(U.G.-T)ECE321 Digital MOS Circuits.Unit 4: PSEUDO NMOS

ECE Department, Kalasalingam UniversityPage 1 of 3

KALASALINGAM UNIVERSITY(Kalasalingam Academy of Research and Education)

KrishnankoilDEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

Date:

1. UNIT DETAILS

COURSE CODE/NAME ECE321 Digital MOS Circuits.

TOPIC (UNIT) TITLE Unit 4: PSEUDO NMOS

DESCRIPTION

In high-density, high-performance digital implementations where reduction of circuit delay and silicon areais a major objective, dynamic logic circuits offer several significant advantages over static logic circuits.The operation of all dynamic logic gates depends on temporary (transient) storage of charge in parasiticnode capacitances, instead of relying on steady-state circuit behavior. In this unit, we will examine theDynamic CMOS circuits, Solutions for charge sharing, Method of Logical Effort for high speed CMOSdesign. Later we will discuss about BiCMOS logic circuits, Simple gates using BiCMOS.

DETAILED COURSE TOPICSDynamic CMOS circuits, Solutions for charge sharing - DOMINO Logic- NORA TSPC logic styles,BiCMOS logic circuits

CONTRIBUTION TOPROFESSIONAL

COMPONENT Engineering: 100%

COURSE OUTCOMES FROMTHIS UNIT

4.Classify the various CMOS logic style option and solutions for charge sharing problem5.Apply VLSI methodologies in the implementation of general system components like decoder, Flip flop atCMOS levels

ASSESSMENT TOOLS Short Answer, Long Answer, Assignment, Open book test

-

KLU/ECE/2014-15/ODD/Teaching-Learning/FORM-2A(U.G.-T)ECE321 Digital MOS Circuits.Unit 4: PSEUDO NMOS

ECE Department, Kalasalingam UniversityPage 2 of 3

2. CONCEPT MAP

-

KLU/ECE/2014-15/ODD/Teaching-Learning/FORM-2A(U.G.-T)ECE321 Digital MOS Circuits.Unit 4: PSEUDO NMOS

ECE Department, Kalasalingam UniversityPage 3 of 3

3. BOOKS THAT MAY BE REFERRED FOR THIS UNIT

Book Title Author(s) Publisher(s) Edition/Print andYear Chapter(s)# of copies in

Centrallibrary

Dept.library

CMOS Digital Integrated Circuits -Analysis & Design

Sung-Mo Kang &Yusuf Leblebici

Tata McGrawHill 2nd Edition, 2001 8, 9, 12 10 3

Digital Integrated Circuit Design Ken MartinOxford Univ.Press 2003 7, 8, 9 3 1

4. WEBSITES, ONLINE MATERIALS, E-BOOKS THAT MAY REFERRED FOR THIS UNIT

Unit Topic URL (Address)Sequential Logic http://www.coe.montana.edu/ee/lameres/courses/eele414_fall11/All topics http://www.seas.upenn.edu/~ese570/Static Characteristics http://www.cse.wustl.edu/~vgruev/cse/463/index.htm

Prepared ByCourse CoordinatorName:Signature with date:

Verified ByModule CoordinatorName:Signature with date:.

FOR OFFICE USE ONLYComments (if any):

(Signature of Programme Coordinator with date) (Signature of Head of the Department with date)

-

KLU/ECE/2014-15/ODD/Teaching-Learning/FORM-2A(U.G.-T)ECE321 Digital MOS CircuitsUnit 5: CMOS CLOCKING STYLES

ECE Department, Kalasalingam UniversityPage 1 of 4

KALASALINGAM UNIVERSITY(Kalasalingam Academy of Research and Education)

Krishnankoil

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

Date:

1. UNIT DETAILS

COURSE CODE/NAME ECE321 Digital MOS Circuits

TOPIC (UNIT) TITLE Unit 5: CMOS CLOCKING STYLES

DESCRIPTION

The need for low-power design is also becoming a major issue in high-performance digital systems, such asmicroprocessors, digital signal processors (DSPs) and other applications. The common traits of high-performance chips are the high integration density and the high clock frequency. The power dissipation ofthe chip, and thus, the temperature, increases with the increasing clock frequency. In this unit, we willprimarily concentrate on the circuit- or transistor-level design measures which can be applied to reduce thepower dissipation of digital integrated circuits.The input/output (VO) circuits, clock generation, and distribution circuits are essential to VLSI chip design.The design quality of these circuits is a critical factor that determines the reliability, signal integrity, andinter chip communication speed of the chip in a systems environment.

DETAILED COURSE TOPICSClock generation and distribution, High speed adders, subtractors and multipliers, CMOS Memorystructures, Low power design techniques, Input and Output circuits

CONTRIBUTION TOPROFESSIONAL

COMPONENT Engineering: 100%

-

KLU/ECE/2014-15/ODD/Teaching-Learning/FORM-2A(U.G.-T)ECE321 Digital MOS CircuitsUnit 5: CMOS CLOCKING STYLES

ECE Department, Kalasalingam UniversityPage 2 of 4

COURSE OUTCOMES FROMTHIS UNIT

5. Apply VLSI methodologies in the implementation of general system components like decoder, Flipflop at CMOS levels6. Explain low power design techniques and basic of adiabatic logic

ASSESSMENT TOOLS FORTHIS UNIT Short Answer , Long Answer, Open book test, Assignment

-

KLU/ECE/2014-15/ODD/Teaching-Learning/FORM-2A(U.G.-T)ECE321 Digital MOS CircuitsUnit 5: CMOS CLOCKING STYLES

ECE Department, Kalasalingam UniversityPage 3 of 4

2. CONCEPT MAP

-

KLU/ECE/2014-15/ODD/Teaching-Learning/FORM-2A(U.G.-T)ECE321 Digital MOS CircuitsUnit 5: CMOS CLOCKING STYLES

ECE Department, Kalasalingam UniversityPage 4 of 4

3. BOOKS THAT MAY BE REFERRED FOR THIS UNIT

Book Title Author(s) Publisher(s) Edition/Print andYear Chapter(s)# of copies in

Centrallibrary

Dept.library

CMOS Digital Integrated Circuits -Analysis & Design

Sung-Mo Kang &Yusuf Leblebici

Tata McGrawHill 2nd Edition, 2001 8, 9, 12 10 3

Microelectronics A, B PHI 29th Print, 2009 4 --- 3

4. WEBSITES, ONLINE MATERIALS, E-BOOKS THAT MAY REFERRED FOR THIS UNIT

Unit Topic URL (Address)All topics http://www.seas.upenn.edu/~ese570/Memory, I/O circuits http://www.coe.montana.edu/ee/lameres/courses/eele414_fall11/

Prepared ByCourse CoordinatorName:Signature with date:

Verified ByModule CoordinatorName:Signature with date:

FOR OFFICE USE ONLYComments (if any):

(Signature of Programme Coordinator with date) (Signature of Head of the Department with date)

Unit 1 cm.pdfUnit2 cm.pdfUnit3 cm.pdfUnit4 cm.pdfUnit5 cm.pdf