Computer Architecture and Microprocessor

-

Upload

adisantkapoor -

Category

Documents

-

view

218 -

download

1

Transcript of Computer Architecture and Microprocessor

Printed Pages-S MCA-206

(Following Paper ID and Roll No. to be filled in your Answer Book)I I I I I I I I 1 I

Roll No.

MCA

SECOND SEMESTEREXAMINATION, 2004-200~

' /

COMPUTER ARCHITECTUREAND MICROPROCESSOR

Time: 3 Hours Total Marks: 100

Note: (i)

(ii)

(iii)

Answer ALL questions.

All questions carry equal marks.

In case of numerical problems assume data wherever1!°t provided.

00to(V)M01.0

Answer any two of the following: (10x2=20)

(a) Distinguish among computer terminologies ineach of the following groups:

(i) Uniprocessor systems versus multiprocessorsystems.

Parallelism versus pipelining.~

(ii)

(iii) Control flow computers versus data flowcomputers.

(iv) Serial versus parallel processing.

(b) Give various architectural classification schemes.

Also discuss the Flynn's classification in detail.

MCA-206 1 [Turn Over

(c) Consider the execution of a program of 15,000 .

instructions by a linear pipeline processor with aclock rate of 25 MHz. Assume that the instruction

pipeline has five stages and that one instructionand out-of-sequence executions are ignored.

(i) Calculate the speedup factor in using thispipeline to execute the program as comparedwith the use of an equivalent nonpipelinedprocessor with an equal amount of flow-through delay.

(ii),0 J

What are the efficiency and throughput ofthis pipelined pro,cessor ?

2. Answer any two of the following: (lOx2=20)

MCA-206

(a)

(b)

Discuss the various possible hazards between read& write operations in an instruction pipeline andstate the mechanism to detect and avoid thesehazards.

Consider the following reservation table:

. ~

(i) List the set of forbidden latencies and thecollision vector.

(ii) Draw a state transition diagram.

2

A B A B

A B

B AB A

(c)

'-"

Consider the following pipelined processor withfour stages. This pipeline has a total evaluationtime of six clock cycles. All successor stages mustbe used after each clock cycle.

Output

Input

(i) Specify the reservatioI) t~ble for this pipelinewith six columns anq four rows.

(ii) List the set of forbidden latencies betweentask initiations.

(iii) Draw the state diagrath which shows allpossible latency cycles.

List all greedy cycles from the state diagram.(iv)

(a)

Answer any two of the following: (lOx2=20)3.

r:/

MCA-206

Answer the following questions related tomultistage networks:

(i) Draw a 16 - Input Omega networK using2 x 2 switches as building blocks.

(ii) Determine how many permutations can beimplemented in one pass through theOmega network. What is the percentage ofone - pass permutations among allpermutations.

3

4.

5.

MCA-206

(ill) What is the maximum number of passesneeded to implement any permutationthrough the network?

(b) Discuss the following terms associated with amultiprocessor system: loosely coupledmultiprocessors and Tightly coupledmultiprocessors.

(c) Write short notes on the following:

(i)

(ii)

Cube Interconnection Networks .......

Shuffle - Exchange Networks.,;

Answer any two of the following: (10x2=20)

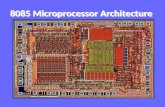

(a) Discuss the architectural featl.\res of Intel-SaSSmicroprocessor also draw the functional blockdiagram.

(b) Discuss the register organization of SOS6microprocessor and explain the function of eachregister.

(c) Describe deterministic scheduling models ofprocessor management techniques used inmultiprocessor system with a suitable diagram.

vAnswer any two of the following: (10x2=20)

(a) Define Instruction. What are the various type ofInstructions used in Intel-SaSS Microprocessor?Explain with suitable example.

4 [Turn Over

..I

r

MCA-206,.

(b) A string of six data bytes is stored starting frommemory location 2050 H. The string inculdes someblanks. Write a program to eliminate the blanksfrom the string.

Data (H) F2, 00, 00, 4A, 98, 00

(c) Define stack and subroutine. Discuss the

subroutine concept with suitable format.(i)

. (ii) Calculate the delay in the following loop,assuming the system.clock period is 0.33 j.Ls.

Label

DELAY

-000-

5

Mnemonics 8085 T - States

LXI B, 12FFH 10

DCXB 6

XTHL 16

XTHL 16

Nap 4

Nap 4

MOV A, C 4

aRAB 4

J N Z DELAY 10/7