Comparison of topside contact layouts for power dies ... · Comparison of topside contact layouts...

Transcript of Comparison of topside contact layouts for power dies ... · Comparison of topside contact layouts...

Comparison of topside contact layouts forpower dies embedded in PCB

ESTC 2016, Grenoble

Chenjiang YU1, Cyril BUTTAY2, Éric LABOURÉ1,Vincent BLEY3, Céline COMBETTES3, Gilles BRILLAT3

1GEEPS, Paris, France2Laboratoire Ampère, Lyon, France

3 LAPLACE, Toulouse, France

14/09/16

1 / 23

Outline

Introduction

Proposed Embedding Technique

Effect of Contact Area/Layout

Summary and Conclusion

2 / 23

Outline

Introduction

Proposed Embedding Technique

Effect of Contact Area/Layout

Summary and Conclusion

3 / 23

Advantages of die embedding

The Printed-Circuit-Board technology (PCB) enables:

I higher interconnect densityI multi-layerI small pitch (down to 25 µm linewidth)

I Low inductance [1]I small sizeI laminated busbar structure

I batch-processed manufacturingI all interconnects are processed at once

E. Hoene, “Ultra Low Inductance Package for SiC” ECPEworkshop on power boards, 2012, [1]

4 / 23

Advantages of die embedding

The Printed-Circuit-Board technology (PCB) enables:

I higher interconnect densityI multi-layerI small pitch (down to 25 µm linewidth)

I Low inductance [1]I small sizeI laminated busbar structure

I batch-processed manufacturingI all interconnects are processed at once

E. Hoene, “Ultra Low Inductance Package for SiC” ECPEworkshop on power boards, 2012, [1]

4 / 23

Advantages of die embedding

The Printed-Circuit-Board technology (PCB) enables:

I higher interconnect densityI multi-layerI small pitch (down to 25 µm linewidth)

I Low inductance [1]I small sizeI laminated busbar structure

I batch-processed manufacturingI all interconnects are processed at once

E. Hoene, “Ultra Low Inductance Package for SiC” ECPEworkshop on power boards, 2012, [1]

4 / 23

Literature Review – Die embedding in PCB – 1

Patents on chip embedding [2]

A. Ostmann, “Leistungselektronik in der Leiterplatte” AT&S Technologieforum, 2013

I Very active area in recent yearsI Many applications to high interconnect densityI Several industrial developments (AT&S, Schweizer, etc.)

5 / 23

Literature Review – Die embedding in PCB – 2

Low-inductance packaging for SiC [1]I Half bridge moduleI 0.8 nH loop inductanceI Embedding die using stud bumps

E. Hoene, “Ultra Low Inductance Package for SiC” ECPE workshop on powerboards, 2012 [1]

I Power module development through germanproject Hi-LEVEL [3]

I 10 kW and 50 kW demonstratorsI Thick copper or DBC for thermal management

http://www.pcdandf.com/pcdesign/index.php/editorial/menu-features/9257-component-packaging-1405

6 / 23

Literature Review – Die embedding in PCB – 2

Low-inductance packaging for SiC [1]I Half bridge moduleI 0.8 nH loop inductanceI Embedding die using stud bumps

E. Hoene, “Ultra Low Inductance Package for SiC” ECPE workshop on powerboards, 2012 [1]

I Power module development through germanproject Hi-LEVEL [3]

I 10 kW and 50 kW demonstratorsI Thick copper or DBC for thermal management

http://www.pcdandf.com/pcdesign/index.php/editorial/menu-features/9257-component-packaging-1405

6 / 23

Outline

Introduction

Proposed Embedding Technique

Effect of Contact Area/Layout

Summary and Conclusion

7 / 23

Overview of the process

I Start with a DBC substrateI Die attach (silver sintering)I PCB stackingI PCB laminationI Topside copper etchingI Laser ablationI Copper electroplating

8 / 23

Overview of the process

I Start with a DBC substrateI Die attach (silver sintering)I PCB stackingI PCB laminationI Topside copper etchingI Laser ablationI Copper electroplating

8 / 23

Overview of the process

I Start with a DBC substrateI Die attach (silver sintering)I PCB stackingI PCB laminationI Topside copper etchingI Laser ablationI Copper electroplating

8 / 23

Overview of the process

I Start with a DBC substrateI Die attach (silver sintering)I PCB stackingI PCB laminationI Topside copper etchingI Laser ablationI Copper electroplating

8 / 23

Overview of the process

I Start with a DBC substrateI Die attach (silver sintering)I PCB stackingI PCB laminationI Topside copper etchingI Laser ablationI Copper electroplating

8 / 23

Overview of the process

I Start with a DBC substrateI Die attach (silver sintering)I PCB stackingI PCB laminationI Topside copper etchingI Laser ablationI Copper electroplating

8 / 23

Overview of the process

I Start with a DBC substrateI Die attach (silver sintering)I PCB stackingI PCB laminationI Topside copper etchingI Laser ablationI Copper electroplating

8 / 23

Overview of the process – significant points

I Backside die attach with silver sintering:I The die does not move during assemblyI Accurate positioning

I Ablation using a CO2 laserI Very good selectivity (metal layers insensitive to laser light)I Use of the copper layer as an alignment mask

I Prototype-scale equipment usedI Can manufacture prototypes from 4x4 cm2 up to 21x28 cm2

I Affordable, useful for process development.

9 / 23

Overview of the process – significant points

I Backside die attach with silver sintering:I The die does not move during assemblyI Accurate positioning

I Ablation using a CO2 laserI Very good selectivity (metal layers insensitive to laser light)I Use of the copper layer as an alignment mask

I Prototype-scale equipment usedI Can manufacture prototypes from 4x4 cm2 up to 21x28 cm2

I Affordable, useful for process development.

9 / 23

Overview of the process – significant points

I Backside die attach with silver sintering:I The die does not move during assemblyI Accurate positioning

I Ablation using a CO2 laserI Very good selectivity (metal layers insensitive to laser light)I Use of the copper layer as an alignment mask

I Prototype-scale equipment usedI Can manufacture prototypes from 4x4 cm2 up to 21x28 cm2

I Affordable, useful for process development.

9 / 23

Die Preparation — Lab-scale process

I Standard Al topside UnsuitableI Ti/Cu PVD with a shadow mask

(50/500 nm)I Simple process for singulated dies

5×5 mm2 IGBT die

10 / 23

Die Preparation — Lab-scale process

Mask

I Standard Al topside UnsuitableI Ti/Cu PVD with a shadow mask

(50/500 nm)I Simple process for singulated dies

5×5 mm2 IGBT die

10 / 23

Die Preparation — Lab-scale process

MaskDie

I Standard Al topside UnsuitableI Ti/Cu PVD with a shadow mask

(50/500 nm)I Simple process for singulated dies

5×5 mm2 IGBT die

10 / 23

Die Preparation — Lab-scale process

PVD

MaskDie

I Standard Al topside UnsuitableI Ti/Cu PVD with a shadow mask

(50/500 nm)I Simple process for singulated dies

5×5 mm2 IGBT die

10 / 23

Die Preparation — Lab-scale process

PVD

MaskDie

I Standard Al topside UnsuitableI Ti/Cu PVD with a shadow mask

(50/500 nm)I Simple process for singulated dies

5×5 mm2 IGBT die

10 / 23

Cross section

I Vertical walls in epoxy layersI Good self-alignmentI No degradation of die topside

metal due to CO2 laserI Die contact not yet perfect

11 / 23

Outline

Introduction

Proposed Embedding Technique

Effect of Contact Area/Layout

Summary and Conclusion

12 / 23

Effect of Contact Area/Layout

Die

Topside copper

Wells

R

Copper foil Electroplated copper

Die

Die topside métallizationfiber-resin composite

I Thick topside copper foil (35 µm)I Thin electroplated copper (10 µm)I Many wells:

I More copper section on wallsI Large well(s):

I Thicker die contact metallizationI reduction of topside copper section

13 / 23

Effect of Contact Area/Layout

Die

Topside copper

Wells

R

Copper foil Electroplated copper

Die

Die topside métallizationfiber-resin composite

I Thick topside copper foil (35 µm)I Thin electroplated copper (10 µm)I Many wells:

I More copper section on wallsI Large well(s):

I Thicker die contact metallizationI reduction of topside copper section

13 / 23

Effect of Contact Area/Layout

Die

Topside copper

Wells

R

Copper foil Electroplated copper

Die

Die topside métallizationfiber-resin composite

I Thick topside copper foil (35 µm)I Thin electroplated copper (10 µm)I Many wells:

I More copper section on wallsI Large well(s):

I Thicker die contact metallizationI reduction of topside copper section

13 / 23

Modelling

Die

Topside copper

Wells

RRtop

Rwall

Rcont

Rdie

RAl

Raccess

Vin

I Structure divided into 100×100µm cellsI 2-D current flow assumedI Generation of a meshed circuit of resistorsI Solving using Modified Nodal Analysis.

14 / 23

Modelling — Results

1 mm2 4 mm2 9 mm2

16 mm2 4 mm2 9 mm2

9 mm2

0.0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1.0Voltage [V]

15 / 23

Modelling — Results (2)

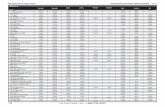

# of Surface Resistancecontacts (mm2) (mΩ)

1 1 3.801 4 2.161 9 1.551 16 1.324 4 1.404 9 1.269 9 1.13

Resistance decreases with:I Contact areaI Contact distribution

Ü Well spread contacts are moreefficient

Ü split 4 mm2 contactcomparable to single 16 mm2

16 / 23

Experimental Validation — Test Vehicles

I 6×6 mm2 diodes embedded in PCBI 4-point connexions for accurate resistance measurementI high current (up to 100 A), pulsed measurement

17 / 23

Experimental Validation — Test Results

0.8 1.0 1.2 1.4 1.6 1.8 2.0Voltage [V]

0

20

40

60

80

100

Cu

rren

t [A

] 13. 6

0mΩ

6.62m

Ω

5.43m

Ω

4.83m

Ω

1 mm² contact

4 mm² contact

9 mm² contact

16 mm² contact# of Surface Resistance

contacts (mm2) (mΩ)1 1 16.51 4 5.61 9 4.91 16 4.74 4 5.44 9 4.49 9 5.2

I Resistance value extracted from I(V) characteristic of diodeI Large scattering of experimental data (±20%)I Same die in standard TO-247 package: 4.4 mΩ

18 / 23

Contact Resistance — conclusions

I Contact distribution is important, contact area not so muchI Experimental results show same trend as simulation

I Resistance 4 times higher!I Poor quality of die/electroplated copper interfaceI Model also probably too optimistic (diode modelled as a resistance)

I Resistance equivalent to that of (commercial) wirebonded dies

19 / 23

Contact Resistance — conclusions

I Contact distribution is important, contact area not so muchI Experimental results show same trend as simulation

I Resistance 4 times higher!I Poor quality of die/electroplated copper interfaceI Model also probably too optimistic (diode modelled as a resistance)

I Resistance equivalent to that of (commercial) wirebonded dies

19 / 23

Contact Resistance — conclusions

I Contact distribution is important, contact area not so muchI Experimental results show same trend as simulation

I Resistance 4 times higher!I Poor quality of die/electroplated copper interfaceI Model also probably too optimistic (diode modelled as a resistance)

I Resistance equivalent to that of (commercial) wirebonded dies

19 / 23

Contact Resistance — conclusions

I Contact distribution is important, contact area not so muchI Experimental results show same trend as simulation

I Resistance 4 times higher!I Poor quality of die/electroplated copper interfaceI Model also probably too optimistic (diode modelled as a resistance)

I Resistance equivalent to that of (commercial) wirebonded dies

19 / 23

Outline

Introduction

Proposed Embedding Technique

Effect of Contact Area/Layout

Summary and Conclusion

20 / 23

Summary and Conclusion

I Embedding of power devicesI Custom design at die levelI Attractive for fast, wide-bandgap devicesI Contact layout allows for better current

spreadingI Simple process

I Lab-scale process presentedI Low contact resistance achievedI Main issue: die topside finish

I Developments to come:I Half-bridge with gate driversI Embedding of passive componentsI Work on thermal design

21 / 23

Summary and Conclusion

I Embedding of power devicesI Custom design at die levelI Attractive for fast, wide-bandgap devicesI Contact layout allows for better current

spreadingI Simple process

I Lab-scale process presentedI Low contact resistance achievedI Main issue: die topside finish

I Developments to come:I Half-bridge with gate driversI Embedding of passive componentsI Work on thermal design

21 / 23

Summary and Conclusion

I Embedding of power devicesI Custom design at die levelI Attractive for fast, wide-bandgap devicesI Contact layout allows for better current

spreadingI Simple process

I Lab-scale process presentedI Low contact resistance achievedI Main issue: die topside finish

I Developments to come:I Half-bridge with gate driversI Embedding of passive componentsI Work on thermal design

21 / 23

Bibliography I

E. Hoene, “Ultra Low Inductance Package for SiC,” in ECPE workshop on powerboards, ECPE, 2012.

A. Ostmann, “Leistungselektronik in der Leiterplatte,” in AT&S Technologieforum,2013.

A. Ostmann, L. Boettcher, D. Manessis, S. Karaszkiewicz, and K.-D. Lang,“Power modules with embedded components,” in Microelectronics PackagingConference (EMPC) , 2013 European, pp. 1–4, Sept. 2013.

22 / 23

Thank you for your attention

contact: [email protected]

This work was funded by the French National Research Agency(ANR) under the grant name ETHAER.

23 / 23