Chapter 6 System Integration and Performance. 2 Chapter Goals Implementation of the system bus and...

-

Upload

rafael-fares -

Category

Documents

-

view

224 -

download

3

Transcript of Chapter 6 System Integration and Performance. 2 Chapter Goals Implementation of the system bus and...

Chapter 6

System Integration and Performance

INFO 225: Chapter 6 2

Chapter Goals

• Implementation of the system bus and bus protocol.

• Interaction of the CPU with peripheral devices.

• Purpose and function of device controllers.

• Interrupting coordination of actions of the CPU with

secondary storage and I/O devices.

• Improving computer system performance by buffers,

caches, and data compression.

INFO 225: Chapter 6 4

Chapter Topics

INFO 225: Chapter 6 5

System Bus

• Bus Terms• Bus Clock and Data Transfer Rate• Bus Protocol

INFO 225: Chapter 6 6

System Bus

Bus – a set of parallel communication lines that connect two or more devices.

System Bus – connects the CPU with main memory and other system components.

Peripheral Devices – devices other than the CPU and primary storage.

INFO 225: Chapter 6 7

System Bus

1. What is carried by the bus line?

Each bus line can carry a single bit value during any bus transfer operation.

2. Are there different types of bus?

Yes, they are categorized based on types of information they carry.

INFO 225: Chapter 6 8

System Bus

Bus Types (or subsets of bus lines)• Data bus

– moves data among computer system components.

• Address bus – carries the bits of a memory address.

• Control bus –– carries, commands, command responses, status

codes, and similar messages.

INFO 225: Chapter 6 9

System Bus

INFO 225: Chapter 6 10

System BusBus Clock and Data Transfer Rate:• Bus clock pulse is a common timing

reference for all attached devices. – Bus clock pulses are carried by one or more control

bus lines.– Frequency of bus clock pulses is expressed in terms of

MHz– Bus clock rate = is equal or a fraction of the CPU clock

rate– Bus cycle time = Time interval between two pulses =

1/(Bus clock rate)e.g.: Bus clock rate = 200 MHz Bus cycle time= 1/200MHz = 5 ns

INFO 225: Chapter 6 11

• Bus length imposes a theoretical max on bus clock rate and a theoretical minimum on bus cycle time.

• Bus capacity = data transfer unit x clock rate = 64 bits x 200 MHz = 1,600,000,000 Bps

This measure of communication capacity is called:• Data transfer rate – rate at which data is transmitted

through a medium or communication channel, as a measurement in data units per time interval.

• To increase Max bus data transfer rate: Increase the clock rate or bus width– Clock rate is limited by bus length, conservative engineering,

and peripheral device costs– Data bus lines should be at least equal to CPU word size.

System Bus

INFO 225: Chapter 6 12

System BusBus Protocol governs:

The format, content and timing of data, memory addresses, and control messages sent across the bus.

• Bus protocol has two effects on maximizing data transfer rate:1. Use of efficient control signal while maintaining reliability of

transmission

2. Regulates bus access by devices and avoiding the message collision using one of the two access control approaches.

INFO 225: Chapter 6 13

System BusAccess Control Approaches:

1. Master-Slave ApproachBus Master (CPU)

Bus Slaves (all other devices)

2. Multiple Master, or Peer-to-Peer Approach• Direct Memory Access

– Uses DMA controller which is a device that assumes bus master (freeing CPU)

• Multiple master bus– Uses Bus arbitration unit which is a simple processor attached to a

multiple master bus

INFO 225: Chapter 6 14

Logical and Physical Access

• An I/O port is a communication pathway from the CPU to a peripheral device.

• An I/O port is a logical abstraction used by the CPU and bus to interact with each peripheral device.

INFO 225: Chapter 6 15

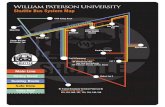

Figure 6-3a A typical personal computer motherboard

INFO 225: Chapter 6 16

Logical and Physical Access

Figure 6-3b: Motherboard with eight I/O ports (slots) and two devices or device controllers attached to the leftmost I/O port

INFO 225: Chapter 6 17

Logical and Physical Access

• The CPU and bus interact with each peripheral device as if it were a storage device containing one or more bytes stored in sequentially numbered addresses.

• A read/write operation from/to this hypothetical storage device is called a logical access.

• The set of sequentially numbered storage locations is called a linear address space.

INFO 225: Chapter 6 18

Logical and Physical AccessExample of Logical Access:

The CPU thinks of the disk as a linear sequence of storage locations, each holding one sector of data, and sends a single number to identify the location it wants to read.

Example of Logical Access:

To access the appropriate sector physically, the location within the assumed linear address space must be converted into the corresponding platter, sector, and track. Linear addresses can be assigned to

physical sectors in any number of ways. The above fig minimizes head-to-head switching and track-to-track seeks.

The disk drive or device controller, translates the linear sector address into the corresponding physical sector location on a specific track.

INFO 225: Chapter 6 19

• CPU communicates with keyboards and sound cards only in terms of sequential streams of bytes that fill the same memory location. The concept of an address or location does not exists.

• Video or printer use logical storage location. The device controller translates logical write operation into the physical actions necessary to illuminate the corresponding pixel or place ink at the corresponding position on the page.

Logical and Physical Access

INFO 225: Chapter 6 20

Device Controllers

• Functions of device controllers• Mainframe Channels

INFO 225: Chapter 6 21

Device Controllers

Storage and I/O devices normally are connected to the system bus through a device controller.

INFO 225: Chapter 6 22

Device Controllers

Functions of Device Controllers:

– Implement the bus interface and access protocols– Translate logical accesses into physical accesses– Permit several devices to share access to a bus

connection

INFO 225: Chapter 6 23

Device Controllers

– Implement the bus interface and access protocols:

• Device controllers translate signals from the bus control lines into appropriate commands to the storage or I/O device.

• Data and status signals from the device are translated into appropriate control and data signals.

INFO 225: Chapter 6 24

Device Controllers

– Translate logical accesses into physical accesses

• Perform some or all of the conversion between logical and physical access commands.

Example:

The device controller converts a logical access to a specific disk sector within a linear address space into a command to read from a specific head, track, and sector.

INFO 225: Chapter 6 25

Device Controllers

– Permit several devices to share access to a bus connection

• The number of physical I/O ports on the system bus may be less than the number of storage and I/O devices.

• Most storage and I/O devices operate slower than the system bus data transfer rate.

• Communication capacity of a single bus connection can be shared among multiple slower devices.

INFO 225: Chapter 6 26

Device Controllers

Mainframe Channels• In many mainframe computer systems, a device

controller can be a dedicated special-purpose computer called an I/O channel or simply a channel.

• The term channel is used by IBM in 300 series mainframe, and gained a generic meaning. Other vendors of mainframe use terms such as peripheral processing unit or front end processor.

INFO 225: Chapter 6 27

Device Controllers

Mainframe Channels

• The difference between an I/O channel and a device controller is a function of power and capability in several key areas:– Number of devices that can be controlled.– Variability in type and capability of attached

devices.– Maximum communication capacity.

INFO 225: Chapter 6 28

Device Controllers

Mainframe Channels• Example:

– A disk controller in a desktop can control 2 disk drives.– A secondary storage channel in a mainframe computer

can control several dozen storage devices of various types such as magnetic disks, optical disks, and magnetic tape drives.

– Another channel in the same mainframe may control up to 100 video display terminals or point-of-sale devices.

INFO 225: Chapter 6 29

Technology Focus - SCSISCSI: Small Computer System Interface

– SCSI is a family of standard buses designed primarily for secondary storage devices.

– There are 9 SCSI standards:1. SCSI-12. SCSI-23. SCSI-34. Ultra SCSI5. Ultra2 SCSI6. Ultra3 SCSI7. Ultra320 SCSI8. Ultra640 SCSI9. Serial Attached SCSI

– There are multiple variations of several SCSI standards e.g. fast, wide, differential, etc.

INFO 225: Chapter 6 30

Technology Focus - SCSI• A SCSI bus implements

– A low-level physical I/O protocol.– A high-level logical device control protocol.

• A SCSI bus can connect up to 16 devices.– Each device is assigned a unique device ID 0-15

• A SCSI bus can be up to 25 meters– Logically the bus is divided into control & data bus

• The control bus transmit control & status signals• The data bus transmits data and device ID numbers

• SCSI-1 has 8 bits wide data bus• Later SCSI standards use a 16-bit data bus.

INFO 225: Chapter 6 31

Technology Focus - SCSI

SCSI controller, bus, and secondary storage devices.

A SCSI controller translates signals between the system bus and the SCSI bus.

INFO 225: Chapter 6 32

Technology Focus - SCSI

A partial listing of SCSI controller signals

INFO 225: Chapter 6 33

Technology Focus - SCSI

A SCSI bus has desirable characteristics:• Non-proprietary standard• High data transfer rate• Multiple master capability• High-level (logical) data access commands• Multiple command execution• Interleaved command execution

INFO 225: Chapter 6 34

Interrupts

• Definition of an Interrupt• Interrupt Handlers• Multiple Interrupts• Stack Processing• Performance Effects

INFO 225: Chapter 6 35

Interrupts

• Secondary storage and I/O device data transfer rates are much slower than the CPU.

• Slow access times and data transfer rates are due to mechanical limitations.

INFO 225: Chapter 6 36

Secondary storage and I/O devices have slower data transfer rates than the CPU.

Interrupts

INFO 225: Chapter 6 37

Interrupts

• The CPU incur one or more wait states if it waits for a device to complete an access request.

• How to prevent such inefficient use of the CPU?– Peripheral devices may interact with the CPU

using interrupt signals.

INFO 225: Chapter 6 38

Interrupts

Interrupt – a signal to the CPU that some event has occurred that requires the CPU to execute a specific program or process.

Physically, an interrupt is an electrical signal generated by a peripheral device and then sent over the control bus.

A portion of the CPU continuously monitors the bus for interrupt signals and copies them to an interrupt register.

The interrupt signal is a numeric value called interrupt code, usually equivalent to the bus port number of the peripheral device sending the interrupt.

INFO 225: Chapter 6 39

Interrupts

At the conclusion of each execution cycle, the control unit checks the interrupt register for a nonzero value.

• If one is present, the CPU suspends execution of the current process, resets the interrupt register to zero, and proceeds to process the interrupt.

• When the interrupt has been processed, the CPU resumes executing the suspended process.

INFO 225: Chapter 6 40

Interrupts• There is one operating system service routine, called an interrupt handler, to

process each possible interrupt.

• Each interrupt handler is a separate program stored in a separate part of primary storage.

• In order to process an interrupt, the CPU must load and execute the first instruction of the correct interrupt handler.

• An interrupt table stores the memory address of the first instruction of each interrupt handler.

• When the CPU detects an interrupt, it executes a master interrupt handler program called the supervisor.

• The supervisor examines the interrupt code stored in the interrupt register and uses it as an INDEX to the interrupt table.

• The supervisor extracts the corresponding memory address and transfers control to the interrupt handler at that address.

INFO 225: Chapter 6 41

Interrupts

Multiple Interrupts

When multiple interrupts occur:

Which interrupt has priority?

What is done with the interrupt that does not have priority?

INFO 225: Chapter 6 42

InterruptsMultiple Interrupts

Interrupts are classified into the following categories:– I/O event: completion of a read/write operation

– Error condition: SW: open non-existing file.

HW: dropped modem connection

– Service request: issued by application programs to request OS services.

• An OS groups interrupts by their importance or priority. • For example, if a hardware error interrupt code is detected

while and I/O interrupt is being processed, the I/O processing is suspended and the hardware error is processed immediately.

INFO 225: Chapter 6 43

InterruptsStack Processing

• Stack – is a reserved area of main memory that is access in a Last-In, First-Out basis. (LIFO)

• Push – adding data of registers to the stack.

• Pop – removing data from the stack.

• Machine state – The saved register values in the stack.

• Stack overflow error – push values to a stack which is filled to the capacity

• Stack pointer – A special purpose register pointing to the next empty address in the stack

INFO 225: Chapter 6 44

Interrupts

Processing Effects

Figure 6-7 summarizes the sequence of events that occurs when processing an interrupt.

INFO 225: Chapter 6 45

HardwareDetect interruptPush registers on stackIncrement stack pointerBranch to supervisor

SupervisorSearch interrupt tableReset interrupt registerPUSH registers on stackIncrement stack pointerBranch to interrupt handler

Interrupt handlerProcess interruptPOP stack

SupervisorDecrement stack pointerPOP stack

Application program

Application Program

Interrupts

Interrupt Processing

INFO 225: Chapter 6 46

Buffers and Caches

• Definition of Buffer• Diminishing Returns• Cache• Primary Storage Caches

INFO 225: Chapter 6 47

Buffers and Caches

Buffer – a small storage area used to hold data in transit from one device to another.

• Resolves differences in data transfer rate or data transfer unit size.

• Required when there is a difference in data transfer unit size.

• If a buffer is not large enough to hold a full page, a buffer overflow occurs.

INFO 225: Chapter 6 48

Buffers and Caches

INFO 225: Chapter 6 49

Buffers and Caches

Diminishing Returns – as buffer size increases, CPU cycle consumption decreases at a nearly linear rate, but total bus cycles decrease at a diminishing rate.

INFO 225: Chapter 6 50

Buffers & Caches Bus & CPU cycles consumed for a 64KB data transfer with various buffer sizes (Table 6-4)

Buffer Size Bus Data Transfer

Interrupts Total Bus Transfers

Improvement CPU Interrupt Processing Cycle

Improvement

4 16,383 32,768 49,152 N/A 3,276,800 N/A

8 16,383 16,384 32,768 33.33% 1,638,400 50%

16 16,383 8,192 24,576 25% 819,200 50%

32 16,383 4,096 20,480 16.67% 409,600 50%

64 16,383 2,048 18,432 10% 204,800 50%

128 16,383 1,024 17,408 5.56% 102,400 50%

256 16,383 512 16,896 2.94% 51,200 50%

512 16,383 256 16,640 1.52% 25,600 50%

1,024 16,383 128 16,512 0.77% 12,800 50%

INFO 225: Chapter 6 51

Buffers and Caches

INFO 225: Chapter 6 52

Buffers and Caches

Cache – a storage area (usually RAM) used to improve system performance.

INFO 225: Chapter 6 53

Buffers and Caches

Differences between cache and a buffer:• Data content is not automatically removed as it is

used.• Cache is used for bidirectional data transfer• Cache is used only for storage devices accesses• Caches are usually much larger that buffers• Cache content must be managed intelligently

INFO 225: Chapter 6 54

Buffers and Caches

Write caching can result in more significant performance improvement when one write access must be confirmed before another can begin (e.g., transaction updates for banks and retailers).

Figure 6-9:

A storage write operation using a cache

INFO 225: Chapter 6 55

Buffers and Caches

Most of the performance benefits of a cache occur during read operations.

INFO 225: Chapter 6 56

Buffers and CachesCache Terms:• Cache hit

– When a read operation accesses data already contained within the cache

• Cache miss– When the data needed is not in the cache

• Hit ratio– The ration of cache hits to read accesses

• Cache swap– A cache miss requires that a cache swap to or

from the storage device be performed

INFO 225: Chapter 6 57

Buffers and Caches

Primary Storage Caches

• Level 1 (L1) – with-in CPU• Level 2 (L2) – on-chip cache• Level 3 (L3) – off-chip cache

INFO 225: Chapter 6 58

Technology Focus

INFO 225: Chapter 6 59

Buffers and Caches

Secondary Storage Caches – disk caching that can improve system performance.

Specific strategies:• Give frequently accessed files higher priority for

cache retention.• Use read-ahead caching for files that are read

sequentially.• Give files opened for random access lower priority

for cache retention.

INFO 225: Chapter 6 60

Compression

• Definition of compression• Compression algorithm• Decompression algorithm• Compression algorithms

– Lossy Compression– Compression ratio

INFO 225: Chapter 6 61

Compression

Compression – a technique that reduces the number of bits used to encode a set of related data items.

INFO 225: Chapter 6 62

Compression

Compression algorithm – a specified mathematical compression technique implemented as a program.

Decompression algorithm – used to restore compressed data to its original or nearly original state.

INFO 225: Chapter 6 63

Compression

Lossy compression – the result of compressing and then decompressing a data input is different than, but still similar to, the original input (audio or video streams).

Compression ratio – describes the ratio of data sizes in bit or bytes before and after compression (word processing, ASCII and Unicode text files).

INFO 225: Chapter 6 64

Compression

INFO 225: Chapter 6 65

Technology Focus

INFO 225: Chapter 6 66

Summary

• The system bus is the communication pathway that connects the CPU with memory and other devices.

• The CPU communicates with peripheral devices through I/O ports.

INFO 225: Chapter 6 67

Summary

• Application programs use interrupt processing to coordinate data transfers to or from peripheral devices, notify the CPU of errors, and call operating system service programs.

• A buffer is a region of memory that holds a single unit of data for transfer to or from a device.

INFO 225: Chapter 6 68

Summary

• Compression reduces the number of bits required to encode a data set or stream, effectively increasing the capacity of a communication channel or storage device.

INFO 225: Chapter 6 69