Chap5 Arithmetic Circuit

-

Upload

jose-lopez -

Category

Documents

-

view

227 -

download

0

Transcript of Chap5 Arithmetic Circuit

-

8/13/2019 Chap5 Arithmetic Circuit

1/46

Chapter 5.

Arithmetic Circuits

1

-

8/13/2019 Chap5 Arithmetic Circuit

2/46

Representation of signed numbers of base r

1) Signed magnitude (aka, sign & magnitude)2) rs complement (2s complement in binary)

r- s comp emen s comp emen n nary

Signed magnitudeuman- r en y way: + -

sign (+,-) magnitude

,bit (0 = plus, 1 = minus)

-

-(2n-1 - 1) ~ +(2n-1 - 1)

two resentations of zero (+0, -0)Representation

2

sign bit magnitude

-

8/13/2019 Chap5 Arithmetic Circuit

3/46

SignedDecimal

(ex) 4 bit numbers

magn u e0000 +0

0001 +1

0010 +2

0011 +3+

0101 +5

0110 +6

01111000

+7-0

1010

1011

-

-2

-31100

1101

-4

-5

-

3

1111 -7

-

8/13/2019 Chap5 Arithmetic Circuit

4/46

(r-1)s complement

n- g pos ve num er n ase r (r-1)s complement of N= (rn 1) - N

ex s comp emen o

99999 105

-1-

47479

1s complement (for binary number system)

(ex) 1s complement of 101100

-101100

010011

4

-

8/13/2019 Chap5 Arithmetic Circuit

5/46

Representation

n-bit numbers

s gn t magn u e com emen nega ve

-( 2n-1- 1 ) ~ +( 2n-1 - 1 )

two representations of zero (+0, -0)

5

-

8/13/2019 Chap5 Arithmetic Circuit

6/46

1sDecimal

(ex) 4 bit numbers

0000 +0

0001 +1

0010 +2

0011 +3

0101 +5

0110 +6

01111000

+7-7

-

symmetric

1010

1011

-5

-41100

1101

1110

-3

-2

-1

6

1111 -0

-

8/13/2019 Chap5 Arithmetic Circuit

7/46

rs complement

n-digit positive number N in base r rs complement of N = rn N for N 0

0 for N = 0

(ex) 10s complement of 52520100000 105

-52520

2s complement (for binary number system)

s comp emen +

(ex) 2s complement of 101100 = 010011 + 1 =010100

-101100

010100

7

-

8/13/2019 Chap5 Arithmetic Circuit

8/46

Representation

n-bit numbers

s gn t magn u e com emen nega ve

-(2n-1) ~ +(2n-1 - 1)

Only one zero (+0)

xtra negat ve : -n-

no pos t ve counterpart

8

-

8/13/2019 Chap5 Arithmetic Circuit

9/46

2sDecimal

(ex) 4 bit numbers

0000 +0

0001 +1

0010 +2

0011 +3

0101 +5

0110 +6

01111000

+7-8

-

1010

1011

-6

-51100

1101

1110

-4

-3

-2

9

1111 -1

-

8/13/2019 Chap5 Arithmetic Circuit

10/46

Signed magnitude addition

igns are t e sameAdd the magnitudes

11001011+

1111

(-4)(-3)(-7)

2) Signs are different

Compare magnitudes(larger one) (smaller one)Give the result sign of the larger

0011+

1001

-(+3)(-1)

Signed magnitude subtraction

Add with minuend addition

ex

00111100

00110100+

(+3)(-4)

(+3)(+4)

00110100

00111100+

(+3)(+4)

(+3)(-4)

10

Very complicated

on ru e

-

8/13/2019 Chap5 Arithmetic Circuit

11/46

1s complement addition

nc u ng s gnTake the carry out and add it to the sum

(ex) 4 bit

0111

0100+ 47 1100

1000+ -7-3 1111

1010+ -50 1111

1111+ -00

cf: x + (-x) = -0, (+0) + (+0) = +0

1 1

11001

1101

1100

-2+ -3

-5

1010

,

11

-

8/13/2019 Chap5 Arithmetic Circuit

12/46

Overflow is said to occur if an addition produces a result

a excee s e range o e num er sys emOverflow occurs when two numbers of the same sign are

0

0+

1

1+

In general, overflow occurs if carries into and out of MSB

1 0

or

are different1011-4

1 1 1 101004

0 001004

0 11011-4

1 0

10000

0101+ 51 1110

1010+ -5-1 1001

0101+ 59 10101

1010+ -5-9(-6)

1 1correctincorrect

10111

11001011

-3+ -4

-7

1 0

- + - +

(exception)incorrect(overflow)

12

1

1000 (-7)

(+) + (+) (-)OF

-

8/13/2019 Chap5 Arithmetic Circuit

13/46

1s complement subtraction

om emen e u ra en Add

A B = A + -B

( A) (-B) = ( A) + (B)

2s complement addition

Add including sign bit

I nore an carr out of the MSB

Overflow occurs if carries into and out of MSB are

different

0111

00110100

3+ 4

7 10011

01101101

6+ -3

3

1 1

10000

01011011

5+ -5

0

1 1

the onl 0

13

-

8/13/2019 Chap5 Arithmetic Circuit

14/46

1101

10100011

-6+ 3- (-3) 10111

10101101

-6+ -3

- (+7) 1001

01100011

6+ 3

-7

1 0 0 1

correct

-1 1

incorrect

(overflow)

incorrect(overflow)

11001

1100- 4-7 (-7)

correct

V = Cin Cout

V

V = 1 overflow

ou n

+2s complement subtraction Complement the subtrahend

14

-

8/13/2019 Chap5 Arithmetic Circuit

15/46

(cf) comparison

1s complement 2s complement

- easier to complement - simpler addition (no end-around-carry)

2s complement is preferred for most digital systems

- one zero representation

15

-

8/13/2019 Chap5 Arithmetic Circuit

16/46

Half-adder (two 1-bit numbers addition)

Simplest adder that adds two 1-bit inputs producing twooutputs, sum and carry

A B C S

0 0 0 0

SA

1 0 0 1

1 1 1 0 C

S = AB + AB = A B

=

But what we really need to do is add threebits: the

, .

1 1 1 0

16

+ 1 1 1 01 1 0 0 1

-

8/13/2019 Chap5 Arithmetic Circuit

17/46

-

8/13/2019 Chap5 Arithmetic Circuit

18/46

A

B S

C

C

Can build a full adder by putting together two HAs

18

-

8/13/2019 Chap5 Arithmetic Circuit

19/46

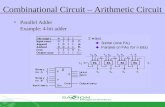

Binary parallel adder (ripple adder)

B3 A3 B2 A2 B1 A1 B0 A0

FA FAFAFA C0 = 0C

2 C1C

3

C4

HA can be

Voverflowdetecting

LSB FA

slow since a carry must propagate from

least significant FA to most significant FA

19

-

8/13/2019 Chap5 Arithmetic Circuit

20/46

When you add two 4-bit numbers the carry in is always 0,

so w y oes e - a er ave a npuOne reason is so we can put 4-bit adders together to

four full adders together to make the 4-bit adder in the

first lace.

CI is also useful for subtraction

Here is an 8-bit adder or e a e.

20

-

8/13/2019 Chap5 Arithmetic Circuit

21/46

Binary parallel subtractor (ripple subtractor)

s comp emen su rac on X Y = X + (-Y) = X + Y + 1

(ex) 4 bit ripple subtractor

bit-by-bit complement of Y

21

-

8/13/2019 Chap5 Arithmetic Circuit

22/46

Binary parallel adder/subtractor

0 1

A 3 B 3 B3

0 1

A 2 B2 B2

0 1

A 1 B1 B1

0 1

A 0 B 0 B0

Sel Sel Sel Sel

A B

CO + CI

A B

CO + CI

A B

CO + CI

A B

CO + CI Add/Subtract

S S S S

3 2 1 0

Overflow

22

-

8/13/2019 Chap5 Arithmetic Circuit

23/46

Carry lookahead adder

carry propagation delay of ripple adder is a limitingfactor on the speed

mos w e y use ec n que or re uc ng e e ay :principle of carry look-ahead

23

-

8/13/2019 Chap5 Arithmetic Circuit

24/46

Define two variables

Pi = Ai Bi -> carry propagateCi+1 = Ci if one of Ai and Bi is 1 while the other is 0 (Ai Bi = 1)

i i i Gi = 1 if Ai and Bi are both 1, independent of Ci

Si = Ai Bi Ci = Pi CiCi+1 = AiBi + Ci (Ai Bi ) = Gi + PiCi

C1 = G0 + P0C0= + = + +

C3 = G2 + P2C2 = G2 + P2G1 + P2P1G0 + P2P1P0C0

C4 = G3 + P3C3 = G3 + P3G2 + P3P2G1 + P3P2P1G0 + P3P2P1P0C0

24

-

8/13/2019 Chap5 Arithmetic Circuit

25/46

25

-

8/13/2019 Chap5 Arithmetic Circuit

26/46

CF: Comparison (n-bit adder)

o ga es nee ecarry lookahead adder

n-1

3n + (i+2) = 3n+ [(n-1)n]/2 + 2n

i=0

= n2/ 2 n / 2 + 5 n = n2/2 + 9/2 n O(n2)

ripple adder : 5n -> O(n)

# of levels (delay)lookahead :4

Cout=AB+BC+AC XOR

Trade-off between complexity and performance

Ri le carry adders are sim ler, but slower

26

Carry lookahead adders are faster but more complex.

-

8/13/2019 Chap5 Arithmetic Circuit

27/46

BCD adder

01100011

6+ 3

01100111

6+

1001

9

Binary sum = BCD sum

1101

13 13 in binary sum, but

not used in BCD0110+

10011

1 or carry-out

max BCD sum = 9 + 9 + 1 = 19

n u carry

27

-

8/13/2019 Chap5 Arithmetic Circuit

28/46

Decimal Binary Sum BCD Sum

3 2 1 0 3 2 1 0

0 0 0 0 0 0 0 0 0 0 0

1 0 0 0 0 1 0 0 0 0 1

2 0 0 0 1 0 0 0 0 1 0

3 0 0 0 1 1 0 0 0 1 1

4 0 0 1 0 0 0 0 1 0 0 Binar Sum = BCD Sum

6 0 0 1 1 0 0 0 1 1 0

7 0 0 1 1 1 0 0 1 1 1

9 0 1 0 0 1 0 1 0 0 1

10 0 1 0 1 0 1 0 0 0 0

12 0 1 1 0 0 1 0 0 1 0

13 0 1 1 0 1 1 0 0 1 1

nary um

+ 0 1 1 0

15 0 1 1 1 1 1 0 1 0 1

16 1 0 0 0 0 1 0 1 1 0

28

18 1 0 0 1 0 1 1 0 0 019 1 0 0 1 1 1 1 0 0 1

-

8/13/2019 Chap5 Arithmetic Circuit

29/46

-

8/13/2019 Chap5 Arithmetic Circuit

30/46

Binary multiplier

u p ca on s us repea e a on.AND operation is equivalent to multiplication on two bits

a b ab

0 0 0

0 1 0

a b ab

0 0 0

0 1 0

1 0 0

1 1 1

1 0 0

1 1 1

1 1 0 1 Multiplicand (m bit)x 0 1 1 0 Multiplier (n bit)

0 0 0 0 Partial products

1 1 0 1

+ 0 0 0 0

30

-

8/13/2019 Chap5 Arithmetic Circuit

31/46

Since we always multiply by either 0 or 1, the partial

in this example).

Ex: 2x2 binary multiplier

B1 B0x A1 A0

A0B1 A0B0+ A1B1 A1B0

C3 C2 C1 C0

HA HA

31

-

8/13/2019 Chap5 Arithmetic Circuit

32/46

4x4 binary multiplierB0B1B2B3

A0

B0 A0

A1

B1 A0

A2

B2 A0

A3

B3 A0

B0 A1B1 A1B2 A1B3 A1

AND gate

B0 A3

B1 A3

B2 A3B3 A3adder

When multiplying an m-bit number (multiplicand ) by an n-

C6 C5 C4 C3 C2 C1 C0C7

t num er mu t p er

There are n partial products

-This requires (n-1) adders, each of which can add m bits(the size of the multiplicand).

32

-

8/13/2019 Chap5 Arithmetic Circuit

33/46

A0 B0A1 B0A0 B1A0 B2A1 B1A2 B0A0 B3A 1 B2A2 B1A3 B0A1 B3A2 B2A3 B1A2 B3A3 B2A3 B3B3A3B

3A

2 B2A3 B3A1 B2A2 B1A3 B3A0 B2A1 B1A2 B0A3 B2A0B

1A

1 B0A2 B0A1B

1A

0 B0A0

HAHAFA HA

FA

FAFA FAFA

FAFA HA

S0S1S3S4 S2S5S6S7

33

-

8/13/2019 Chap5 Arithmetic Circuit

34/46

34

-

8/13/2019 Chap5 Arithmetic Circuit

35/46

Arithmetic Lo ic Unit ALUCombinational network that performs both arithmetic andlogic operations

The heart of a processor you could say that

everything else in the CPU is there to support the ALU.

35

-

8/13/2019 Chap5 Arithmetic Circuit

36/46

The basic four-bit adder alwayscomputes S = A + B + CI.

But by changing what goes into the adder inputs A, B andCI, we can change the adder output S.

This is also what we did to build the combined adder- .

So we have one adder performing two separate functions.

36

whether the circuit performs addition or subtraction.

-

8/13/2019 Chap5 Arithmetic Circuit

37/46

By following the same approach, we can use an adder to

compu e o er unc ons as we .

37

-

8/13/2019 Chap5 Arithmetic Circuit

38/46

Here are some of the different possible arithmetic.

Selection code Desired arithmetic operation Required adder inputs

S2 S1 S0 G (A + B + CI) A B CI

0 0 0 X (transfer) 0000 X 0

0 0 1 X + 1 increment 0000 X 10 1 0 X + Y (add) Y X 0

0 1 1 X + Y + 1 Y X 1

1 0 0 X + Y 1C subtraction Y X 0

1 0 1 X + Y + 1 (2C subtraction) Y X 11 1 0 X 1 (decrement) 1111 X 0

1 1 1 X transfer 1111 X 1

Adder input CI is always the same as selection code bit S0.

.A depends only on S2 and S1.

38

-

8/13/2019 Chap5 Arithmetic Circuit

39/46

All we need to do is compute the adder input A, given the

(actually just S2 and S1).

2 1 i i

0 0 0 0

0 0 1 0

0 0 0000

0 1 Y

0 1 0 0

0 1 1 1

1 1 1111 1 0 1 01 1 0 1

1 1 1 1

S2S1 Yi

1 0 1 1Ai = S2Yi + S1Yi

39

-

8/13/2019 Chap5 Arithmetic Circuit

40/46

This completes our arithmetic unit.

40S0

A l i it t diff t l i l f ti t

-

8/13/2019 Chap5 Arithmetic Circuit

41/46

A logic unit supports different logical functions on two- , .

Four possible functions

implement this.

S1 S0 Output

0 0 Gi= XiYi

0 1 Gi= Xi+ Yi

1 0 Gi= XiYi1 1 Gi= Xi

41

-

8/13/2019 Chap5 Arithmetic Circuit

42/46

Now we have two pieces:

An arit metic unit t at can compute eig t unctionsA logic unit that can perform four functions.

,

S3 S2 S1 S0 O eration0 0 0 0 G = X

0 0 0 1 G = X + 1

= +

0 0 1 1 G = X + Y + 10 1 0 0 G = X + Y

= + +

0 1 1 0 G = X 1

0 1 1 1 G = X

1 x 0 1 G = X or Y

1 x 1 0 G = X Y

42

1 x 1 1 G = X

l

-

8/13/2019 Chap5 Arithmetic Circuit

43/46

A complete ALU circuit

4

4

4

44

43

Thi ALU i d l f hi hi l d i

-

8/13/2019 Chap5 Arithmetic Circuit

44/46

This ALU is a good example of hierarchical design.

Wit t e 12 inputs, t e trut ta e wou ave a 2 =4096 lines.

Instead we were able to use com onents that weve seenbefore to construct the entire circuit from a couple ofeasy-to-understand components.

4

44

44

-

8/13/2019 Chap5 Arithmetic Circuit

45/46

-

8/13/2019 Chap5 Arithmetic Circuit

46/46

Selection M = 1 M = 0, Arithmetic Functions

S3

0

0

0

S2

0

0

0

S1

0

0

1

S0

0

1

0

Logic Function

F = not A

F = A nand B

F = (not A) + B

Cn = 0

F = A minus 1

F = A B minus 1

F = A (not B) minus 1

Cn = 1

F = A

F = A B

F = A (not B)

0

0

0

1

1

1

0

0

1

0

1

0

=

F = A nor B

F = not B

F = A xnor B

= m nus

F = A plus (A + not B)

F = A B plus (A + not B)

F = A minus B minus 1

= zero

F = A plus (A + not B) plus 1

F = A B plus (A + not B) plus 1

F = (A + not B) plus 1

1

1

1

0

0

0

0

0

1

0

1

0

=

F = (not A) B

F = A xor B

F = B

=

F = A plus (A + B)

F = A plus B

F = A (not B) plus (A + B)

=

F = (A + not B) plus 1

F = A plus (A + B) plus 1

F = A (not B) plus (A + B) plus 1

1

1

1

1

1

1

0

0

1

0

1

0

F = 0

F = A (not B)

F = A B

=

F = A

F = A B plus A

F= A (not B) plus A

=

F = A plus A plus 1

F = AB plus A plus 1

F = A (not B) plus A plus 1

=

46