an efficient implementation of modified booth encoder for floating point signed and unsigned...

-

Upload

puvvadi-venkata-krishna-mohan -

Category

Documents

-

view

221 -

download

0

Transcript of an efficient implementation of modified booth encoder for floating point signed and unsigned...

8/9/2019 an efficient implementation of modified booth encoder for floating point signed and unsigned numbers

http://slidepdf.com/reader/full/an-efficient-implementation-of-modified-booth-encoder-for-floating-point-signed 1/6

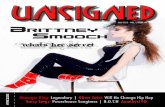

An Efficient Implementation of High Speed Modified

Booth Encoder for Floating Point Signed & Unsigned

Numbers

P!"rishna Mohan #upta

$

% hS!Maruthi 'ao

(

% #' Padmini

)

%$M*ech +,SE-% Sre.as Institutite of Engineering & *echnolog.% H.derabad% pu//adi0rish1gmailcom (Associate Professor% Sre.as Institutite of Engineering & *echnolog.% H.derabad%

maruthichinnam1gmailcom

)Associate Professor% !asa/i ollege of Engineering% H.derabad% grpadmini$()1rediffmailcom

Abstract---Multiplication is an important fundamental function

in arithmetic operations. It can be performed with the help of

different multipliers using different techniques. In this paper we

focus on an efficient implementation of an IEEE 754 single

precision floating point multiplier with signed and unsigned

numbers. The multiplier implementation in floating point

multiplication is done by Modified Booth Encoding MBE!

multiplier to reduce the partial products by half. The multiplier

ta"es care of o#erflow and underflow cases. $ounding is not

implemented to gi#e more precision when using the multiplier in

a Multiply and %ccumulate M%&! unit. By using MBE

multiplier we increases the speed of multiplication' reduces the

power dissipation and cost of a system. The proposed multiplier

will be designed and #erified using Modelsim with (erilog )*+.

,ilin- is used for synthesis.

Keywordsfloating point multiplication' %rray Multiplier'

MBE' /artial /roducts' o#erflow and underflow

I. I0T$1*2&TI10

*oda. the main applications of floating point numbersare in the field of medical imaging% biometrics% motioncapture and audio applications Since multiplicationdominates the e2ecution time of most ,SP algorithms% thereis a need of high speed multiplier 3ith more accurac.'educing the time dela. and po3er consumption are /er.essential re4uirements for man. applications Floating Point

Numbers5 *he term floating point is deri/ed from the fact thatthere is no fi2ed number of digits before and after the decimal

point% that is% the decimal point can float*he Institute of Electrical and Electronics Engineers

+IEEE- sponsored a standard format for )(6bit and larger floating point numbers% 0no3n as IEEE 789 standard :$;

*his paper presents a ne3 floating point multiplier 3hichoperates on single6precision floating point *he con/entionalfloating point multipliers use Arra. multiplier for Mantissamultiplication :(; In this paper 3e presents a Modified Booth

Encoder +MBE- multiplier :);:9; for Significand or Mantissamultiplication% 3hich reduces the partial products b. half% toachie/e speed of operation and reduces the timedela.:<;Normal MBE multiplier ha/ing arr. Sa/eAdder+SA- for partial product addition:8;% here in thisfloating point multiplier 3e proposed 'ipple arr.Adder+'A- to reduce the comple2it. of the circuit andcomplicated more number of bit addition *his paper isorgani=ed as follo3s5 In section I +B- mainl. concentrated onSingle Precision floating point numbers% section II focuses onfloating point algorithm% section III concentrate on different

multiplication methods:7;:>;% section I! loo0ing for hard3areof floating point multiplier+Bloc0 diagram-% section !contains the e2ponent result on o/erflo3 or underflo3 andfinal sectional e2plains s.nthesis results and conclusions of this pro?ect

A. Floating Point Arithmetic

*he IEEE 789 :$; standard is the most 3idel. used

standard for floating point computation% and is follo3ed b.man. PU implementation *he standard defines formats for representing floating point number +including @ =ero anddenormals- and special /alues +infinities and NaNs- together 3ith a set of floating point operations IEEE 789:$; specifiesfour formats for representing floating point /alues5 single6

precision +)(6bit-% double6precision +<96bit-% single6e2tended precision + 9)6bit% not commonl. used- and double e2tended precision + 76bit% usuall. implemented 3ith >C bits-

B. Single Precision Floating point Numbers

*hus% a total of )( bits is needed for single6precisionnumber representation *o achie/e a bias e4ual to ( n-1 6$ isadded to the actual e2ponent in order to obtain the stored

e2ponent *his e4ual $(7 for an >6bit e2ponent of the single precision format *he addition of bias allo3s the use of ane2ponent in the range from 6$(< to @$(7 *he single precisionformat offers a range from ( -126 to(+127

. Fig $ sho3s theIEEE 789 single precision binar. format representationD itconsists of a one bit sign +S-% an eight bit e2ponent +E-% and at3ent. three bit fraction +M or Mantissa- An e2tra bit isadded to the fraction to form 3hat is called the significand$ If the e2ponent is greater than C and smaller than (88% and thereis $ in the MSB of the significand then the number is said to

be a normali=ed numberD in this case the real number isrepresented b. +$-

Fig $ IEEE single precision floating point format

Z +6$S-(+E6Bias-+$M- +$-

8/9/2019 an efficient implementation of modified booth encoder for floating point signed and unsigned numbers

http://slidepdf.com/reader/full/an-efficient-implementation-of-modified-booth-encoder-for-floating-point-signed 2/6

Ghere M m(( (6$ @ m($ (6( @ m(C (

6)@@ m$ (6((@ mC (6()D

Bias $(7

$Significand is the mantissa 3ith an e2tra MSB bit

C. Floating Point Multiplication

Multiplication of t3o numbers in floating point format isdone b. follo3ing steps5 $ adding the e2ponent of the t3o

numbers then subtracting the bias from their result% (multipl.ing the significand of the t3o numbers% and)calculating the sign b. J'ing the sign of the t3o numbersIn order to represent the multiplication result as a normali=ednumber there should be $ in the MSB of the result +leadingone-% detailed e2planation is gi/en in ne2t section

II. 3+1%TI0 /1I0T M2+TI/+I&%TI10 %+1$IT)M

Floating point multiplication algorithm is sho3n in fig +(-in the belo3 flo3chart

Fig ( IEEE single precision floating point format

As stated in the introduction% normali=ed floating pointnumbers ha/e the form of K +6$S- ( +E 6 Bias- +$M- *o

multipl. t3o floating point numbers the follo3ing is done5

$ Multipl.ing the significandD ie +$M$$M(-( Placing the decimal point in the result

) Adding the e2ponentsD ie +E$ @ E( L Bias-

9 Jbtaining the signD ie s$ 2or s( 8 Normali=ing the resultD ie obtaining $ at the MSB of the

results significand

< 'ounding the result to fit in the a/ailable bits

7. hec0ing for underflo3o/erflo3 occurrence

onsider a floating point representation similar to the

IEEE 789 single precision floating point format% but 3ith a

reduced number of mantissa bits +onl. 9- 3hile still retaining

the hidden $ bit for normali=ed numbers5

A C $CCCC$CC C$CC 9C%

B $ $CCCCCC$ $$$C 6 78

*o multipl. A and B

1. Multipl. significand5 1.0100

× 1.1110

00000

10100

10100

10100

_10100____

1001011000

2. Place the decimal point5 10.01011000

) Add e2ponents5 10000100

+ 10000001100000101

*he e2ponent representing the t3o numbers is alread.shiftedObiased b. the bias /alue +$(7- and is not the truee2ponentD ie EA EA6true @ bias and EB EB6true @ bias and EA @

EB EA6true @ EB6true @ ( bias

So 3e should subtract the bias from the resultant e2ponentother3ise the bias 3ill be added t3ice

100000101

- 0111111110000110

$ Jbtain the sign bit and put the result together5

1. 10000110 10.01011000

( Normali=e the result so that there is a $ ?ust before the radi2

point +decimal point- Mo/ing the radi2 point one place to the

left increments the e2ponent b. $D mo/ing one place to the

right decrements the e2ponent b. $

a. 10000110 1001011000 +before normali=ing-

b. 10000111 1001011000 +normali=ed-

*he result is +3ithout the hidden bit-5

1 10000111 00101100

) *he mantissa bits are more than 9 bits +mantissa a/ailable

bits-D rounding is needed If 3e applied the truncation

rounding mode then the stored /alue is5

1 10000111 0010

In this paper 3e present a floating point multiplier in

8/9/2019 an efficient implementation of modified booth encoder for floating point signed and unsigned numbers

http://slidepdf.com/reader/full/an-efficient-implementation-of-modified-booth-encoder-for-floating-point-signed 3/6

3hich rounding support isnt implemented 'ounding supportcan be added as a separate unit that can be accessed b. themultiplier or b. a floating point adder% thus accommodatingfor more precision if the multiplier is connected directl. to anadder in a MA unit Fig ) sho3s the multiplier structureDE2ponents addition% Significand multiplication% and 'esultssign calculation are independent and are done in parallel *hesignificand multiplication is done on t3o (9 bit numbers andresults in a 9> bit product% 3hich 3e 3ill call the intermediate

product +IP- *he IP is represented as +97 do3nto C- and thedecimal point is located bet3een bits 9< and 98 in the IP

Fig ) Floating point multiplier bloc0 diagram

III. MET)1*6 31$ M2+TI/+I&%TI10

*here are number of techni4ues that can be used to

perform multiplication In general% the choice is based uponfactors such as latenc.% throughput% area% and design

comple2it.

a- Arra. Multiplier b- Booth Multiplier

a Array Multiplier

Arra. multiplier is an efficient la.out of a combinationalmultiplier Multiplication of t3o binar. number can beobtained 3ith one micro6operation b. using a combinational

circuit that forms the product bit all at once thus ma0ing it a

fast 3a. of multipl.ing t3o numbers since onl. dela. is the

time for the signals to propagate through the gates that formsthe multiplication arra. In arra. multiplier% consider to3

binar. numbers A and B% of m and n bits *here are mn

summands that are produced in parallel b. a set of mn AN,

gates n 2 n multiplier re4uires n +n6(- full adders% n half6adders and n( AN, gates Also% in arra. multiplier 3orst case

dela. 3ould be +(n@$- td

b Booth Multiplier Booths multiplication algorithm is a multiplication

algorithm that multiplies t3o signed binar. numbers in t3os

complement notation *he algorithm 3as in/ented b. Andre3

,onald Booth :9; on/entional arra. multipliers% li0e the Braun multiplier and Baugh Goolle. multiplier achie/e comparati/el. good

performance but the. re4uire large area of silicon% unli0e theadd6shift algorithms% 3hich re4uire less hard3are and e2hibit

poorer performance *he Booth multiplier ma0es use of Booth

encoding algorithm in order to reduce the number of partial products b. considering t3o bits of the multiplier at a time%there b. achie/ing a speed ad/antage o/er other multiplier architectures *his algorithm is /alid for both signed andunsigned numbers It accepts the number in (s complementform *he Modified Booth encoder Floating point multiplier architecture is identified 3ith the follo3ing bloc0s as sho3nin fig +)- *he follo3ing sections detail each bloc0 of the

floating point multiplier

I(. )%$*%$E 13 3+1%TI0 /1I0T M2+TI/+IE$

*he hard3are of floating point multiplier is mainl.

di/ided into a- sign bit calculation% b- e2ponent addition% c-significand multiplication and d- normali=e unit

A. Sign bit calculation

Multipl.ing t3o numbers results in a negati/e sign number

if one of the multiplied numbers is of a negati/e /alue B. the

aid of a truth table 3e find that this can be obtained b.

J'ing the sign of t3o inputs

B. !nsigned Adder "#or e$ponent addition

*his unsigned adder is responsible for adding the e2ponent

of the first input to the e2ponent of the second input andsubtracting the Bias +$(7- from the addition result +ie

Ae2ponent @ Be2ponent 6 Bias- *he result of this stage is

called the intermediate e2ponent *he add operation is done

on > bits% and there is no need for a 4uic0 result because mostof the calculation time is spent in the significand

multiplication process +multipl.ing (9 bits b. (9 bits-D thus

3e need a moderate e2ponent adder and a fast significand

multiplier

An >6bit ripple carr. adder is used to add the t3o input

e2ponents As sho3n in Fig ) a ripple carr. adder is a chainof cascaded full adders and one half adderD each full adder has

three inputs +A% B% i- and t3o outputs +S% o- *he carr. out

+o- of each adder is fed to the ne2t full adder +ie each carr.

bit QripplesQ to the ne2t full adder-

Fig9 'ipple arr. Adder

*he addition process produces an > bit sum +S7 to SC- and a

carr. bit +o%7- *hese bits are concatenated to form a bit

addition result +S> to SC- from 3hich the Bias is subtracted

*he Bias is subtracted using an arra. of ripple borro3subtractors

8/9/2019 an efficient implementation of modified booth encoder for floating point signed and unsigned numbers

http://slidepdf.com/reader/full/an-efficient-implementation-of-modified-booth-encoder-for-floating-point-signed 4/6

Fig8 sho3s the Bias subtractor 3hich is a chain of 7 onesubtractors +JS- follo3ed b. ( =ero subtractors +KS-D the

borro3 output of each subtractor is fed to the ne2t subtractorIf an underflo3 occurs then Eresult R C and the number is out of the IEEE 789 single precision normali=ed numbers rangeD inthis case the output is signaled to C and an underflo3 flag isasserted

Fig 8 'ipple Borro3 Subtractor

C. !nsigned Multiplier "#or signi#icand multiplication

*his unit is responsible for multipl.ing the unsigned

significand and placing the decimal point in the multiplication product *he result of significand multiplication 3ill be called

the intermediate product +IP- *he unsigned significand

multiplication is done on (9 bit Multiplier performance

should be ta0en into consideration so as not to affect the3hole multipliers performance *he modified6Booth

algorithm is e2tensi/el. used for high6speed multiplier

circuits *he multiplier here 3e are design and implement

multiplier for signed and unsigned numbers using MBEtechni4ue *able $ sho3s the truth table of MBE scheme

From table $ the MBE logic diagram is implemented as sho3n

in Fig8 Using the MBE logic and considering other

conditions the Boolean e2pression for one bit partial product

generator is gi/en b. the e4uation (

*ABE $5 *ruth *able of MBE Scheme

bi+1

bi bi-1 /alue I$a I(a K Neg

C C C C $ C $ C

C C $ $ C $ $ C

C $ C $ C $ C C

C $ $ ( $ C C C

$ C C 6( $ C C $

$ C $ 6$ C $ C $

$ $ C 6$ C $ $ $

$ $ $ C $ C $ C

E4uation ) is implemented as sho3n in Fig8 *he

SUMBE multiplier does not separatel. consider the encoder

and the decoder logic% but instead implemented as a single unitcalled partial product generator as sho3n Fig <

Fig < ogic diagram of MBE

*ABE (5 Sho3s the SUMBE multiplier operation

Sign6unsign *.pe of operation

C Unsigned multiplication$ Signed multiplication

Fig sho3s the partial products generated b. partial product generator circuit 3hich is sho3n in Fig 8 *here are86partial products 3ith sign e2tension and negate bit N i Allthe 86partial products are generated in parallel

a7 a6 a5 a4 a3 a2 a1 a0

b7 b6 b5 b4 b3 b2 b1 b0

p08 p08 p08 p07 p06 p05 p04 p03 p02 p01 p00 I$

1 p18 p17 p16 p15 p14 p13 p12 p11 p10 N 0 I(

1 p28 p27 p26 p25 p24 p23 p22 p21 p20 N 1 )

1 p38 p37 p36 p35 p34 p33 p32 p31 p30 N 2 9

P 47 p46 p45 p44 p43 p42 p41 p40 N) 8

p15 p14 p13 p12 p11 p10 p9 p8 p7 p6 p5 p4 p3 p2 p1 p0

Fig 7 ogic diagram of $6bit partial product generator

%. Normali&er

8/9/2019 an efficient implementation of modified booth encoder for floating point signed and unsigned numbers

http://slidepdf.com/reader/full/an-efficient-implementation-of-modified-booth-encoder-for-floating-point-signed 5/6

*he result of the significand multiplication +intermediate product- must be normali=ed to ha/e a leading $ ?ust to theleft of the decimal point +ie in the bit 9< in the intermediate

product- Since the inputs are normali=ed numbers then theintermediate product has the leading one at bit 9< or 97$ If the leading one is at bit 9< +ie to the left of the decimal

point- then the intermediate product is alread. anormali=ed number and no shift is needed

( If the leading one is at bit 97 then the intermediate product is shifted to the right and the e2ponent isincremented b. $

*he shift operation is done using combinational shift

logic made b. multiple2ers Fig > sho3s a simplified logic of a Normali=er that has an > bit intermediate product input and a

< bit intermediate e2ponent input

Fig > Simplified Normali=er logic

(. 20*E$3+11(E$3+1 *ETE&TI10

J/erflo3Ounderflo3 means that the results e2ponent is

too largeOsmall to be represented in the e2ponent field *he

e2ponent of the result must be > bits in si=e% and must be

bet3een $ and (89 other3ise the /alue is not a normali=edone An o/erflo3 ma. occur 3hile adding the t3o e2ponents

or during normali=ation J/erflo3 due to e2ponent addition

ma. be compensated during subtraction of the biasD resulting

in a normal output /alue +normal operation- An underflo3ma. occur 3hile subtracting the bias to form the intermediate

e2ponent If the intermediate e2ponent R C then its an

underflo3 that can ne/er be compensatedD if the intermediatee2ponent C then its an underflo3 that ma. be compensatedduring normali=ation b. adding $ to it

Ghen an o/erflo3 occurs an o/erflo3 flag signal goes

high and the result turns to TInfinit. +sign determined

according to the sign of the floating point multiplier inputs-Ghen an underflo3 occurs an underflo3 flag signal goes

high and the result turns to TKero +sign determined according

to the sign of the floating point multiplier inputs-

,enormali=ed numbers are signaled to Kero 3ith the

appropriate sign calculated from the inputs and an underflo3

flag is raised Assume that E$ and E( are the e2ponents of thet3o numbers A and B respecti/el.D the results e2ponent is

calculated b. +<-

Eresult E$ @ E( 6 $(7 +(-

E$ and E( can ha/e the /alues from $ to (89D resulting in E result

ha/ing /alues from 6$(8 +(6$(7- to )>$ +8C>6$(7-D but for

normali=ed numbers% Eresult can onl. ha/e the /alues from $ to(89 *able III summari=es the E result different /alues and the

effect of normali=ation on it

*ABE III Normali=ation Effect Jn 'esults E2ponent AndJ/erflo3OUnderflo3 ,etection

Eresult &ategory &omments

6$(8 Eresult R C Underflo3 ant be compensated during

normali=ationEresult C Kero Ma. turn to normali=ed number

during

normali=ation +b. adding $ to it-

$ R Eresult R (89 Normali=ed Ma. result in o/erflo3 during

number normali=ation

(88 Eresult J/erflo3 ant be compensated

(I. 680T)E6I6 $ E62+T6

*his design has been implemented using Modelsim and

s.nthesi=ed for !erilog H, *he !erilog code is used for

coding Simulation based /erification is one of the methods

for functional /erification of a design Simulation based/erification ensures that the design is functionall. correct

3hen tested 3ith a gi/en set of inputs *hough it is not full.complete% b. pic0ing a random set of inputs as 3ell as corner

cases% simulation based /erification can still .ield reasonabl.good results

Fig Floating point Multiplier '* top module

8/9/2019 an efficient implementation of modified booth encoder for floating point signed and unsigned numbers

http://slidepdf.com/reader/full/an-efficient-implementation-of-modified-booth-encoder-for-floating-point-signed 6/6

Fig $C Floating point Multiplier output

Fig $$ Floating point Multiplier s.nthesis results using ilin2

,esign Number of slices

AddersOSubtractor s

9inputU*s

BondedIJBs

,ela.

Arra.Multiplier

<)C )( $$97 < <C>ns

BoothMultiplier

$8>( (< (7>$ 7 )<7ns

*ABE I!5 omparison of Multipliers

From the abo/e table% it is clearl. found that the dela.

associated 3ith MBE multiplier is almost <CV less than thedela. of Arra. Multiplier

(II. &10&+26I106 %0* 32T2$E 1$9

*his paper presents an implementation of a floating point

multiplier that supports the IEEE 789 binar. interchange

formatD one of the important aspects of the presented designmethod is that it can be applicable to all 0inds of floating6

point multipliers *he present design is compared 3ith an

ordinar. floating point arra. multiplier and modified Booth

encoder multiplier /ia s.nthesis It sho3s that Booths floating point multiplier is faster than the arra. multiplier% b. seeing

the dela. /alue 3e can 0no3n this factor and po3er

dissipation is also less compare to arra. multiplier *he future

3or0 sho3s it can be implemented for double precisionfloating point multiplier also

(III. $ E3E$E0&E6

:$; IEEE 7896(CC>% IEEE Standard for Floating6Point Arithmetic% (CC>

:(; Mohamed Al6Ashraf.% Ashraf Salem% Gagd. AnisWAn Efficient

Implementation Floating Point MultiplierX% IEEE (C$$

:); 'a/indra P 'a?put & MNShanmu0ha S3am. WHigh speed ModifiedBooth multiplier for signed and unsigned numbersXIEEE (C$(% <96<8)

:9; A , Booth% WA signed binar. multiplication techni4ue%X Quart.

J.Math.% /ol I!% pp ()<L(9C% $8(

:8; S Gallace% WA suggestion for a fast multiplier%X IEEE Tra!. E"#$tr%

&%'put.% /ol E6$)% no $% pp $9L$7% Feb $<9:<; Puneet Paruthi% *an/i "umar%Himanshu Singh% WSimulation of IEEE789

standard ,ouble precision Multiplier using Booth *echni4uesX

IYE'A!ol(% Issue 8% Septmenber(C$(

:7; A ' ooper% WParallel architecture modified Booth multiplier%X Pr%$.

I!t. E"#$tr%i$. E(. )% /ol $)8% pp $(8L$(>% $>>:>; F Elguibal.% WA fast parallel multiplierLaccumulator using the modified

Booth algorithm%X IEEE Tra!. &ir$uit! *!t.% /ol (7% no % ppC(L

C>% Sep (CCC:; Y Fada/i6Arde0ani% WM2N Booth encoded multiplier generator using

Jptimi=ed Gallace trees%X IEEE Tra!. ,#r ar(# *$a"# It#(r. ,*I/*!t.% /ol $%

:$C; ho% YHong% and # hoi% W892896bit 'adi269 multiplier based on

Modified Booth AlgorithmX%$)th AM S.mp!SI%pp())6

()<%Apr(CC)

:$$; A#oldo/s0. and et al% W,esign and implementation of $< b. $< o36 po3er *3os complement MultiplierX In design and Implementation of

AdderOSubtractor and Multiplication units for Floating6Point Arithmetic

IEEE International S.mposium on ircuits and S.stems%8%pp )986

)9>%(CCC