AlGaN/GaN HFET 構造を用いた...

Transcript of AlGaN/GaN HFET 構造を用いた...

-

平成 17 年度修士論文

AlGaN/GaN HFET 構造を用いた Cockcroft-Walton

回路に関する研究

徳島大学大学院工学研究科電気電子工学専攻物性デバイス講座

大野研究室 松田 義和

1

-

平成17年度 修士論文 内容梗概 電気電子工学専攻

研究題目 AlGaN/GaN HFET構造を用いたCockcroft-Walton回路に関する研究

氏 名 松田 義和 [大野研究室]

1.はじめに

破壊電界が高く高移動度のGaNは、良好な絶縁基板に高性能トランジスタが集積可能であり、通信分野だけでな

く、パワーエレクトロニクス分野への応用も検討されている。そこで、同じチップ上にダイオードとトランジスタ

を作製できるAlGaN/GaN HFET構造をショットキーダイオードとして使い、MIMキャパシタと組み合わせ、サフイア基板上に高電圧発生回路であるCockcroft-Walton回路を作成した。 ァ

2.ダイオード特性とコンデンサ特性

ウエハはAlGaN/GaN HFET構造のエピを用い、通常のHFETプロセスで作製

した。チャネル層のシート抵抗は574.5Ω、コンタクト抵抗は1.37Ωmmであった。アノードサイズはL=1μm,W=10μm、電極間距離は3μmである。ダイオードの順方向電流特性は、高電流域で電流飽和が現れた(図1)。この原因はアノード・カソード間の2次元電子ガス層の抵抗による速度飽和のためである。逆方向耐圧は測定装置の都合上100V以上ということまでしか確認できなかった。リーク電流は抵抗値でGΩクラスで、この用途には十分に低い。キャパシタはショットキー電極金属上にプラズマCVD法を用いて100nmの酸化膜を堆積させ、上部にメッキ配線を用いた。サイズがW=0.12μm,H=0.125μmの場合、理論容量値は5.1pFである。しかし1MHzでの測定では8pFとなり、カーボンや水素原子が酸化膜に残留し理想SiO2からずれたためであろう。リーク電流はやはり十分低いが、耐圧は

定より低い40Vであった。 予 3.実験結果

5段Cockcroft-Walton回路のサイズは、面積0.25mm2(W=0.57mm,H=0.45mm)とコンパクトにした。キャパシタ容量は16pF、ダイオードサイズはL=1μm,W=10μmを用いた(図2)。入力電圧を振幅20Vp-pとし、周波数10MHz,1MHz,500kHzにおける負荷依存性ついて測定した。負荷として10MΩ,5MΩ,1MΩの抵抗にオシロスコープの10MΩのプローブを並列接続し、その結果、10MΩのプローブ抵抗と合成抵抗5MΩ,3.3MΩ,0.9MΩに対する出力電圧を測定した。周波数10MHzにおいてすべての負荷に対し出力は約40Vで一定になった。周波数1MHzでは出力は低下し、40Vから抵抗値に対し指数関数的に下がり0.9MΩでは27.2Vとなった。また、周波数500kHzにおける負荷特性は、10MΩ,5MΩ,3.3MΩにおいて40V,37V,34Vとなっ

。しかし、0.9MΩにおいて回路が壊れ測定できなかった。 た 4.考察 負荷依存性の実験結果から、周波数1MHzと周波数500kHzにおける出力電圧は理論値よりも1Vから3V高くなっ

た。これはCockcroft-Walton回路のキャパシタ容量が寄生容量などにより設計値より大きくなったためである。また、周波数10MHzの場合は理論値よりも出力電圧が3V低くなった。こちらは、配線のインダクタンス成分により出

電圧が下がったためである。 力 5.まとめ

AlGaN/GaN HFET構造をショットキーダイオードとして使い、MIMキャパシタと組み合わせることにより集積化5段Cockcroft-Walton回路を作成した。その結果、入力電圧は振幅20Vp-p/周波数10MHzの信号を用いて、出力電圧は40Vとなり、2倍の昇圧に成功した。今後キャパシタの耐圧を向上させ、段数を増加させることで、コンパクトなチップでより高電圧を発生させることができるであろう。

0

2

4

6

8

10

0 2 4 6 8 10

Voltage ( V )C

urre

nt (

mA

)図 1 ダイオード特性

L=1μm

W=10μm

C 1

D 1

D 2

C2

E

D 3 C4

C 3

C 5

D 5

D 4

R

図

16pF

16pF

16pF

16pF

16pF

2 5 段 Cockcroft-Walton 回路

-

目次 第 1 章 序論

1.1 背景 3 1.2 目的 3

第 2 章 AlGaN/GaN HFET ショットキーダイオード特性 2.1 はじめに 4 2.2 基板構造およびプロセスフロー 4 2.3 ダイオードの I-V 特性および周波数特性 5

2.3.1 I-V 特性と周波数特性の実験結果 5 2.3.2 TLM パターン使った I-V 特性の実験結果 6

2.4 シミュレーションによる考察 7 2.4.1 仮想ゲート効果 7 2.4.2 シミュレーションによるモデルフィッティング 7 2.4.3 考察 9

2.5 まとめ 9 第 3 章 Cockcroft-Walton 回路

3.1 はじめに 10 3.2 原理 10 3.3 簡易計算(性能予測) 11 3.4 まとめ 15

第 4 章 AlGaN/GaN Cockcroft-Walton 回路 4.1 はじめに 4.2 基板構造およびマスクパターン 16

4.2.1 基板構造 16 4.2.2 マスクパターン 17

4.3 ダイオードの I-V 特性およびコンデンサの耐圧/周波数特性 18 4.3.1 ダイオードの I-V 特性 18 4.3.2 コンデンサの周波数特性/耐圧特性 18

4.4 実験結果 19 4.5 考察 20 4.6 まとめ 21

第 5 章 まとめ 22 第 6 章 謝辞 参考文献 23

2

-

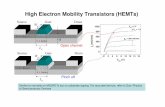

第 1 章 序論 1.1 背景 破壊電界が高く高移動度の GaN は、良好な絶縁基板に高性能トランジスタが集積可能で

あり、通信分野だけでなく、パワーエレクトロニクス分野への応用も検討されている。そ

こで、同じチップ上にダイオードとトランジスタを作製できる AlGaN/GaN HFET 構造のショットキーダイオードに注目した。 1.2 目的 AlGaN/GaN HFET 構造を採用したショットキーダイオードの DC 特性を測定し、その特性を SPICE モデルで解析する。また、MIM キャパシタと組み合わせ、平面回路として集積化 5 段 Cockcroft-Walton 回路を駆動させる。

3

-

第 2 章 AlGaN/GaN HFET ショットキーダイオード特性 2.1 はじめに 破壊電界が高く高移動度の GaN は、良好な絶縁基板に高性能トランジスタが集積可能であり、通信分野だけでなく、パワーエレクトロニクス分野への応用も検討されている。そ

こで、同じチップ上にダイオードとトランジスタを作製できる AlGaN/GaN HFET 構造を採用したショットキーダイオードの DC 特性を測定し、その特性を SPICE モデルで解析した。 2.2 基板構造およびプロセスフロー 実験で使用した AlGaN/GaN エピ結晶は、C 面サファイア基板上に MOCVD 法で成長し

た。(図 2.2.1)カソード(ドレイン、ソース)は電子ビーム蒸着による Ti/Al/Ni/Au を用い、N2 中 850℃でアニールを行った。アノード(ゲート)は電子線蒸着で Ni/Au を蒸着させ、次にプラズマ CVD 法でパッシベ―ション層(SiO2)を 1000Å堆積した(図 2.2.2)。

C-plane Sapphire Sub

i-GaN

i-AlXGa1-X N(x=0.25,t=6nm)n-AlXGa1-XN(Si=4×1018 ,x=0.25,t=12nm)

i-AlXGa1-X N(x=0.25,t=6nm)

Anode

SiO2

CathodeCathode CathodeCathode

C-plane Sapphire Sub

i-GaN

i-AlXGa1-X N(x=0.25,t=6nm)n-AlXGa1-XN(Si=4×1018 ,x=0.25,t=12nm)

i-AlXGa1-X N(x=0.25,t=6nm)

Anode

SiO2

C-plane Sapphire Sub

i-GaN

i-AlXGa1-X N(x=0.25,t=6nm)n-AlXGa1-XN(Si=4×1018 ,x=0.25,t=12nm)

i-AlXGa1-X N(x=0.25,t=6nm)

Anode

SiO2

CathodeCathode CathodeCathode

C-plane Sapphire Sub

i-GaN

i-AlXGa1-X N(x=0.25,t=6nm)n-AlXGa1-XN(Si=4×1018 ,x=0.25,t=12nm)

i-AlXGa1-X N(x=0.25,t=6nm)

Anode

SiO2

図 2.2.1 ダイオード断面構造

オーミック電極形成(電子線蒸着)(Ti/Al/Ni/Au 50/200/40/30nm)

アニール(N2中,850℃,30sec)

素子間分離(RIE)(エッチング深さ:60nm)

アノード電極形成(電子線蒸着)(Ni/Au 80/30nm)

パッシベ―ションSiO2(プラズマCVD)(TEOS:7sccm/O2:300sccm/Heater:300℃/100nm)

ウエットエッチング(BHF,30sec)

金メッキ(メッキ:Au,1.5μm )

オーミック電極形成(電子線蒸着)(Ti/Al/Ni/Au 50/200/40/30nm)

アニール(N2中,850℃,30sec)

素子間分離(RIE)(エッチング深さ:60nm)

アノード電極形成(電子線蒸着)(Ni/Au 80/30nm)

パッシベ―ションSiO2(プラズマCVD)(TEOS:7sccm/O2:300sccm/Heater:300℃/100nm)

ウエットエッチング(BHF,30sec)

金メッキ(メッキ:Au,1.5μm )

図 2.2.2 プロセスフロー

4

-

2.3 ダイオードの I-V 特性および周波数特性 2.3.1 I-V 特性と周波数特性の実験結果 アノード電極と半導体(AlGaN)とのショットキー障壁を利用してダイオードとして使用する。実験に使用した測定 TEG*1のシート抵抗及びコンタクト抵抗は 510 Ω/□、0.6 Ωmm である。また、アノードサイズは L=1μm,W=10μm、電極間距離は 3μm である。ダイオードの I-V 特性は半導体アナライザーを用いて測定した。順方向電流特性は、高電流域で電流飽和が現れた(図 2.3.1)。逆方向電流は、測定装置の都合上 100V 以上となり、低いリーク電流値であった(図 2.3.2)。 *1Test Element Group

順方向電流特性に現れた電流飽和を調べるために、LCR メータを用いてダイオードの周波数特性を調べた。測定条件は、周波数 1kHz~1MHz まで一桁間隔で測定した(図 2.3.3)。その結果、周波数によるコンダクタンスの値に大きな変化はなかった。

0 2 4 6 8 1002468

1012141618

Voltage ( V )

Curre

nt (

mA

)

-100 -50 010-10

10-910-810-710-610-510-410-310-2

Voltage ( V )

Cur

rent

( A

)

図 2.3.1 順方向特性 図 2.3.2 逆方向特性

0 2 4 6 8 100

1

2

3

4

5

6

Voltage ( V )

Con

duct

ance

( m

S ) 1M Hz

100K Hz

10K Hz

1K Hz

L=1μm

W=10μm

0 2 4 6 8 100

1

2

3

4

5

6

Voltage ( V )

Con

duct

ance

( m

S ) 1M Hz

100K Hz

10K Hz

1K Hz

L=1μm

W=10μm

1M Hz

100K Hz

10K Hz

1K Hz

1M Hz

100K Hz

10K Hz

1K Hz

L=1μm

W=10μm

図 2.3.3 周波数特性

5

-

2.3.2 TLM パターン使った I-V 特性の実験結果 2.3.1 の結果を受け、順方向電流特性に現れた電流飽和は速度飽和により引き起こされた

ものか検証するために、アノード無しの TLM*2パターン(図 2.3.4)使った I-V 特性を計測した。TLM パターンは W=100μm、電極間隔(X)を 5μm~30 μm とした。その結果、電流飽和は電極間隔に無関係に現れた(図 2.3.5)。特に電極間隔が 5μm(80mA)の場合と30 μm(40mA)の場合、距離は 6 倍違うが電流値は約半分である。つまり、2DEG*3層における電子が単純な抵抗体によって制御されたのではない。むしろ速度飽和を含んだ FET 特性に近いと思われる。 *2アノード無しの電極間隔を変えたもの *32 次元電子ガス層

0 5 10 150

20

40

60

80

100

Voltage ( V )

Cur

rent

( m

A )

- X = 5μm

- X = 10μm

オーミック電極X

GaN

オーミック電極

SiO2AlGaN

2DEG

オーミック電極X

GaN

オーミック電極

SiO2AlGaN

2DEG

X

GaN

オーミック電極

SiO2AlGaN

2DEGGaN

オーミック電極

SiO2AlGaN

2DEGGaN

オーミック電極

SiO2AlGaN

2DEGGaN

オーミック電極

SiO2AlGaN

2DEG

SiO2AlGaN

2DEG

図 2.3.4 TLM パターン

- X = 15μm

- X = 20μm- X = 25μm- X = 30μm

図 2.3.5 TLM パターン

6

-

2.4 シミュレーションによる考察 2.4.1 仮想ゲート効果 前の 2.3 の結果をふまえて、順方向時に現れた電流飽和は、電極間(アノード、カソード)

での仮想ゲート効果により引き起こされたものと推測した。通常 2DEG 層の電子は、AlGaN層の厚さや誘電率によって制御されるが、この仮想ゲート効果により、2DEG 層より下の基板側で制御されるモデルとした(図 2.4.1)。 仮想ゲート仮想ゲート

Cathode

AlGaN

SiO2

Anode

Cathode

GaN2DEG

Cathode

AlGaN

SiO2

Anode

Cathode

GaN2DEG

図 2.4.1 仮想ゲート効果

2.4.2 シミュレーションによるモデルフィッティング TLMパターンで測定した I-V特性に速度飽和を含むFETモデルでフィッティングした。モデルは MOS モデルを採用し、モデルパラメータは、AlGaN の厚さを 3 分の 1 にし、閾値を通常-6(V)から 3倍の-18(V)した。速度飽和はGaNの代表的な値を入力した(表 2.4.1)。シミュレーション結果は実測値とほぼ同じ結果が得られた(図 2.4.2)。

0 5 10 150

20

40

60

80

100

Voltage ( V )

Cur

rent

( m

A )

― Experiment○ Simulation

from 5μm to 30μm

step 5μm

0 5 10 150

20

40

60

80

100

Voltage ( V )

Cur

rent

( m

A )

― Experiment○ Simulation

0 5 10 150

20

40

60

80

100

Voltage ( V )

Cur

rent

( m

A )

― Experiment○ Simulation

from 5μm to 30μm

step 5μm

図 2.4.2 TLM フィティング

パラメータ 値 単位

LEVEL: 3

Variable μm L:

10 μm W:

-18 V Vth:

mA/V2 KP: 110

μ0: 2000 cm2/v・s

Vsat:

2×107

cm/s

Rd,Rs: 6 Ω

表 2.4.1 モデルパラメータ

7

-

次に、ダイオードの飽和特性を表現するため、ダイオードと FET を組み合わせた回路モデルを作成した(図 2.4.3)。モデルパラメータは、先の TLM パターンで速度飽和を含む FETモデルを採用した(表 2.4.2)。SPICE モデルと実測値とのフィッティング結果を示す(図2.4.4)。 その結果 DC 特性は実測値と一致することが確認できた。

表 2.4.2 SPICE モデル

図 2.4.3 ダイオードモデル

FET DIODE パラメータ 値 単位 パラメータ 値 単位

n: 4 LEVEL: 3 IS: 4n A L: 3 μm

RS: 50 Ω W: 10 μm RL: 200Meg Ω KP: 110 μΑ

m0: 2000 cm2/v・s

Vsat: 2×107 cm/s

RS: 60 Ω

0 2 4 6 8 1002468

1012141618

Voltage ( V )

Curre

nt (

mA

)

― Experiment ○ Simulation

図 2.4.4 ダイオードフィッテング

8

-

2.4.3 考察 ダイオードの順方向時の電流飽和は、仮想ゲート効果により引き起こされた。そのため

SPICE モデルでは、ダイオードと仮想ゲート効果を表すために速度飽和を含む FET を組み合わせることにより実測値と良くあった。 2.5 まとめ AlGaN/GaN HFET ショットキーダイオード特性(DC 特性)について調べた。その結果逆方向特性に優れリーク電流も低くかった。一方で、順方向電流に現れた電流飽和(非線

形抵抗)は、アノード電極とカソード電極間での仮想ゲート効果により引き起こされてい

た。上記の観点より、ショットキーダイオード特性(DC 特性)は、順方向電流に制限はあるが整流素子として機能することが確認できた。

9

-

第 3 章 Cockcroft-Walton 回路 3.1 はじめに Cockcroft-Walton 回路は J.D.Cockcroft と E.T.S.Walton が、水素イオンの加速装置用電源を作るために考案した回路である。近年は、高電圧回路としての用途だけでなく、半導

体技術が進歩するにつれ、小型の DC-DC コンバータや LED の駆動回路と多岐に渡り応用が進められている。本研究はサファイア基板上の AlGaN/GaN HFET 構造をショットキーダイオードとして使い、MIM キャパシタと組み合わせ、平面回路として集積化Cockcroft-Walton 回路を駆動させることである。そのためこの章では、Cockcroft-Walton回路の原理や性能予測について説明する。 3.2 原理 Cockcroft-Walton 回路はコンデンサを直列に積み上げることが特徴である。その動作原理を説明するのにあたり 2 段 Cockcroft-Walton 回路を例にあげる。図 3.2.1 に示すようにダイオードとコンデンサが対をなし 2 組から成り立っている。この場合、無負荷時においてコンデンサ C1は波高値 E に充電され、コンデンサ C2は電源からコンデンサ C1を通して2E に充電される。しかし負荷電流を得る場合、コンデンサに充電される電荷は均一にならない。そ

の基本動作は、電源周波数 1 周期内において、負荷に要求する電荷を Q クーロンとした場合、コン

デンサ C2が放電する電荷量も Q クーロンである。そのため、コンデンサ C2の線間電圧は Q クーロンの放電傾きを持つ。一方で失った電荷 Q クーロン

は、コンデンサ C1から同じだけの電荷をコンデンサ C2 に充電する。しかし、コンデンサ C2 の線間電圧は電源からコンデンサ C1 を通して充電されるため、無負荷時に比べ Q/ C1 下がった値になる(図 3.2.2)。このように負荷電流を Cockcroft-Walton 回路から得る場合、相当な脈動が現れる。

C1

D1

D2

C2

R

E

図 3.2.1 2段 Cockcroft-Walton回路

10

-

t

入力電圧( V ) t4t3t2t1

E

1

2CQE −

2CQ

21

2CQ

CQE −−

t

t

E

1CQ

1CQE −

C1の線間電圧( V )

C2の線間電圧( V )

22CQ

放電 充電 充電

充電 充電放電 放電

3.3 簡易計算(性能予測) 実際に設計した 5 段 Cockcroft-Walton 回路の計算導出を説明する。また、その計算式から簡易計算を行い性能予測をする。 5 段 Cockcroft-Walton 回路は、ダイオードとコンデンサが対をなし 5 組から成り立っている(図 3.2.3)。基本動作は、電源周波数 1 周期内において負荷に要求する電荷を Q クーロンとした場合、コンデンサ C1、コンデンサ C3、コンデンサ C5 の直列放電により供給されている。そのためコンデンサ C5、コンデンサ C3、コンデンサ C1の線間電位は Qクーロンの放電傾きを持つ。一方で、コンデンサ C4 から失った電荷 Q クーロンはコンデンサ C5に充電される。コンデンサ C4 が失った電荷 Q クーロンは、コンデンサ C3より充電される。しかし、コンデンサ C3は負荷へ Q クーロン放電しているため、2Q クーロンの放電量となる。失った電荷 2Q クーロンは、コンデンサ C2 からコンデンサC3へ充電される。同様に、失った電荷 2Q クーロンはコンデンサ C1からコンデンサ C2へ充電される。しかし、コンデンサ C1 は負荷へ Q クーロン放電しているため、3Q クーロンの放電量となる(図 3.2.4)。

図 3.2.2 2 段 Cockcroft-Walton 回路論理波形

C1

D 1

D 2

C2

E

D 3 C4

C3

C5

D 5

D 4

R

図 3.2.3 5 段 Cockcroft-Walton 回路

11

-

t

入力電圧( V ) t4t3t2 t1

E

t

t

12CQ

C2の線間電圧( V )

t

C1の線間電圧( V )

E 1

2CQ

1

3CQE −

1

3CQ

2

2CQ

21

2252

CQ

CQE −− 12

52CQE −

C5の線間電圧( V )

5CQ

52CQ

C3の線間電圧( V ) 3CQ

3

2CQ

C4の線間電圧( V )

t

4CQ

t

21

2252

CQ

CQE −−

32CQ

321

22252

CQ

CQ

CQE −−−

321 232

252

CQ

CQ

CQE −−−

4321 232

252

CQ

CQ

CQ

CQE −−−−

4321 232

252

CQ

CQ

CQ

CQE −−−−

54321 232

252

CQ

CQ

CQ

CQ

CQE −−−−−

図 3.2.4 5 段 Cockcroft-Walton 回路論理波形

12

-

図3.2.4論理波形から5段Cockcroft-Walton回路の計算式は、コンデンサC1の線間電圧、コンデンサ C3の線間電圧、コンデンサ C5の線間電圧を足し合わせ*1ダイオードの閾値*2を引いた値になる。 *1コンデンサの線間電圧は平均値を使った。 *2ダイオードの閾値は一定の Vthを使った。

thVQCQ

CQ

CQ

CQ

CEV 5)11

254

213(5

543215 −++++−= 式(3.1)

電源周波数 1 周期内において負荷に要求する電荷 Q クーロンは、負荷電流を電源周波数で割った値となる。

RfV

Q 5= 式(3.2)

ここで、コンデンサの容量はすべて同じと仮定し、式 3.1、式 3.2 を用いて、5 段Cockcroft-Walton 回路の計算式は

CRf

VEV th

5.141

)(55

+

−= 式(3.3)

となる。 簡易計算は、式 3.3 を使って周波数/負荷特性を計算した。計算に用いた値は、交流電圧10V、閾値 1V、コンデンサ 16pF とした。その結果、電源周波数が 10MHz、1MHz、500kHzでは、負荷電流が大きくなるにつれて指数関数的に電圧が下がっている。これは電源周波

数 1 回に充放電する電荷が低周波になるにつれて大きくなるためである(図 3.2.5)。

0

10

20

30

40

50

60

0.5 2.5 4.5 6.5 8.5

Load ( Ω )

Vol

tage

( V

)

[×106]

10M Hz1M Hz

500k Hz

100

10

20

30

40

50

60

0.5 2.5 4.5 6.5 8.5

Load ( Ω )

Vol

tage

( V

)

[×106]

10M Hz1M Hz

500k Hz

10

図 3.2.5 周波数/負荷特性

13

-

次に負荷電流を横軸にとり、その傾きから周波数による内部インピーダンスの変化を求

めた。その結果、電源周波数 10MHz, 1MHz, 500kHz で内部インピーダンスは、90kΩ、900kΩ, 1.6MΩとなった(図 3.2.6)。つまり、コンデンサ容量が決まれば、内部インピーダンスは電源周波数に反比例する。

0

10

20

30

40

50

60

0.E+00 1.E-05 2.E-05 3.E-05

Load Current ( A )

Vol

tage

( V

)

10M Hz 5段 Cockcroft-Walton回路の最大性能は電源周波数で決まる。ダイオード抵抗値は 100

Ω、コンデンサ容量は 10pF の場合における最大駆動周波数は、

)1010(100 12−××=×= CRDτ 式(3.4)

6max 105020

1×==

τf ( Hz ) 式(3.5)

となる。最大駆動周波数 50MHz での負荷特性は、約 600kΩまでは定電流特性特性をとる(図 3.2.7)。また、内部インピーダンスは 29kΩとなった(図 3.2.8)。負荷効率を 90%として駆動させた場合の性能予測は、負荷抵抗 300kΩで出力電圧 41V、負荷電流 0.13mA となる。

500k Hz

1M Hz

図 3.2.6 内部インピーダンス

0

10

20

30

40

50

60

0 1 2 3 4 5Load ( Ω )

Vol

tage

( V

)

[×106]

0.1

50M Hz

図 3.2.7 負荷特性

0

10

20

30

40

50

60

0.E+00 1.E-04 2.E-04 3.E-04

Vol

tage

( V

Load Current ( A )

)

50M Hz

14 図 3.2.8 内部インピーダンス

-

3.4 まとめ Cockcroft-Walton 回路は、負荷電流を得るにつれて指数関数的に電圧は下がる。また、内部インピーダンスは、コンデンサ容量と電源周波数の積によってきまる。今回設計した 5段 Cockcroft-Walton 回路の最大性能は、コンデンサの容量を全て 10pF と仮定し、ダイオード抵抗/閾値を 100Ω/1V として最大性能を計算した。その結果、入力は交流電圧 10V/周波数 50MHz で、負荷効率 90%のとき出力電圧 41V/負荷電流 0.13mA となった。

15

-

第 4 章 AlGaN/GaN Cockcroft-Walton 回路 4.1 はじめに この章では、サファイア基板上の AlGaN/GaN HFET 構造をショットキーダイオードとして使い、MIM キャパシタと組み合わせ Cockcroft-Walton 回路として駆動させた。 4.2 基板構造およびマスクパターン 4.2.1 基板構造 実験で使用した AlGaN/GaN エピ結晶は、C 面サファイア基板上に MOCVD 法で成長した(図 4.2.1)。カソード(ドレイン、ソース)は Sputter による Ti/Al/Ti/Au を用い、N2 中850℃でアニールを行った(図 4.2.2)。アノード(ゲート)は Sputter で Ni/Au/Ti を堆積させた。次にコンデンサを作るため、酸化膜層(SiO2)はプラズマ CVD 法で 1000Å堆積させ、O2中 600℃でアニールを行った後、電界メッキ法を用いて金メッキをした(図 4.2.3)。

CathodeCathode

i-AlXGa1-XN(x=0.25,t=6nm)

Anode

SiO2

1μm3μm 3μm

CathodeCathode CathodeCathode

C-plane Sapphire Sub

u- GaN

C-plane Sapphire Sub

GaNu-AlXGa1-XN(x=0.24,t=12nm)

Anode

SiO2

3μm 3μm

(t=3000nm)

CathodeCathode CathodeCathode

i-AlXGa1-XN(x=0.25,t=6nm)

Anode

SiO2

1μm3μm 3μm

CathodeCathode CathodeCathode

C-plane Sapphire Sub

u- GaN

C-plane Sapphire Sub

GaNu-AlXGa1-XN(x=0.24,t=12nm)

Anode

SiO2

3μm 3μm

(t=3000nm)

酸化膜熱処理(RTA O2 600℃ 10min)

オーミック電極形成(Sputter Ti/Al/Ti/Au )

オーミックアニール(RTA N2 850℃ 30sec)

素子間分離(RIE BCl3 60~70nm)

酸化膜堆積(TEOS PE-CVD 100nm)

スルーホールエッチング(BHF 1min)

配線(電解金メッキ)

アノード電極形成(Sputter Ni/Au/Ti = 60/30/10nm)

酸化膜熱処理(RTA O2 600℃ 10min)

オーミック電極形成(Sputter Ti/Al/Ti/Au )

オーミックアニール(RTA N2 850℃ 30sec)

素子間分離(RIE BCl3 60~70nm)

酸化膜堆積(TEOS PE-CVD 100nm)

スルーホールエッチング(BHF 1min)

配線(電解金メッキ)

アノード電極形成(Sputter Ni/Au/Ti = 60/30/10nm)

オーミック電極形成(Sputter Ti/Al/Ti/Au )

オーミックアニール(RTA N2 850℃ 30sec)

素子間分離(RIE BCl3 60~70nm)

酸化膜堆積(TEOS PE-CVD 100nm)

スルーホールエッチング(BHF 1min)

配線(電解金メッキ)

アノード電極形成(Sputter Ni/Au/Ti = 60/30/10nm)

図 4.2.1 ダイオード断面構造

sio2u-GaN

金メッキAnode

sio2u-GaN

金メッキAnode

sio2u-GaN

金メッキAnode 図 4.2.2 プロセスフロー

図 4.2.3 コンデンサ断面構造

16

-

4.2.2 マスクパターン Cockcroft-Walton 回路はダイオードとコンデンサから成り立っている。そこでマスクパターンは、面積を小さくすると同時にプロセス工程を短くするため、コンデンサの下地金

属をアノード金属にした。これによりダイオード(アノード金属)とコンデンサ(下地金

属)の両方を兼用することになり面積効率(配線不要)が良くなった。また、コンデンサ

の金メッキ(上地金属)と下地金属がショートするのを防ぐため、エアーブリッジを用い

て、コンデンサ間の結線(直列接続)、カソードとコンデンサ間との結線を行った。ダイオ

ード形状については、アノード長(ゲート長)はリーク電流を小さくするため、1μm とした。 図 4.2.4 に実際に設計した 5 段 Cockcroft-Walton 回路*1のマスクパターンを示す。回路自体の面積は 0.25mm2(W=0.567mm,H=0.445mm)とコンパクトにした。コンデンサの面積は 0.031mm2(W=0.25mm,H=0.125mm)、ダイオード形状は L=1μm(ゲート長)、W=10μm(ゲート幅)である。 *1等価回路は 3 章 3 を参照

図 4.2.4 Cockcroft-Walton 回路のマスクパターン

コンデンサ C5

ダイオード

pad

エアーブリッジ

エアーブリッジ

pad

pad

pad

入力

出力

アース

コンデンサ C4

コンデンサ C3 コンデンサ C2

コンデンサ C1 ダイオード

アンプ部分

17

-

4.3 ダイオードの I-V 特性およびコンデンサの耐圧/周波数特性 4.3.1 ダイオードの I-V 特性 実験に使用したチップのシート抵抗及びコンタクト抵抗は 574.5 Ω/□、1.37 Ωmm である。また、アノードサイズは L=1μm,W=10μm、電極間距離は 3μm である。ダイオードのI-V 特性は半導体アナライザーを用いて測定した。順方向電流特性は、高電流域で電流飽和が現れた(図 4.3.1)。この原因はアノード・カソード間の 2 次元電子ガス層の抵抗による速度飽和のためである。逆方向電流は、測定装置の都合上 100V 以上となり、極めて低いリーク電流値(リーク抵抗:ギガΩ)であった(図 4.3.2)。 4.3.2 コンデンサの周波数特性/耐圧特性

0

2

4

6

8

10

0 2 4 6 8 10

Voltage ( V )

Cur

rent

( m

A )

図 4.3.1 順方向特性

1.E-11

1.E-09

1.E-07

1.E-05

1.E-03

1.E-01

-100 -80 -60 -40 -20 0

Voltage ( V )

Cur

rent

( A

)

10

図 4.3.2 逆方向特性

実験に使用したコンデンサは、TEOS 原料からプラズマ CVD 法を用いて、酸化膜(SiO2)を 100nm 体積させた。コンデンササイズは W=0.12mm,H=0.125mm で理論値は 5.1pF である。コンデンサの周波数特性および I-V 特性は、LCR メータと半導体アナライザーを用いて測定した。その結果、周波数特性は 8pF と理論値から約 1.5 倍大きくなっている(図4.3.3)。この原因は、TEOS 原料に含まれるカーボンや水素原子が酸化膜に混入し、誘電率が大きくなったためであろう。耐圧特性は40Vで極めて低いリーク電流であった(図4.3.4)。また、耐圧特性は膜質の改善により更なる改善が期待できる。

0

2E-12

4E-12

6E-12

8E-12

1E-11

3 5 7 9

Frequency ( Hz )

Cap

acita

nce

( F )

[ ×105 ]

10

0.E+00

1.E-10

2.E-10

3.E-10

4.E-10

5.E-10

6.E-10

0 10 20 30 4

Voltage ( V )

Cur

rent

( A

)

0

図 4.3.3 周波数特性 図 4.3.4 耐圧特性 18

-

4.4 実験結果 実験に使用した 5段Cockcroft-Walton回路のコンデンサ容量は全て 16pFである。また、ダイオードの I-V 特性およびコンデンサ特性は 4.3 で説明した。入力電圧はファンクションジェネレーターを用いて、交流電圧 10V/周波数 10MHz である。負荷はオシロスコープの10MΩのプローブを利用して測定した。その結果、出力電圧は 41.6V でリプル電圧はピーク・ツー・ピーク 100mV であった(図 4.4.1、図 4.4.2)。

図 4.4.1 10MΩ/10MHz 出力電圧

入力電圧

出力電圧

図 4.4.2 10MΩ/10MHz リプル電圧

入力電圧

リプル電圧 負荷抵抗 1MΩにオシロスコープの 10MΩのプローブを並列接続し、合成抵抗 0.9MΩの状態で測定した。その結果、入力電圧 10V/周波数 1MHz の場合の出力電圧は 27V であった(図 4.4.3)。また、リプル電圧はピーク・ツー・ピーク 2V となった(図 4.4.4)。これは負荷電流を得るにつれて、定電流特性が低下し、リプル電流が大きくなったためである。

図 4.4.3 0.9MΩ/1MHz 出力電圧

入力電圧

出力電圧

入力電圧

リプル電圧 図 4.4.4 0.9MΩ/1MHz リプル電圧

19

-

5 段 Cockcroft-Walton 回路のサイズは、面積 0.25mm2(W=0.567mm,H=0.445mm)とコンパクトにした。キャパシタ容量は 16pF、ダイオードサイズは L=1μm,W=10μm を用いた。入力電圧を振幅 20Vp-pとし、周波数 10MHz,1MHz,500kHz における負荷依存性ついて測定した。負荷として 10MΩ,5MΩ,1MΩの抵抗にオシロスコープの 10MΩのプローブを並列接続し、その結果、10MΩのプローブ抵抗と合成抵抗 5MΩ,3.3MΩ,0.9MΩに対する出力電圧を測定した。周波数 10MHz においてすべての負荷に対し出力は約 40V で一定になった。周波数 1MHz では出力は低下し、40V から抵抗値に対し指数関数的に下がり 0.9MΩでは 27.2V となった。また、周波数 500kHz における負荷特性は、10MΩ,5MΩ,3.3MΩにおいて 40V,37V,34V となった。しかし、0.9MΩにおいて回路が壊れ測定できなかった。これは負荷電流を得るにつれて、定電流特性が低下しキャパシタからダイオードに流

れる瞬時電流が大きくなり、ダイオードが壊れたためであろう(図 4.4.5)。

0

10

20

30

40

50

60

0.5 2.5 4.5 6.5 8.5

Load ( Ω )

Vol

tage

( V

)

[×106]

1MHz -理論値 △ 実測値

10MHz -理論値 ○ 実測値

500kHz

-理論値 □ 実測値

10

図 4.4.5 周波数/負荷特性

4.5 考察 負荷依存性の実験結果から、周波数 1MHz と周波数 500kHz における出力電圧は理論値よりも 1V から 3V 高くなった。これは Cockcroft-Walton 回路のキャパシタ容量が寄生容量などにより設計値より大きくなったためである。また、周波数 10MHz の場合は理論値よりも出力電圧が 3V 低くなった。こちらは、配線のインダクタンス成分により出力電圧が下がったためである。 *2理論値の計算については 3 章 3 を参照

20

-

4.6 まとめ AlGaN/GaN HFET 構造をショットキーダイオードとして使い、MIM キャパシタと組み合わせることにより集積化 5 段 Cockcroft-Walton 回路として駆動させた。その結果、入力電圧は振幅 20Vp-p/周波数 10MHz の場合、出力電圧は 40V となり 2 倍昇圧に成功した。

21

-

第 5 章 まとめ AlGaN/GaN HFET ショットキーダイオード特性(DC 特性)について調べた。その結果逆方向特性に優れリーク電流も低くかった。一方で、順方向電流に現れた電流飽和(非線

形抵抗)は、アノード電極とカソード電極間での仮想ゲート効果により引き起こされてい

た。上記の観点より、ショットキーダイオード特性(DC 特性)は、順方向電流に制限はあるが整流素子として機能することが確認できた。 AlGaN/GaN HFET 構造をショットキーダイオードとして使い、MIM キャパシタと組み合わせることにより集積化 5 段 Cockcroft-Walton 回路として駆動させた。その結果、入力電圧は振幅 20Vp-p/周波数 10MHz の場合、出力電圧は 40V となり 2 倍昇圧に成功した。

22

-

23

第 6 章 謝辞 参考文献 謝辞 本研究を行うにあたり、終始懇切なるご指導とご鞭撻をいただきました大野泰夫教授お

よび敖金平先生に心より感謝いたします。 本研究を行うにあたり、適切な御指導とご教示を賜りました徳島大学工学部電気電子工

学科 酒井士郎 教授、富永喜久雄 助教授、直井美貴 助教授、西野克志 助教授、稲岡武 技官に深く感謝します。 最後に菊田大悟氏、岡田政也氏、高木亮平氏をはじめとした大野研究室の皆様に感謝い

たします。 参考文献 HIGH VOLTAGE LABORATORY TECHNIQUE p21~p31 著者 J.D CRAGGS AND J.M.MEEK

出版 LONDON BUTTERWORTHS SGIENTIFIC PUBLICATIONS 1954 図書館書庫 54138 G1-1

回路シミュレーション技術と MOSFET モデリング 著者 盛健次 三浦道子 名野隆夫

現代 高電圧工学 p204~p206 編著者 家田正之

現代電気工学講座 高電圧工学 p172~p177 著者 中野義映 石橋鐐造 野田達哉