Abstract of “Switching Activity Analysis and Optimization ...

Transcript of Abstract of “Switching Activity Analysis and Optimization ...

Abstract of “Switching Activity Analysis and Optimization Methods for Promoting

Functionally Appropriate Test and Delay Characterization in Digital Integrated Circuits”

by Elif Alpaslan, Ph.D., Brown University, May 2011

This dissertation utilizes Design for testability, DFT-, and automatic test pattern

generation, ATPG-based, techniques to overcome various problems that are caused by

the non-functional switching activity of the circuit during scan-based test. Switching

activity discrepancies between a circuit’s functional and test modes are problematic for a

variety of reasons. When switching activity is excessive, it may damage chips or cause

working parts to be considered defective—leading to yield loss. In other cases, very low

switching activity during test may lead to test escapes. In this dissertation, the

characteristics and the nature of the hazardous switching activity have been studied

during circuit’s test and functional mode. A quantitative comparison of the amount and

the profile of the switching activity for different modes of operation has been performed.

Motivated by the outcomes of our activity analysis for scan shift, we developed a

DFT-based technique which relies on inserting extra test points to a subset of the flip-

flops in the verified circuit such that the transitions at the outputs of these selected flip-

flops will be blocked from propagating to the combinational parts of the design. The

proposed technique modifies the circuit at register-transfer level, RTL, such that the

timing violations due to the inserted extra hardware will be handled by the synthesis tool.

With the proposed method, the excessive switching activity during the shift cycles of the

scan test will be reduced with an insignificant area overhead.

We also developed a noise index model, NIM, which can be effectively used to

capture the effects of the excessive switching activity around a critical path during the

launch clock cycle on the delay of the path. We have validated the effectiveness of our

noise index model on an industrial size circuit to estimate the delay discrepancies

between the silicon measurements and pre-silicon simulation estimations.

We then used our noise index model for high-quality path delay pattern

generation by utilizing the large fraction of the don’t care bits in the test cubes. Through

our noise index model based X’filling method, we replicated the worst observed

functional switching activity profile around the critical path of interest. We used this

model to overcome the over-testing and under-testing problems of the path delay test.

Switching Activity Analysis and Optimization Methods for Promoting Functionally

Appropriate Test and Delay Characterization in Digital Integrated Circuits

by

ELIF ALPASLAN

B.S. Sabanci University, 2005

Sc. M. Brown University, 2007

A Dissertation submitted in partial fulfillment of the requirements for

the Degree of Doctor of Philosophy

in the Division of Engineering at Brown University

Providence, Rhode Island

May 2011

iii

This dissertation by Elif Alpaslan is accepted in its present form by

the Division of Engineering as satisfying the

dissertation requirement for the degree of

Doctor of Philosophy

Date_____________ ______________________________________________ Jennifer Lynn Dworak, Director

Recommended to the Graduate Council

Date_____________ ___________________________________________ Iris Bahar, Reader

Date_____________ ___________________________________________ Desta Tadesse, Reader

Approved by the Graduate Council

Date_____________ ___________________________________________ Peter M. Weber, Dean of the Graduate School

iv

The Vita of Elif Alpaslan

Elif Alpaslan was born in Istanbul, Turkey on February 10, 1981. Upon completion of

high school, her undergraduate education took place at Sabanci University in Istanbul,

Turkey where only the top 0.5% of students taking the nationwide University Entrance

Exam were considered for admission to this university. She graduated from Sabanci

University in June 2005 with a B.S.E.E in Microelectronics Engineering. Shortly after

graduation, she received a Brown University Graduate Fellowship and arrived at Brown

University in September 2005. At Brown University, she joined the Laboratory for

Engineering Man/Machine Systems (LEMS) group as a research assistant, advised by

Professor Jennifer Dworak. She was awarded a Design Automation Conference (DAC)

Graduate Fellowship in July 2006. She completed the requirements for a Sc.M in

Engineering in 2007 at Brown University. She completed an engineering internship at

Mentor Graphics Corporation in Marlboro, MA in the summer of 2007. Her work during

this internship was published in VLSI Test Symposium (VTS) in 2008 and in IEEE

Transactions on Computer-Aided Design of Integrated Circuits and Systems in 2010. She

completed her second engineering internship at NXP Semiconductors in Eindhoven,

Netherlands between 2008 and 2009. Her work during this internship was published in

the proceedings of Design and Test in Europe (DATE).

.

v

Acknowledgements

I would like to express my most sincere appreciation to my advisor Jennifer Dworak at

Brown University. During this long journey she has been a great advisor to me in terms

of her scientific creativeness and her kind and understanding personality. Also special

thanks goes to my dissertation committee members, Professor Iris Bahar and Dr. Desta

Tadesse. I would also like to thank to the past and current members of our laboratory,

Kundan Nepal, Cesare Ferri, Yiwen Shi, Nuno Alves, Roto Lee and Octavian Biris for

their support and their friendship.

A very special thanks goes to my undergraduate advisor Ilker Hamzaoglu, for being

helpful in my decision process to continue with my education and become a PhD. His

VLSI classes and projects were the reason for my decision to continue my academic life

in the VLSI area.

I would like to thank my advisor Dr. Yu Huang at Mentor Graphics for giving me the

engineering internship opportunity at Mentor Graphics and for his feedback in our

project. I also want to acknowledge Dr. Ananta K. Majhi, Dr. Bram Kruseman and Paul

van de Wiel for being my advisors during my internship at NXP Semiconductors. The

quality of my project at NXP was significantly enhanced by their assistance.

Special thanks goes to James Eakin, and his parents Diane and James Eakin who have

been like a second family to me in the United States due to their support and love.

Finally, a very special thanks goes to my sister Ece Alpaslan and my parents Aynur and

Bayram Alpaslan for their never-ending love and support, and for always believing in

me. I would not have accomplished any of this without them.

1

Contents

Chapter 1 Introduction 7

1.1 Main Contributions ………………………………………………………….13

1.2 Organization of the Dissertation …………………………………...………..15

Chapter 2 Background 16

2.1 Scan-based Test ……………………………………………………………..19

2.2 Overhead of Scan-based Test ………………………………………………..21

2.3 Fault Models ………………………………………………………………...23

2.3.1 Stuck-at Faults …………………………………………………….23

2.3.2 Transition Delay Faults ……………………………………………26

2.3.3 Path Delay Faults ………………………………………………….28

2.4 Scan-based Delay Testing …………………………………………………...29

Chapter 3 Power Dissipation during Test 32

3.1 Test Power Reduction Techniques …………………………………………..33

3.1.1 ATGP-based Approaches ………………………………………….33

3.1.2 DFT-based Approaches …………………………………………...35

3.2 Comparison of the Switching Activity during Test and Functional Modes ...38

3.3 Power Sensitive Scan Cell Identification ……………………………………43

3.3.1 Signal Probability Approach ………………………………………43

3.3.2 TRR – Toggling Rate Reduction Metric …………………………..45

2

3.4 RTL Modification for Scan Shift Activity Reduction ………………………47

3.4.1 Identifying Power-Sensitive RTL Bits …………………………….49

3.4.2 Freezing Power-Sensitive RTL Bits ………………………………50

3.5 Experimental Results ………………………………………………………..55

3.5.1 Actual Shift Power Reduction …………………………………….56

3.5.2 Area Overhead of the Freeze Modification ……………………….61

3.5.3 Computational Complexity ………………………………………………..61

3.6 Summary …………………………………………………………………….63

Chapter 4 Unexpected Timing on Silicon 65

4.1 Delay Discrepancies between Silicon and Simulation ………………………67

4.2 Path Delay Measurements vs SPICE-Level Timing Analysis ………………69

4.3 The Noise Index Model ……………………………………………………..75

4.4 Flow for the Noise Index Model …………………………………………….81

4.5 Correlation between NIM and Delay Difference between Design Simulation

and Silicon ………………………………………………………………………82

4.6 Summary …………………………………………………………………….84

Chapter 5 High-quality At-speed Testing 85

5.1 High-quality Test Pattern Generation and Manipulation Techniques ………87

5.1.1 Pseudo-Functional Test ……………………………………………88

5.1.2 Power Supply Noise Aware Pattern Generation …………………..89

5.2 Noise Index Analysis for Functional and Test Modes ………………………90

3

5.3 NIM-X: NIM-based X-filling Algorithm …………………………………..100

5.4 Experimental Results ………………………………………………………105

5.5 Summary …………………………………………………………………...108

Chapter 6 Conclusion 110

4

List of Figures

Figure 2-1: The difference between the D-type flip flop and MUX-based scan flip

flop……………………………………………………………………………………20

Figure 2-2: Scan inserted design…………….………………………………….........21

Figure 2-3: Stuck-at fault example……… ………….……………………………….24

Figure 2-4: Stuck-at test timing scheme……………………………………………..18

Figure 2-5: Timing behavior for LOC delay test………………………………….….30

Figure 2-6: Timing behavior of LOS delay test………………………………………31

Figure 3-1: Simulation flow for functional inputs ………………….…………...…...39

Figure 3-2: Analysis flow for test patterns generated by ATPG……………………...41

Figure 3-3: Signal Probability Calculation……………………...……………………44

Figure 3-4: Procedure for calculating TRR………………………………………….. 46

Figure 3-5: Original Circuit…………………………………………...……………...48

Figure 3-6: Circuit after inserting an additional gate…………………………………48

Figure 3-7: Example of RTL modification in VHDL………………………………...52

Figure 3-8: Example of RTL modification in Verilog………………………………..53

Figure 3-9: Complete design flow with the proposed freeze modification method…..54

Figure 3-10: Total number transitions at the combinational gate outputs for the

unmodified and modified copies of the Ckt1…………………………...…………….57

Figure 3-11: Total number transitions at the combinational gate outputs for the

unmodified and modified copies of the Ckt2 ...…………………...……………….....58

5

Figure 3-12: Effect of the XOR/XNOR gates to the switching activity reduction ......59

Figure 4-1: Correlation between expected and measured path delays ……………….71

Figure 4-2: Switching activity profile of two different paths at launch cycle………..73

Figure 4-3: Switching activity profile of two slower than expected paths at launch

cycle…………………………………………………………………………………..74

Figure 4-4: Switching activity area of interest for the noise index model …………...77

Figure 4-5: Triangular shaped current profile ………………………………………..78

Figure 4-6: Voltage drop profile vs radius ……………………………………...……79

Figure 4-7: Flow for the noise index analysis ………………………………..………82

Figure 4-8: Delay difference vs. noise index values………………………………….83

Figure 5-1: Flow for VCD and DEF files generation …………………….……..…...91

Figure 5-2: Location of the robustly-detected critical paths …..…………..……...….97

Figure 5-3: Spatial activity profile for region 1 …………..…………..…..…...……98

Figure 5-4: Spatial activity profile for region 7 .…………………..……..…………99

Figure 5-5: Spatial activity profile for region 8 .……………………………………100

Figure 5-6: The NIM difference of the paths between functional and test modes…..102

Figure 5-7: Proposed NIM-based X-filling Method…………………...….………...103

Figure 5-8: NIM difference between path delay test vectors and functional patterns for

No-Fill and NIM-Fill for color converter benchmark……………………………….105

Figure 5-9: NIM difference between path delay test vectors and functional patterns for

No-Fill and NIM-Fill for FPU benchmark…………………………………………..106

6

List of Tables

Table 3-1 Average Number of Transitions per Clock Cycle during Functional

Operation…………………………………………………………………………….. 40

Table 3-2 Average Number of Transitions per Clock Cycle for ATPG Patterns…….42

Table 3-3 Characteristics of the Circuits…….………………………………………..55

Table 3-4 Actual Reduction in Switching Activity at Combinational Part of the Circuit after Freezing Power-Sensitive Scan Cells………………………………...…………60

Table 3-5 Area Overhead of the Freeze Modification………………………………. 61

Table 5-1 Average and Maximum Number of Transitions during Functional

Operation……………………………………………………………………………...93

Table 5-2 Average Number of Transition during the Path Delay Test Mode….……..94

Table 5-3 The Average of the Absolute Values of NIM Differences for Different Fill

Options………………………………………………………………………………107

7

Chapter 1

Introduction

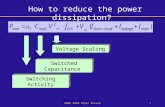

In 1965, Gordon Moore predicted that the total number of transistors that can be placed

on a single chip would double every two years [1]. Since then, the semiconductor

industry has poured significant resources into making that prediction come true. The

switching speed of the transistors has increased, and smaller device sizes have enabled

the designers to fit more transistors into the same area. This has lead to exponential

increases in performance. At the same time, because today’s chips experience more

simultaneous switching per unit area, there has been a dramatic increase in the power

densities of today’s high performance designs.

As a result, reducing power dissipation and power supply switching noise has become

an important design consideration in current system-on-a-chip (SoC) designs [5]. High

power dissipation leads to shorter battery lifetimes and requires expensive

cooling/packaging methods. Switching activity can also alter the delay characteristics of

the chip, making predictable design for a desired clock frequency difficult. As a result,

VLSI circuit designers have exploited multiple low power design methods at different

8

levels of the design process. At the same time, reducing power dissipation during test has

become especially critical as inappropriate switching activity during test can jeopardize

the accuracy of the tests, and in some cases, even destroy the chip.

According to the International Technology Roadmap for Semiconductors, testing of

today’s high performance chips is one of the most expensive, time-consuming and

challenging aspects of the overall design cycle [3]. The essential goal of manufacturing

test is to detect defective or “out-of-spec” chips by generating and applying high quality

test patterns at a minimum cost with respect to test application time and test data volume

[6]. The costs of manufacturing test correspond primarily to the time and effort required

to generate the high quality test patterns, the cost of the test equipment, and the

throughput or time required to apply the tests on the test floor. Testability features are

added to digital designs to make the development and application of manufacturing tests

easier and more effective. Unfortunately, they also make matching power during test and

functional operation more difficult.

Design for testability (DFT) techniques help the test engineers to achieve a high

quality test with a minimum usage of testing resources. One of the simplest DFT

approaches consists of Ad-Hoc DFT methods, where good design practices that are

learned from previous design experiences are used in the current circuit design cycle [6].

Unfortunately, the growing size and complexity of digital circuits makes the usage of the

Ad-Hoc DFT methods inadequate for high quality test. As a result, structured DFT

methodologies are a critical component of modern design flows.

9

Structured DFT methods rely on the insertion of the extra logic and signals into the

circuit to improve the testability of the design. Scan-based design is one of the most

widely-used structured DFT techniques for the manufacturing test of digital circuits. It

introduces a new mode to circuit operation—a test mode that is distinct from functional

mode. It reduces the complexity of the test by enhancing the controllability and

observability of the internal nodes of the design. Flip-flops in the design are connected

together into a large shift register, called a scan chain, which allows the circuit to be

initialized to an arbitrary state during test mode and allows the values of all of the flip-

flops, in addition to the outputs of the circuit, to be observed after the application of each

test pattern.

One of the major drawbacks of scan-based test is the increase in the circuit’s switching

activity during the shifting of the scan chain. There are multiple reasons for this

phenomenon. First, the test vectors applied consecutively are not correlated [7]. Second,

non-functional states may be traversed during the testing of the circuit. Furthermore, test

compaction and testing multiple cores simultaneously also contribute to higher switching

activity during test [8].

Unfortunately, increased test power due to excessive switching activity during scan

shift can create hot spots that may damage the silicon, the bonding wires and even the

package. It can also cause intensive erosion of conductors – severely decreasing the

reliability of the device. Furthermore, thermal spots have an adverse affect on the

carrier’s mobility which will eventually slow down the device in the hot-spot region of

the design. Elevated power dissipation and temperature variations in the circuit might

cause timing variations during the test mode that are different from the functional mode –

10

leading to yield loss due to inaccurate testing. As a result, some chips that would perform

well during normal operation may be rejected during test. Finally, the scan clock signal

may experience additional delays caused by supply voltage droop. This could cause scan

chain hold time violations during scan shifting when the delay of the clock signal is

larger than the scan cell hold time margin.

As a result, researchers have proposed various techniques to minimize the power

dissipation of the circuit during scan shift. These power reduction techniques can be

classified into two main categories, DFT-based approaches and ATPG-based approaches.

ATPG-based power reduction solutions [15-48] attempt to reduce the test power

dissipation by changing the characteristics of the test patterns applied to reduce the

switching activity. DFT-based power reduction techniques require either the

segmentation of the conventional scan chain architecture [49-56] or the insertion of

additional hardware into the original design [57-62] .

While it is known that switching activity during scan shift can easily exceed the

switching activity during functional mode, a detailed analysis of this difference has been

missing in the literature. This dissertation quantitatively analyzes the nature of the

switching activity of a circuit for functional and test modes to characterize the magnitude

of the discrepancy. Motivated by this switching activity analysis, we develop a novel and

effective DFT-based power reduction method for reducing the switching activity of the

scan-based test during the shift cycles at very low cost. Previous DFT-based power

reduction techniques rely on inserting extra test points into the verified design at the gate

level; however the insertion of extra hardware at the gate level will add extra delay that

11

may violate the timing requirements of the design. This new methodology makes changes

at the RTL instead of the gate level, providing standard synthesis tools with the ability to

automatically compensate for the added logic.

Reducing the timing discrepancy between design simulation and silicon measurements

is another fundamental challenge of current VLSI technology. With the decreasing noise

and timing margins of current VLSI chips, the performance of the chips has become more

susceptible to excessive switching activity. Making accurate predictions of silicon timing

through the use of pre-silicon modeling and analysis has become a very difficult

undertaking. The ultimate goal of the timing predictions during the design phase is to

estimate the delay of the critical paths on silicon. Unfortunately, current static timing

analysis (STA) tools generally have difficulty predicting the actual delays of the circuit

paths as well as finding the real speed-limiting critical paths of final silicon [9, 10].

Mismatches between silicon measurements and simulation are problematic for variety of

reasons. It makes it harder to predictably design the circuits so that they meet timing

specifications at first-silicon. In addition, it makes silicon debug a more arduous process.

When predicted and post-silicon delays do not match, the problem can be handled by

adding safety margins to designs, typically at the cost of area and performance, by selling

lower performing chips for less cost, or by re-spinning the design. Unfortunately, each of

these solutions is very expensive. As a result, multiple researchers have studied delay

mismatches and attempted to design complex tools to take into account various factors

causing the delay mismatches so that pre-silicon delay predictions can be improved [69 -

86]. However, these complex solutions suffer from practicality and scalability issues. In

this dissertation we develop a noise index model (NIM) which efficiently focuses on the

12

effects of the switching activity-generated IR-drop in the appropriate area around a path

on the actual delay of the circuit paths and estimates the magnitude of the timing

discrepancies due to switching activity.

The impact of switching activity on delay is not only a problem in the design phase. It

is also a problem in the test phase. When scan-based tests are applied, the switching

activity in the circuit during test application may not match the switching activity during

the circuit’s functional mode of operation. This can lead to changes in the delays of

tested paths and cause overtesting. For example, the performance of the chip during test

may be adversely affected by the IR-drop due to the high switching activity. The design

may fail to meet aggressive timing requirements when the supply voltages of the

transistors are reduced by the excessive IR-drop.

Over-testing may cause the circuit to be declared defective even when the chip would

work correctly during its functional mode. This problem can be solved at design time, but

at significant cost. For example, the designers may over-design the chip and power

distribution network by making the power rails of the power distribution network larger

or by increasing wiring pitch [11]. The timing slack may also be increased at the cost of

performance. Over-testing might also cause a loss of revenue even when chips are not

discarded as faulty, such as when the high frequency chips are incorrectly characterized

as lower speed chips and must be sold at lower prices [10].

In order to handle the yield and revenue loss problem, low power ATPG techniques

can be used to minimize the overall switching activity of the circuit during test [15-48].

However power-aware test vectors may also lead to under-testing problems. Some of the

13

chips containing speed-related problems may pass manufacturing test when the power

supply noise effects around the critical paths of the chip are reduced below functional

usage. As a result, in addition to yield loss, test escapes may also occur during delay

testing as a result of non-functional switching activity.

A significant amount of research effort has been directed to the generation of power

supply noise aware test vectors [43-48] and to the generation of pseudo-functional test

vectors [94-100]. These methods have often tried to simply minimize the switching

activity in the entire circuit during test. In other cases, they have relied on either vector-

less analysis of the circuit to estimate its functional mode switching activity, or they have

used designer-specific threshold values, which are based on the average switching

activity of the standard cells, for limiting switching activity. In this dissertation, we

investigate and quantitatively compare the noise index values of the critical paths during

functional and test modes. Based on this analysis we then propose a noise index model-

based test pattern modification technique that aims to generate high-quality test vectors

by reducing the over-testing and under-testing problems simultaneously.

1.1 Main Contributions

In this dissertation, we quantitatively compare the amount of switching activity during

test and functional mode both in the circuit as a whole and in the relevant area around

particular paths. We characterize the effect of local path switching activity on the

realized silicon delay. We then develop DFT-based and ATPG-based algorithms for

reducing the effects of switching activity-generated IR-drop and power consumption

14

during scan-based test to both protect the chip during scan shift and to reduce the impact

of over- and under-testing of the chip during the application of delay test patterns.

More specifically, the main contributions of this dissertation can be summarized as

follows:

• We focus our research efforts on the development of high level techniques to

reduce the effects of excessive switching activity during scan shift.

Specifically, we develop a DFT-based technique to reduce the switching

activity of the circuit during the shift cycles of the scan-based design. The

proposed DFT technique modifies the design at the RT-level such that the

synthesis tools can later be utilized for the automatic optimization of the timing

closure.

• We develop a noise index model (NIM) that characterizes the magnitude of the

timing mismatch between silicon and simulation based upon the switching

activity in a well-defined area around a critical path. We have validated the

effectiveness of this model on an industrial size circuit.

• We perform a detailed quantitative comparison of the switching activity with

respect to the noise index model on multiple benchmark circuits during

functional and test modes. Our comprehensive switching activity investigation

considers the effects of non-functional transitions in addition to the functional

transitions.

• Using the proposed noise index model, we develop an ATPG-based method to

help overcome the over-testing and under-testing problems of digital circuits.

15

Our noise index model-based pattern modification algorithm relies on the true

functional switching of the circuit such that the worst case functional switching

activity profile around the critical path of interest will be replicated during path

delay test. Our noise index model based test pattern modification method will

improve the quality of the at-speed delay test patterns.

1.2 Organization of the Dissertation

Chapter 2 provides background information about some of the important scan-based test

concepts and major fault models that have been used in manufacture testing. After the

introduction on scan-based test and important fault models, Chapter 3 explores previous

work on DFT- and ATPG-based test power reduction techniques during scan test and

then introduces a quantitative analysis on the nature of the switching activity of a circuit

operated in functional and test modes. In this chapter, we also introduce our RT-level

DFT-based approach to reduce the switching activity of the circuit during the shift cycles

of the scan test. Chapter 4 examines previous work on reducing timing mismatches

between silicon measurements and design simulations and then presents our noise index

model which characterizes the magnitude of the timing mismatch between silicon and

simulation. Chapter 5 presents our high-quality test pattern modification method, which

is based on our noise index model. Past research on switching activity aware test pattern

generation and modification techniques have been presented in this chapter. Finally,

chapter 6 offers some conclusions and future research ideas that have emerged through

these projects.

16

Chapter 2

Background

Power Analysis

Power dissipation in CMOS circuits has two components: static power dissipation and

dynamic power dissipation. Static power dissipation is primarily due to sub-threshold

conduction of current and occurs even when the circuit is not changing its state. In

contrast, dynamic power dissipation is generated when the circuit changes its logical

state, causing circuit switching. Although reducing static power dissipation has become

increasingly important—especially in ultra low-power designs, dynamic power

dissipation is still generally the dominant source of the overall power dissipation. It is

also a principal concern in power-aware testing since it is the dynamic power dissipation

that differs significantly between test and functional mode.

Dynamic power depends on the power supply voltage Vdd, the system clock frequency

f, the physical capacitance per unit area C, and the switching activity factor a. The

equation for the dynamic power dissipation is given as:

17

f)CV(P dddynamic α2

21

= (1.1)

Lowering any of these parameters will result in a reduction of the dynamic power

dissipation in the circuit. However, doing so effectively may be difficult both due to the

demands of today’s designs and the complex interdependencies that exist between the

parameters. In general, the parameter that is of most interest during power-aware test is

the switching activity factor a, as it is this parameter that changes significantly between

the test and functional modes of operation. It is also the only parameter that the test

engineer has any control over.

As power supply voltages decrease, the noise margin of the devices reduces

accordingly, making the design more vulnerable to power supply noise (PSN).

Understanding the impacts of the power supply noise on VLSI circuits involves

investigating the power supply network’s response to a sudden change in the current flow

in the circuit. Power supply noise has two components, inductive noise, also known as

Ldi/dt noise, and resistive noise, which is also known as IR-drop. Both the inductive and

resistive noises are due to the package and on-chip parasitics of the power/ground

network. The inductive noise, Ldi/dt, is due to the rate of change of the instantaneous

current flowing through power/ground networks in short time, and is dominant at the

package level of the chip. The resistive noise, IR-drop, refers to the amount of decrease in

the power rail voltage.

An increase in switching activity inside the chip leads to higher current densities in the

power distribution network. Power distribution networks also suffer from voltage

fluctuations due to the rapid changes in the supply current caused by large switching

18

activities inside the design. Specifically, because of the resistive effects of the power

supply network, voltage is reduced locally inside the chip due to current traveling from

the power pads to the core area in the design. Similarly the resistive ground network will

experience a voltage increase as current travels through it. The performance and

reliability of the circuit are adversely affected from both of the voltage drop in the power

supply network and voltage spike in the ground network. The IR drop will reduce the

voltage difference between the VDD and VSS pins of the standard cells, leading to a

reduction in standard cell’s performance. For example, the authors of [4] showed how the

delays of the circuits are affected by the supply voltage changes; specifically, for 90nm

technology, a 1% change in power supply voltage leads to a 4% change in the delay of a

circuit. Thus, in addition to potentially damaging the chip, changes in non-functional

switching activity may change the delay characteristics of a device during test.

Testing

The main goal of the manufacturing test is to ensure that a digital circuit fabricated on

silicon behaves according to the designer’s specifications. A high-quality manufacturing

test procedure should identify all the defective chips. As the complexity of current VLSI

systems increase, generating high-quality test vectors with good coverage becomes more

complicated and resource-intensive as well. The test generation problem becomes even

more complex in the case of sequential circuits because it is very difficult to control and

observe the internal states of the memory elements in sequential circuits. Therefore,

different types of design-for-testability techniques have been proposed for alleviating

some of the complex problems of manufacturing test.

19

Scan-based test is one of the most widely accepted design-for-testability techniques.

Additional logic is added to the design such that the controllability and observability of

the design will increase during the test of the circuit. Unfortunately scan-based tests often

cause excessive switching activity compared to the circuit’s normal operation. This

increase in switching activity results in additional challenges in manufacture testing of

digital circuits.

In the remainder of this chapter we will describe the essential concepts of scan-based

test and the most commonly used fault types for manufacturing test. The fundamentals

that are described in this chapter will be used in the subsequent chapters of the

dissertation when we will explain our methodologies.

2.1 Scan-based Test

The application of the scan-based test into the manufacturing test area was introduced by

Michael Williams and James Angell in 1973 [12]. The goal of the scan test is to simplify

the complex sequential automatic test pattern generation problem by introducing some

internal modifications to the original design. For a sequential design to have scan

capability, certain internal modifications have to be introduced into the original design.

This internal modification of the design starts with replacing the original sequential

elements, D-type flip flops, with scan flip-flops/cells which are later stitched together to

form a shift register, called a scan chain. One of the most widely used approaches to

convert D-type flip flops into scan flip flops is by using MUX-based scan cells. Figure

2-1 illustrates the difference between a standard D-type flip flop and a MUX-based scan

20

flip flop. An additional multiplexer is added to the original flip flop in order to select

between the test or normal mode of operation. Two additional primary inputs, called

scan_enable and scan_in, and one additional primary output, scan_out, are added to the

original design.

D Q D QD

SI

SE

CLK CLK

D-type FF MUX-based Scan-type FF

D Q D QD

SI

SE

CLK CLK

D-type FF MUX-based Scan-type FF

Figure 2-1: The difference between the D-type flip flop and MUX-based scan flip flop

Figure 2-2 illustrates a small example for the scan inserted circuit. The scan_enable

signal is connected to the SE pin of the scan flip flop in order to control test and normal

mode. And the scan_in signal is connected to the SI pin of the scan cell. As we have

pointed out before, in addition to the circuit’s functional operation, scan-inserted designs

also operate in an additional mode called test mode. When the circuit operates in test

mode, the states of the scan flip-flops can be set to any logic value by shifting the logic

states through the scan_in input of the shift register. To allow the shift operation, first the

scan flip-flops are put into the shift mode through scan_enable signal. Test stimuli/test

responses are loaded into/unloaded from the scan chain during these shift cycles of the

test mode. During scan shift, the test stimuli are shifted into the scan chains one bit at a

time, and they create transitions at the scan cell outputs that are further rippled through

the combinational part of the circuit.

21

CLK

AB CCOMBINATIONAL CIRCUIT

D Q D Q D Q

SE SE SESI SI SI

Scan_enable

Scan_inScan_out

CLK

AB CCOMBINATIONAL CIRCUIT

D Q D Q D Q

SE SE SESI SI SI

Scan_enable

Scan_inScan_out

Figure 2-2: Scan inserted design

Hence there will be unnecessary switching activity in the combinational part of the circuit

during the shift cycles. After the complete test vector is shifted into the scan chain, the

shift mode is disabled by forcing the scan_enable signal to logic 0. This places the

circuit back into normal mode to continue the test. During normal mode, the scan cell

contents are updated by applying functional clock(s), and the data stored in the cells is

determined by the circuit’s combinational logic. Depending on the type of the fault model

used, there may be either one functional clock cycle or two functional clock cycles. In the

subsequent sections, we will review three of the most important fault models and the

timing formats of the scan test for those fault models.

2.2 Overhead of Scan-based Test

The use of the scan-based DFT methodology adds area and performance overhead to

the design. In the most straightforward implementation, the replacement of the regular D-

22

type flip-fops with multiplexer-based scan cells adds four additional gates to each flip-

flop. In addition to the increase in gate count, additional routing effort needs to be made

for the scan_enable signal. Scan-based design also impacts the performance of the

circuit. The usage of the multiplexers for every flip flop adds additional delay to the

circuit.

In the full scan methodology, all the sequential elements will be replaced with scan

cells and then stitched together in order to form the scan chain. The full scan

methodology is a fully automated process and thus requires very little manual effort.

However, the area and timing constraints of the design may not allow the usage of the

full scan approach. Alternatively, only a fraction of the sequential elements of the design

can be replaced with scan cells and then stitched into a scan chain. This approach is

called partial scan. Using the partial scan method, the testability of the sequential design

is increased with less impact on the area and timing of the design. For the critical parts of

the design where additional delay can not be tolerated, the flip flops that are physically

located in these critical areas can be excluded from the scan chain. Compared to the full

scan method, partial scan testing requires more ATPG effort for test vector generation.

Based on the area and performance budget of the design, the test engineer must select an

optimal approach for the scan methodology. In this work, we will only consider full-scan

designs.

23

2.3 Fault Models

2.3.1 Stuck-at Faults

Stuck-at faults are one of the most widely used fault models in the area of digital circuit

test because of the effectiveness of test patterns targeted toward them at finding most

common static defects in chips. Static defects are characterized by the fact that they

transform a circuit which realizes the intended function into a circuit that no longer

realizes that function. In other words, for some input combination, the defective circuit

will produce incorrect values at the outputs. When using the stuck-at fault model, the

digital circuit is modeled as interconnections between logical gates. The stuck-at fault

model is associated with these interconnections. In the case of fanout, a branch is

considered a distinct location from the stem. There are two types of stuck-at faults:

stuck-at 0 and stuck-at 1. For the stuck-at 0 fault, the signal line will always remain at a

logical state 0 irrespective of the correct logic output of the driving gate. For the stuck-at

1 fault, the reverse situation exists. Figure 2-3 shows an example circuit having a stuck-at

1 fault at its primary input line A.

24

AS

B

f

P

Q

A s-a-1

0 0/1

1 1/1

0/0

0/10/0

0/1

X

AS

B

f

P

Q

A s-a-1

0 0/1

1 1/1

0/0

0/10/0

0/1

X

Figure 2-3: Stuck-at fault example

The detection of stuck-at faults, like any other faults, has to meet two conditions:

excitation and observation. The excitation, also known as activation, of the stuck-at faults

involves forcing the faulty line to an opposite value from the actual fault value in the non-

faulty circuit. For example in Figure 2-3, the input signal A with the stuck-1 fault has to

be set to a logic 0 value, in order to excite this fault. After the excitation of the fault at a

particular site, the effect of the fault has to be propagated through a path to a primary

output (PO) or pseudo-primary output (PPO)—generally a scan flip-flop. This is called

observation. In order to observe the fault in Figure 2-3, input S is set to the required logic

value, so that the effect of fault is propagated to the primary output. When both of these

requirements are met, the fault can be detected. The detection of the stuck-at faults for

scan-based test requires application of one clock cycle in the normal mode between the

shift operations. The clocking scheme for stuck-at faults during scan-based test is shown

in Figure 2-4. The applied clock frequency for stuck-at faults is much slower than the

functional clock frequency because stuck-at faults do not affect the timing behavior of the

circuit. The test sets that are developed for detecting stuck-at faults may uncover many

25

static manufacturing defects and will ensure the logical correctness of the design.

However stuck-at fault test sets can not detect dynamic manufacturing defects which will

affect the timing behavior of the design. The presence of the defect does not alter the

function realized by the circuit over the long term, but it causes the circuit to slow down.

With the dominance of the timing related defects in current nanometer integrated

circuits (ICs), delay testing has become very popular in recent years. The delay of the

combinational logic in the circuit might exceed the clock period when the circuit has a

delay defect or when process variations impact the timing behavior of the circuit. For

correct circuit operation, the delay of the combinational logic in the circuit should not

exceed the clock period. In order to guarantee the timing correctness of the design, at-

speed testing in which the test patterns are applied to the design under test (DUT) at a

functional clock speed is essential. Transition delay fault (TDF) and path delay fault

(PDF) models are the most commonly used models in at-speed delay testing. In the next

sections, we will review these delay fault models in more detail.

26

CLK

Time

… …

capture

shift

…

SE

Time

shift

CLK

Time

… …

capture

shift

…

SE

Time

shift

Figure 2-4: Stuck-at test timing scheme

2.3.2 Transition Delay Faults

A transition fault at a circuit site causes a signal change at the faulty site to be slower

than expected [6]. To detect a delay fault, a two-vector sequence <V1, V2> is applied to

the circuit under test. The first vector, V1, is the initialization vector. It is responsible for

setting the values in the circuit to the correct initial state so that the desired transitions

will appear when the second vector is applied. The second vector, V2, is the

propagation vector. This vector actually launches the transition and propagates the effect

of the transition to an observable site in the circuit.

One significant advantage of the transition delay fault model is that the number of

faults in the circuit increases linearly with circuit size. There are two types of transition

faults: slow-to-rise and slow-to-fall. Every location where a stuck-at fault may appear is

27

also considered a potential site for a transition fault. For a slow-to-rise transition fault on

a line, the first vector V1 sets the line to a logic 0 and the second vector V2 is responsible

for creating the 0-to-1 transition. So V2 sets the line to logic 1 as well as propagates the

effect of the transition to an observable site in the circuit. If the rising delay is large

enough to exceed the slack on the chosen propagation path, the transition delay fault will

get detected with the applied vector pair.

The slack of a path is the difference between the clock period and the expected arrival

time of a transition propagating along that path. A negative slack for the path implies that

the path is too slow and needs some improvements to meet the timing requirements of the

circuit. However a path with positive slack can tolerate some extra delay without

violating the timing behavior of the circuit. Current ATPG tools tend to detect the

transition delay faults through short paths which usually have large slacks because there

is an underlying assumption that the delay is large.

Another disadvantage of transition fault modeling is the assumption that the delay

defect affects only one particular circuit site. However delay defects and process

variations may add small delays to multiple sites along a path. This is especially

problematic for long paths with small slacks. Thus, transition delay fault modeling is not

effective for detecting distributed small delay defects. As a result, another delay fault

model, the path delay fault model, has been used to detect the small delay defects. In the

next section we will review the path delay fault modeling.

28

2.3.3 Path Delay Faults

Path delay fault modeling is superior to the transition delay fault models in terms of its

small delay detection capability. A path in a circuit starts with a primary input or a

clocked flip-flop, goes through combinational logic, and ends with a primary output or

clocked flip-flop. A path delay fault causes the cumulative propagation delay of the

combinational logic to increase. The path delay fault model uncovers the small

distributed delay defects caused by random variations effectively because they are

usually detected through the circuit’s critical paths, which have small slacks. Critical

paths of a circuit are the combinational paths with the longest propagation delay. Static

timing analysis (STA) tools are used to obtain a list of the expected critical paths of the

circuit. There are two types of path delay faults associated with a path in the circuit:

rising and falling path delay faults.

There are also two types of path delay tests: robust and non-robust path delay tests.

Non-robust path delay test guarantees to detect the fault on the targeted path when no

other path delay fault is present. In the presence of other delay faults, the targeted fault

might remain undetected by a non-robust test. A non-robust path delay test applies a

two-vector sequence at the start of the path and measures the values at the end of the path

after the specified clock period. The vector pair has to satisfy two conditions: first, it has

to launch the required transition at the start of the targeted path and second, it has to set

all the off path inputs of the targeted path to non-controlling values for the second vector

[13]. A robust path delay test guarantees that the delay fault on the targeted path will be

detected if the delay of the path exceeds the clock period, independent of all other delays

in the circuit. For many circuits, it is very difficult to find robustly-testable path delay

29

faults. The robust test has to satisfy all the requirements of the non-robust test, and in

addition it has to make sure that whenever the transition on path input k is from a non-

controlling to a controlling value each side input of k has to be held steady at the non-

controlling value [13].

2.4 Scan-based Delay Testing

When delay testing is performed for scan-inserted circuits, there are two different

clocking schemes for performing the delay test: launch-off last shift (LOS) and launch-on

capture (LOC). Both of these methods have advantages and disadvantages. For the

launch-off last shift, the first vector V1 is shifted in to the scan chain, and the second

vector V2 is merely a one-bit shift of the first vector. The difference for the launch-on

capture method lies on the generation of the second vector. For the launch-on capture

method, the second vector V2 is generated as the functional response of the

combinational circuit to the first vector V1.

The clocking scheme for launch-on capture methods is shown in Figure 2-5. The test

patterns are shifted in to the scan chain during the shift cycles. The clock frequency of the

shift cycles is usually slower than the functional clock frequency. After the entire pattern

is shifted into the scan chain, the system clock is applied once to launch the transition

from the first vector V1 to the second one V2. Then the system clock is applied second

time in order to capture the response of the circuit to the second test vector V2. Then the

circuit is put into the shift mode again in order to shift out the responses of the applied

pattern and to shift in the next pattern into the scan chain.

30

CLK

Time

… …

capture

shift

…

Last shift Launch

SE

Time

shift

CLK

Time

… …

capture

shift

…

Last shift Launch

SE

Time

shift

CLK

Time

… …

capture

shift

…

Last shift Launch

SE

Time

shift

Figure 2-5: Timing behavior for LOC delay test

In contrast, the timing behavior for the launch-off shift method is shown in Figure 2-6.

In the LOS delay test scheme, after the first vector V1 is shifted in to the scan chain, the

scan register is shifted one more time to launch the transition from the first vector V1 to

the second vector V2. In LOS scheme, the test is designed such that the second vector is

obtained through one bit shift of the first vector. Then the system clock is applied once to

capture the response to the second vector. Then the circuit’s responses get shifted out

and the next vector gets shifted in as in the LOC case.

Both of the scan delay test methods have been used for transition delay and path delay

fault tests and they have their own advantages and disadvantages. The fault coverage of

the LOS delay test is higher than the LOC delay test; hence the test set that is generated

with a LOS clocking scheme contains fewer patterns than the test set that is generated

with LOC clocking scheme. However the issue of LOS testing is the timing criticality of

31

the scan_enable signal. For LOS testing the scan_enable signal must be at-speed. The

requirement for a fast scan_enable signal will also increase the DFT cost because of the

routing of the scan_enable signal. The LOC test doesn’t have any requirements regarding

a fast scan_enable signal, however it will have less fault coverage and more test patterns

compared to the LOS testing. According to [14] the design effort and the time required

for designing and routing of the fast scan_enable signal is not acceptable for many

industrial designs. Therefore LOC delay testing is more widely used in industry.

CLK

Time

… …

capture

shift

…

Last shift &Launch

SE

Time

shift

… …CLK

Time

… …

capture

shift

…

Last shift &Launch

SE

Time

shift

… …CLK

Time

… …

capture

shift

…

Last shift &Launch

SE

Time

shift

… …

Figure 2-6: Timing behavior of LOS delay test

32

Chapter 3

Power Dissipation during Test

Power dissipation during scan test is analyzed in two categories depending on the

clock cycle of interest. The test power consumed during scan shift cycles and capture

cycles is referred to as shift power and capture power, respectively. During scan shift, the

test stimuli are shifted into the scan chains one bit at a time. This creates transitions at

the scan cell outputs that are further rippled through the combinational part of the circuit.

Despite the fact that the clock frequency during the shift cycles is low, the average shift

power consumption is still a concern in scan-based test. During the capture cycles, the

scan cell contents are updated by applying functional clock(s) and capturing data from

the combinational logic. To reduce the switching activity during the scan test, many

different power aware test approaches have been proposed in the literature. These low

power scan test schemes can be classified in two broad categories: ATPG-based solutions

and DFT-based solutions.

In this chapter, we will first review the previous work on switching activity reduction

techniques during scan-based testing. After the review of the previous work, we will

33

present a quantitative analysis on the switching activity for a benchmark circuit during its

functional and test modes. Motivated by the difference in test and functional mode

switching activity, we present our RTL-based method for reducing switching activity

during the shift cycles of the scan test.

3.1 Test Power Reduction Techniques

As dynamic power consumption has become an important concern in the

manufacturing test of high-performance digital circuits, many approaches have been

proposed to reduce the test power during the shift and capture cycles. The first category

of these approaches, ATPG-based solutions, focuses on the test pattern generation

process and generates test patterns that will result in less switching activity in the circuit.

On the other hand, DFT-based solutions require the insertion of additional hardware into

the original design. Both ATPG and DFT-based methods focus on different aspects of

power-aware test and tackle the power dissipation problem at different levels. Both of the

methods have their own advantages and shortcomings. We will review the previous

research on both of the methods in the next sub-sections.

3.1.1 ATGP-based Approaches

The ATPG based solutions [15-48] attempt to reduce the test power dissipation during

test generation. These techniques can be grouped into several different categories such as:

deterministic don’t care bit filling techniques [15-26], test vector reordering methods [27-

34

33], application of a special input control pattern [34] , test vector compaction techniques

[35-37], high-quality test pattern selection [38-42] and power-aware test pattern

generation algorithms [43-48].

Power-aware X-filling methods [15-26] take advantage of the high percentage of

don’t care bits in a given test pattern set. These techniques try to minimize the switching

activity of the circuit during the shift and/or capture cycles of scan-based test by filling

the X-bits deterministically. In conventional ATPG, the don’t care bits are filled

randomly in order to increase the fortuitous detection of the faults that are not explicitly

targeted during the ATPG process. However random filling of the don’t care bits results

in much higher switching activities in the circuit. In addition to random fill, other basic

filling options such as 0-fill/1-fill are also used in conventional ATPG. However they

also don’t show a high reduction in transition count during the scan test. The authors of

[16] proposed a simple method called Adjacent Fill, where the X-bits are filled based on

the logic values of their adjacent cells in the scan chain. As the adjacent scan cells are

filled with the same logic values, the total number of transitions during the shift cycles

can be reduced. More advanced variations of the Adjacent Fill method have been

proposed by different researchers [15, 18-22, 25, 26]. Other researchers have proposed X-

filling techniques for at-speed delay testing [17, 23, 24]. In these X-filling techniques,

also known as critical-path-aware X-filling techniques, the don’t care bits are filled

intelligently such that the switching activity around the long sensitized paths can be

reduced during the launch cycles of the scan-based test. These methods rely on the layout

information of the circuit. The main problem with X-filling approaches is the resulting

35

large number of test vectors because test vector compaction algorithms don’t work well

when the number of X values becomes small.

The test vector re-ordering methods try to decrease the dynamic power dissipation of

the circuit by increasing the correlation among the test vectors. Test vector re-ordering is

an NP-complete problem [33]. Researchers have proposed many different techniques for

the optimal order of the test vectors such that the circuit under test experiences less

switching activity [27-33].

Test pattern selection and grading techniques [38-42] pick the most effective patterns

from a larger test set. A conventional ATPG tool is used to generate an n-detect test set

where each fault in the fault list has to be detected n-times during the fault simulation.

Test pattern selection methods screen the patterns from the n-detect test set and construct

a high-quality 1-detect test set.

Low-power test pattern generation algorithms [43-48] attack the problem during the

test vector generation step. They usually rely on power-aware cost functions to generate

the test vectors that minimize the switching activity of the circuit during test mode in

addition to meeting ATPG objectives such as fault coverage and test pattern length.

3.1.2 DFT-based Approaches

In addition to ATPG-based solutions, the research on low power test also focuses on a

different approach: DFT-based methods. In contrast to the ATPG-based methods, DFT-

based approaches are test set independent, and they don’t change the length of the input

36

test patterns. DFT-based techniques involve modifications to the original design. They

either require partitioning of the conventional scan chain architecture [49-56] or the

insertion of additional hardware into the design [57-62].

The fundamental idea of the scan chain partitioning methods [49-56] is to divide the

conventional scan chain into multiple scan chain segments such that the shift operation of

the test patterns can be broken down into different scan chain segments. The scan chain

partitioning methods ensure that the shift-in/shift-out process can be performed on certain

scan chain segments while the other ones can be clock gated. These methods reduce the

average test power dissipation during shift cycles.

Besides partitioning the scan architecture, researchers have also developed techniques

to block the rippling of the transitions at the scan cell outputs to the combinational logic.

In [57], extra logic is inserted to hold the outputs of all the scan cells at constant values

during scan shifting. The main disadvantage of these approaches is the large area

overhead. Moreover, they may degrade circuit performance due to the extra logic added

between the scan cell outputs and the functional logic. The use of the supply gating

transistors for the first-level combinational gates at the outputs of scan cells is proposed

in [58]. The supply gating transistors are placed on every gate that is directly driven by a

scan cell. This technique reduces both dynamic and leakage power dissipation during

shift mode. An alternative implementation to hold the scan cell outputs constant by using

dynamic logic was proposed in [59]. The method proposed in [60] inserts test points at

selected scan cell outputs to keep the peak shift power at every shift cycle below a

specified limit. Given a set of test patterns, logic simulation is carried out to identify the

violating shift cycles in which peak power violations occur. By using integer linear

37

programming (ILP) techniques, the optimization problem is solved to select as few test

points as possible such that all violating cycles can be eliminated. The disadvantages of

this method are twofold: (1) Inserted test points are test set dependent. Therefore,

violating cycles may not be eliminated when the test set is changed; (2) Solving an ILP

problem with a constraint matrix of the size of Vc X 2S is not applicable to large

industrial circuits, where Vc is the total number of violating cycles, and S is the total

number of scan cells. A medium size industrial circuit typically contains several hundred

thousand scan cells. In [61], random vector simulation was used to guide partial test point

selection. When simulating a random vector, the primary inputs and the pseudo-primary

inputs are set to the value X with pre-specified probabilities, and the number of gates

becoming X after the change is used as a cost function to identify the logic value assigned

at the primary inputs and the pseudo-primary inputs, as well as to select scan cells to be

held during scan shifting. To explore several hundred thousands of scan cells in an

industrial circuit, a significant number of random vectors need to be simulated in order to

choose good test points. In [62], the authors analyze the test set to determine the indices

of the bits with high transition frequency and then modify the scan chain accordingly to

reduce the number of transitions during shift cycles.

Motivated by the previous work in [57] [60] [61], another test point insertion approach

to reduce scan shift power was proposed in [63]. They observed that some scan cells have

a much larger impact on toggling rates at the internal signal lines than other scan cells.

The authors call those scan cells power-sensitive scan cells [63]. Our work on reducing

the switching activity of scan shift cycles takes the advantage of the power sensitive scan

cell concept which is described in [63]. Before we introduce our flow, we will first

38

review the work described in [63] in the following sections of this chapter. In addition,

before we introduce our DFT-based approach which reduces the switching activity of the

circuit during the shift cycles of the scan test, we will first present a quantitative analysis

of the switching activity of a circuit operated in test and functional modes.

3.2 Comparison of the Switching Activity during Test and

Functional Modes

Compared to the power dissipation during normal operation, the research in low power

testing has highlighted that the increase in power dissipation during scan test is a

significant problem for testing. However, a quantitative study of the switching activity

during test as opposed to functional mode has not been carried out in the literature on low

power test. Thus, in this section, we present a quantitative analysis of the switching

activity for an example circuit during test and functional modes. In this section, we intend

to show the difference in circuit’s switching activity between the functional way the chips

are used and the way we test them.

The example circuit is a benchmark circuit obtained from opencores.org [64] and its

function is to transform colors between different encodings such as CIE XYZ ↔ RGB or

RGB ↔ YCbCr. Figure 3-1 shows the simulation flow for the functional inputs. The RTL

description of the design, the testbench and the MATLAB code to transform the real

image into an ASCII coded file were all obtained from opencores.org [64]. In the

simulation flow, an industrial synthesis tool is first used to synthesize the benchmark

circuit from the RTL description to the gate level netlist. During synthesis, the timing

39

characteristics of the standard library cells are considered in order to allow

comprehensive switching activity analysis to be carried out later at the gate level.

Synthesis Engine

Color ConverterRTL

Color ConverterGate Level Netlist Test Bench

MATLAB Code

ASCII inputfile

Real Image

Modelsim

ASCII outputfile

VCD

Synthesis Engine

Color ConverterRTL

Color ConverterGate Level Netlist Test Bench

MATLAB Code

ASCII inputfileASCII inputfile

Real ImageReal Image

Modelsim

ASCII outputfileASCII outputfile

VCD

Figure 3-1: Simulation flow for functional inputs

Our switching activity analysis flow only considers the timing information of the

standard cells and the effect of the applied input patterns. More detailed switching

activity analysis including the switching capacitance values of the cells can be performed

if the layout information of the design is available. After the gate level netlist is created,

we used ModelSimTM to simulate the netlist operated in functional mode. The testbench

reads an ASCII coded input file that represents a picture and performs the color

transformation. An ASCII coded output file is created after approximately 25000 clock

cycles. When running the testbench, we made ModelSimTM generate a Value Change

40

Dump (VCD) file in order to record all the signal value changes at every gate that

occurred during simulation. The VCD file was processed by a script developed in house

to analyze the distribution of the switching activity for all the nets over any specified time

slot.

TABLE 3-1

Average Number of Transitions per Clock Cycle during Functional Operation

Average Number of Transitions Per Clock Cycle Time Slot

Combinational Library Cell Outputs Flip-Flop Outputs

1st 5000 656 135

2nd 5000 781 151

3rd 5000 758 155

4th 5000 687 143

5th 5000 638 136

Average 704 144

In Table 3-1, we show the average number of transitions per clock cycle at

combinational library cell outputs and flip-flop outputs, respectively, after dividing the

whole functional simulation into five time slots, 5000 clock cycles per slot. The average

numbers of transitions per clock cycle over five time slots are given on the row Average

of the Table 3-1.

Next, we collected the switching activity during test mode for both the shift and

capture cycles. The analysis flow is shown in Figure 3-2. Similar to the flow shown in

41

Figure 3-1, we first used the synthesis tool to create a gate level net list from the RTL

description.

Synthesis Engine

Color ConverterRTL

Color ConverterGate Level Netlist

Modelsim

VCD

ScanInsertion

ATPG

Scan InsertedNetlist

Scan TestPatterns

Synthesis Engine

Color ConverterRTL

Color ConverterGate Level Netlist

Modelsim

VCD

ScanInsertion

ATPG

Scan InsertedNetlist

Scan TestPatterns

Figure 3-2: Analysis flow for test patterns generated by ATPG

We then ran the scan insertion tool to create the scan chain and the ATPG tool to

generate 142 scan test patterns based on the stuck-at fault model. ModelSimTM was used

next to simulate the test patterns according to the order in which they are generated. It is

worth pointing out that we simulate the simultaneous scan in and scan out of adjacent

42

patterns in order to collect accurate simulation data during test. Another VCD file was

created during simulation for switching activity analysis.

TABLE 3-2

Average Number of Transitions per Clock Cycle for ATPG

Average Number of Transitions Per Clock CycleTest Operation

Combinational Library Cell Outputs Flip-Flop Outputs

Shift 1620 286

Capture 3345 293

The results of the switching activity analysis for the ATPG test patterns are shown in

Table 3-2. The average number of transitions per clock cycle at the combinational library

cell outputs and the flip-flop outputs are listed in the rows Shift and Capture for the scan

shift and capture, respectively.

Comparing the switching activity between Table 3-1 and Table 3-2, it can be seen that

the average number of transitions per clock cycle during scan shift is 2.3 and 2 times

larger than that during normal operation for the combinational library cells and the flip-

flop outputs, respectively. When considering the switching activity during capture, the

ratios become higher, and they are 4.75 and 2 times larger than the switching activity

during normal operation for the combinational library cells and the flip-flop outputs,

respectively.

43

Although the number of transitions per clock cycle during scan shift is much lower

than that during capture, it is worth pointing out that the number of shift cycles used to

shift in a scan test pattern is typically much larger that the number of capture cycles in the

same pattern. Therefore, heat accumulating during scan shift may damage the chip under

test and cause the incorrect values captured into scan cell during capture. Reducing scan

shift power is one of the major problems during test.

Motivated by the switching activity analysis for functional and test modes shown

above, we have developed a novel and effective method for reducing the switching

activity during scan shift at RTL. Before we describe our RTL-based DFT approach,

which will reduce the amount of switching activity during the shift cycle, we will review

the previous work on the identification of power-sensitive scan cells proposed in [63]

because it plays a fundamental role in our proposed method.

3.3 Power Sensitive Scan Cell Identification

3.3.1 Signal Probability Approach

Signal probability calculations to compute the probability of the logical values for the

internal lines of digital circuits have been widely used for several different applications,

including testability measures and power dissipation estimation [65, 66]. When the

primary inputs of digital circuits are assigned with random input vectors, the statistical

estimation of the logical values for the internal lines is computationally-expensive [66].

44

In [63], an effective and efficient signal probability based approach was proposed for

power-sensitive scan cell identification. In this section, we will review the signal

probability approach with the help of a small example circuit.

The signal probability of a signal line i is defined as the probability that i is set to a

logic value v, v∈{0, 1}, by a random vector. In [63], the signal probability calculation

starts by assigning the PI’s and pseudo PI’s (scan cell outputs) an equal probability of

being set to 0 or 1. Then the circuit is traced forward to find the signal probabilities at the

gate outputs (ignoring correlations at gate inputs.) Figure 3-3 provides an example of

how the signal probabilities of internal nodes are calculated. Note that nis is the next state

of the ith scan cell si, where i=1..3. At each site, the probability of a logic zero and logic

one is shown in parentheses.

pi1

pi2

s1

s2

s3

s1n

s2n

s3n

g1

g2

g3

g4

g5 g6

g7

(0.5, 0.5)

(0.5, 0.5)

(0.5, 0.5)

(0.5, 0.5)

(0.75, 0.25)

(0.5, 0.5)

(0.75, 0.25)

(0.375, 0.625)

(0.375, 0.625)

(0.391, 0.609)

(0.305, 0.695)

(0.348, 0.652)

Figure 3-3: Signal Probability Calculation

45

3.3.2 TRR – Toggling Rate Reduction Metric

In this section we review the work in [63], which shows how the scan cells are

identified as power-sensitive scan cells based on the signal probability approach

explained in the former section.

In [63], the signal probability estimates were used to calculate a test pattern-

independent toggling rate reduction (TRR) metric, with the goal of identifying the power-

sensitive scan cells. First, the toggling probability, TP, of a signal line i is calculated as

follows:

)1()0( iii PPTP ×= 3.1

where Pi(0) and Pi(1) are the probabilities that line i is equal to 0 and 1, respectively.

(Note that this is actually equal to half of the true toggling probability if values of the line

i on adjacent clock cycles are statistically independent.) Then, they define a figure of

merit proportional to the toggling rate, TR, of the whole circuit as shown below:

∑=

=N

iiTPTR

1 3.2

where N is the total number of signal lines in a circuit. For the circuit shown Figure 3-3,

the TR is equal to 2.62. Next, to determine the power sensitivity of a scan cell, the

toggling rate reduction (TRR) of a scan cell si is computed by using the procedure

calculate_TRR() shown in Figure 3-4. Toggling rate reduction of a scan cell is calculated

as follows:

46

),( 10 ==−=iii sss TRTRMINTRTRR 3.3

For example, after freezing the PPI s2 to the values 0 and 1 in the circuit in Fig. 3, the

toggling rates are calculated as TRS2=0 = 2.26 and. TRS2=1 = 1.82. Thus, TRRS2 is equal to

0.8. Similarly, we can compute the TRR at other scan cells as well.

Procedure Calculate_TRR()

• Calculate signal and toggling probability of every signal line in the circuit.

• Compute the initial signal toggling rate TR of the circuit by using equation 3.2

• For each value , and for every scan cell:

• Change the signal probability P(v) at scan cell si to 1.0 and to 0.0.

• Update the signal probability at every internal signal line

• Use equation (2) to compute the toggling rate when freezing si to value v.

• Compute TRRsi by using equation 3.3

Procedure Calculate_TRR()

• Calculate signal and toggling probability of every signal line in the circuit.

• Compute the initial signal toggling rate TR of the circuit by using equation 3.2

• For each value , and for every scan cell:

• Change the signal probability P(v) at scan cell si to 1.0 and to 0.0.

• Update the signal probability at every internal signal line

• Use equation (2) to compute the toggling rate when freezing si to value v.

• Compute TRRsi by using equation 3.3

Figure 3-4: Procedure for calculating TRR

The significance of the TRR lies in the fact that a transition at a scan cell si may cause

more internal signal lines to be toggled than a transition at another scan cell sj when

47

TRRSi is larger than TRRSj. In that case, si is considered to be more power-sensitive than

sj. Toggling rate values of scan cells can also be used to identify the logic value at which

a scan cell should be frozen. The frozen value of a scan cell is chosen so that the toggling

rate of the scan cell is minimized. For example, for the circuit in Figure 3-3, PPI s2

should be frozen to logic value 1 because TRS2=1 is smaller than TRS2=0.