8051 microcontroller detailed tutorial

description

Transcript of 8051 microcontroller detailed tutorial

8051

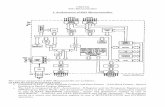

The 8051 is a single chip microcontroller developed by Intel in 1980. A microcontroller is a computer on a single IC containing CPU, Memory, I/O. 8051 is primarily used in Embedded Systems.

Key Features: 8-bit ALU and Accumulator, 8-bit Registers (one 16-bitregister with special move instructions), 8-bit data bus and 216-bit address bus/program counter/data pointer and related 8/11/16-bit operations; hence it is mainly an 8-bitmicrocontroller Boolean processor with 17 instructions, 1-bit accumulator, 32 registers (4 bit-addressable 8-bit) and up to 144 special 1 bit-addressable RAM variables (18 bit-addressable 8-bit) Multiply, divide and compare instructions 4 fast switchable register banks with 8 registers each (memory mapped) Fast interrupt with optional register bank switching Interrupts and threads with selectable priority Dual 16-bit address bus It can access 2 x 216 memory locations 64 KB (65,536 locations) each of RAM and ROM 128 bytes of on-chip RAM (IRAM) 4 KB of on-chip ROM, with a 16-bit (64 KB) address space (PMEM). Not included on 803X variants Four 8-bit bi-directional input/output port UART (serial port) Two 16-bit Counter/timers Power saving mode (on some derivatives)

Memory: Microcontroller requires a program which is a collection of instructions. This program tells Microcontroller to do specific tasks. These programs require a memory on which these can be saved and read by Microcontroller to perform specific operation. The memory which is used to store the program of Microcontroller is known as code memory or Program memory. Microcontroller also requires a memory to store data or operands temporarily. The memory which is used to temporarily store data for operation is known as Data Memory and we uses 'RAM'(Random Access Memory) for this purpose. Microcontroller 8051 has 4K of Code Memory or Program memory that is it has 4KB Rom and it also have 128 bytes of data memory i.e. RAM.

Bus: Basically Bus is a collection of wires which work as a communication channel or medium for transfer of Data. These buses consist of 8, 16 or more wires. Thus these can carry 8 bits, 16 bits simultaneously. Buses are of two typesBuses:Address BusData BusAddress Bus: Microcontroller 8051 has a 16 bit address bus. It used to address memory locations. It is used to transfer the address from CPU to Memory.Data Bus: Microcontroller 8051 has 8 bits data bus. It is used to carry data.

Oscillator: Microcontroller is a digital circuit device, therefore it requires clock for its operation. For this purpose, Microcontroller 8051 has an on-chip oscillator which works as a clock source for Central Processing Unit. As the output pulses of oscillator are stable therefore it enables synchronized work of all parts of 8051 Microcontroller.

Input/output Port: Microcontroller is used in embedded systems to control the operation of machines. Therefore to connect it to other machines, devices or peripherals we require I/O interfacing ports in Microcontroller. For this purpose Microcontroller 8051 has 4 input output ports to connect it to other peripherals.

Timers/Counters: Microcontroller 8051 has 2 16 bit timers and counters. The counters are divided into 8 bit registers. The timers are used for measurement of intervals, to determine pulse width etc

Memory:

The MCS-51 has four distinct types of memory internal RAM, special function registers, program memory, and external data memory.Internal RAM (IRAM) is located from address 0 to address 0xFF. IRAM from 0x00 to 0x7F can be accessed directly. IRAM from 0x80 to 0xFF must be accessed indirectly, using the @R0 or @R1 syntax, with the address to access loaded in R0 or R1. The 128 bits at IRAM locations 0x200x2F are bit-addressable.Special function registers (SFR) are located in the same address space as IRAM, at addresses 0x80 to 0xFF, and are accessed directly using the same instructions as for the lower half of IRAM. They cannot be accessed indirectly via @R0 or @R1. 16 of the SFRs are also bit-addressable.Program memory (PMEM, though less common in usage than IRAM and XRAM) is up to 64 KB of read-only memory, starting at address 0 in a separate address space. It may be on- or off-chip, depending on the particular model of chip being used. Program memory is read-only, though some variants of the 8051 use on-chip flash memory and provide a method of re-programming the memory in-system or in-application. In addition to code, it is possible to store read-only data in program memory, accessed by the MOVC A, @DPTR instruction. Data is fetched from the address specified in the 16-bit special function register DPTR.External data memory (XRAM) is a third address space, also starting at address 0. It can also be on or off-chip; what makes it "external" is that it must be accessed using the MOVX (Move external) instruction. Many variants of the 8051 include the standard 256 bytes of IRAM plus a few KB of XRAM on the chip.

The 8051 is designed as a strict Harvard architecture. The 8051 can only execute code fetched from program memory. The 8051 does not have any instruction to write to program memory. Most 8051 systems respect this distinction, and so are unable to download and directly execute new programs. The strict Harvard architecture has the advantage of making such systems immune to most forms of malware. Some 8051 systems have (or can be modified to have) some "dual-mapped" RAM, making them act somewhat more like Princeton architecture. This (partial) Princeton architecture has the advantage of making it possible for a Forth boot loader running on the 8051 to write new native code to RAM and then execute it, leading to faster incremental and interactive programming cycles than strict Harvard systems.

Registers:

The only register on an 8051 that is not memory-mapped is the 16-bit program counter PC. This specifies the address of the next instruction to execute. Relative branch instructions supply an 8-bit signed offset which is added to the PC.8 general-purpose registers R0R7 may be accessed with instructions 1 byte shorter than others. They are mapped to IRAM between 0x00 and 0x1F. Only 8 bytes of that range are used at any given time, determined by the two bank select bits in the PSW.The following registers are memory-mapped into the special function register space:(0x81) Stack pointer SP: This is an 8-bit register used by subroutine call and return instructions. The stack grows upward; the SP is incremented before pushing and decremented after popping a value.(0x8283) Data pointer DP: This is a 16-bit register that is used for accessing PMEM and XRAM.(0xD0) Program status word PSW. This contains important status flags:PSW.0: P Parity: Gives the parity (modulo-2 sum of the bits of) the most recent ALU result.PSW.1: UD User Defined: For general software use, not otherwise used by hardware.PSW.2: OV Overflow flag. Set when addition produces a signed overflow.PSW.3: RS0 Register select 0. The low-order bit of the register bank. Set when banks at 0x08 or 0x18 are in use.PSW.4: RS1 Register select 1. The high-order bit of the register bank. Set when banks at 0x10 or 0x18 are in use.PSW.5: F0 Flag 0: For general software use, not otherwise used by hardware.PSW.6: AC auxiliary carry. Set when addition produces a carry from bit 3 to bit 4.PSW.7: C Carry bit.(0xE0) Accumulator A: This register is used by most instructions.(0xF0) B register: This is used as an extension to the accumulator for multiply and divide instructions.256 single bits are directly addressable. These are the 16 IRAM locations from 0x200x2F, and the 16 special function registers 0x80, 0x88, 0x90 0xF8. Any bit of these bytes may be directly accessed by a variety of logical operations and conditional branches.Note that the PSW does not contain the common N (negative) and Z (zero) flags. Instead, because the accumulator is a bit-addressable SFR, it is possible to branch on its most significant bit directly. There is also an instruction to jump if the accumulator is zero or non-zero.