8051 Instruction Set - ycce.edu · 8/23/2016 1 23-Aug-16 [email protected] 1 8051 Instruction...

-

Upload

trinhnguyet -

Category

Documents

-

view

237 -

download

5

Transcript of 8051 Instruction Set - ycce.edu · 8/23/2016 1 23-Aug-16 [email protected] 1 8051 Instruction...

8/23/2016

1

23-Aug-16 [email protected] 1

8051 Instruction Set

23-Aug-16 [email protected] 2

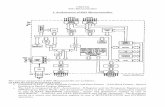

Programmers Model of 8051

Register

Banks

Bit

addressable

General

Purpose

7FH

30H

2FH

20H

1FH

00H

1. A (ACC)

2. B

3. PSW

4. P0 (Port 0)

5. P1 (Port 1)

6. P2 (Port 2)

7. P3 (Port 3)

8. DPH & DPL

9. DPTR

10. SP

11. TH0 & TL0

12. TH1 & TL1

13. TMOD

14. TCON

15. SCON

16. SBUF

17. PCON

18. IE

19. IP

R0 R1 R2

R5 R4 R3

R6 R7

R0 R1 R2

R5 R4 R3

R6 R7

R0 R1 R2

R5 R4 R3

R6 R7

R0 R1 R2

R5 R4 R3

R6 R7

1FH

18H

17H

10H

0FH

08H

07H

00H

Bank 0

(default)

Bank 1

Bank 2

Bank 3

RS1,RS0=00

8/23/2016

2

23-Aug-16 [email protected] 3

Addressing Modes

• General Instruction Format is

Mnemonics <Destination>, <Source>

Operation Operands

• The method by which address of source of data or

address of destination of result is given in the instruction

is called as addressing mode

• The 8051 supports 5 types of addressing modes

1. Immediate addressing mode

2. Register addressing mode

3. Direct addressing mode

4. Indirect addressing mode

5. Index addressing mode

23-Aug-16 [email protected] 4

Addressing Modes (cont..)

1. Immediate addressing mode – If 8/16 bit data required for executing the instruction is given in the

instruction itself then it is called immediate addressing mode

– If hash (#) is used along with the number then it indicates that the

number is a data.

– e.g. MOV R7,#54H ; store data 54H into register R7

54H R7

54H

2. Register addressing mode – If 8/16 bit data required for executing the instruction is present in

8/16 register then name of register is used in the instruction as a

operand then it is called register addressing mode

– e.g. MOV R1, A

A R1

37H 89H 37H

8/23/2016

3

23-Aug-16 [email protected] 5

Addressing Modes (cont..)

3. Direct addressing mode – If 8 bit data required for executing the instruction is present

in memory location and 8 bit address of that memory

location (internal RAM) is directly given in the instruction

then it is called direct addressing mode

– Direct addressing mode is used to give 8 bit address of

internal RAM (00H to 7FH) and address of SFRs (80H to

FFH)

– e.g. MOV A, 65H ; Transfer data of M.L. 65H to Acc

65H 37H

ACC

37H

23-Aug-16 [email protected] 6

Addressing Modes (cont..)

4. Indirect addressing mode – If 8 bit data required for executing the instruction is present in

memory location and address of that memory location

(internal RAM) is present in 8/16 bit register then register

acts as a pointer and it is called indirect addressing mode

– Registers R0 and R1 are used to store 8 bit address of

internal RAM (00H to 7FH) / external RAM.

– DPTR is used to store 16 bit address of external RAM.

– Character @ is placed before the name of register to indicate

that the register contains address.

– e.g. MOV R0, #65H ; store address 65H into register R0

MOV A, @R0 ; Transfer data of M.L. to Acc

37H 65H

65H ACC

R0 37H

8/23/2016

4

23-Aug-16 [email protected] 7

Addressing Modes (cont..)

5. Index addressing mode – Only program memory can be accessed by this mode. This

mode is intended for reading LOOK-UP table in the program

memory.A 16 bit base address (given by DPTR or PC) points

to the base of the look up table and the accumulator carries

the constant indicating table entry number. The address of

the exact location of the table is formed by adding

Accumulator data with the base pointer.

– e.g. MOVC A, @ A+DPTR ; DPTR=0200H, A=05H

A

X5

X1

X3

X2

X4

X5

X6

X0

X7

05

0200 0200H

0201H

0202H

0203H

0204H

0205H

0206H

0207H

DPTR

A

@ DPTR + A

23-Aug-16 [email protected] 8

General name used for operands

• Rn : Register R7-R0 of the currently selected Register Bank.

• direct: 8-bit internal data location’s address. This could be an Internal Data RAM location (0-127) or a SFR [i.e., I/O port,control register, status register, etc. (128-255)].

• @Ri :8-bit internal data RAM location (0-255) addressed indirectly through register R1 or R0.

• #data :8-bit constant included in the instruction.

• #data 16 :16-bit constant included in the instruction

• bit :Direct Addressed bit in Internal Data RAM or Special Function Register.

8/23/2016

5

23-Aug-16 [email protected] 9

• addr 16: 16-bit destination address. Used by LCALL and LJMP instructions. A branch can be anywhere within the 64k-byte Program Memory address space.

• addr 11: 11-bit destination address. Used by ACALL and AJMP instructions. The branch will be within the same 2k-byte page of program memory as the first byte of the following instruction.

• rel : Signed (two’s complement) 8-bit offset byte. Used by SJMP and all conditional jump instructions. Range is –128 to +127 bytes relative to first byte of the following instruction.

General Name for Branching Operands

23-Aug-16 [email protected] 10

Instruction set

• Classification based on type of operation

performed by the instruction

– Data Transfer

• Internal

• External

• Look-up table

• Stack

– Arithmetic

– Logical

– Rotation

– Branching

– Bit Manipulation

8/23/2016

6

23-Aug-16 [email protected] 11

Data Transfer Operation

• 8 bit data is transferred from source to destination

• After the operation, old data of destination is lost and

destination holds new data which is a copy of source

data

Source Destination

Data Data Data

• # <Constant>

• A

• Rn

• direct

• @ Ri

• A

• Rn

• direct

• @ Ri

• DPTR

23-Aug-16 [email protected] 12

Data Transfer Instructions

Mnemonics Operands Bytes/Cycle

MOV A, # data 8 2/1

A, Rn 1/1

A, direct 2/1

A, @Ri 1/1

- MOV A, #45H ; store data 45H into Accumulator

– MOV A, R3

– MOV A, 62H ; Transfer data from M.L. to A

– MOV R1, #62H

– MOV A, @R1 ; Transfer data from M.L. to A

8/23/2016

7

23-Aug-16 [email protected] 13

Data Transfer Instructions

Mnemonics Operands Bytes/Cycle

MOV Rn, # data 8 2/1

Rn, A 1/1

Rn, direct 2/2

- MOV R1, #62H

– MOV R7,A

– MOV R2, 45H ; Transfer data from M.L. to R2

45H 30H

R2

30H

23-Aug-16 [email protected] 14

Data Transfer Instructions (cont..)

Mnemonics Operands Bytes/Cycle

MOV direct, # data 8 3/2

direct, A 2/1

direct, Rn 2/2

direct,direct 3/2

direct, @Ri 2/2

- MOV 65H, #21H ; Store data 21H into M.L.

– MOV 67H, A ;

– MOV 45H, R2 ; Transfer data to M.L. from R2

– MOV 45H, 65H ; Transfer data from M.L. to ML

8/23/2016

8

23-Aug-16 [email protected] 15

Data Transfer Instructions (cont..)

Mnemonics Operands Bytes/Cycle

MOV @Ri, # data 8 2/1

@Ri, A 1/1

@Ri, direct 2/2

DPTR, #data 16 3/2

- MOV R1, #75H ; Store address 75H into R1

– MOV @R1, #37H ; Store data 37H into ML 75H

– MOV @R1, A ; Store ACC into ML 75H

– MOV @R1, 65H ; Transfer data from M.L. to ML

– MOV DPTR, #2150H

23-Aug-16 [email protected] 16

Data Transfer Instructions (cont..)

Mnemonics Operands Bytes/Cycle

MOVX A, @Ri 1/2

A, @DPTR 1/2

@Ri, A 1/2

@DPTR, A 1/2

• MOVX instruction is used for data transfer

between external RAM and 8051.

• e.g. MOV DPTR, #2150H

MOVX A, @DPTR

8/23/2016

9

23-Aug-16 [email protected] 17

Data Transfer Instructions (cont..)

• e.g. MOV DPTR, #2150H

MOVX A, @DPTR

; Transfer data from external RAM location

; 2150H to Accumulator.

data 2150H

DPTR

2150H

A

M.L.

data

8051 External RAM

23-Aug-16 [email protected] 18

Data Transfer Instructions (cont..)

Mnemonics Operands Bytes/Cycle

MOVC A, @A+DPTR 1/2

A, @A+PC 1/2

• MOVC instruction is used for data transfer from

Program Memory to ACC.

e.g.Transfer 6th data from Lookup table to Accumulator

Starting address of Lookup table is 0200H

MOV DPTR, #0200H ; Base address of LT

MOV A, #05H ; Get 6th entry from LT

MOVC A, @A+DPTR

8/23/2016

10

23-Aug-16 [email protected] 19

Data Transfer Instructions (cont..)

• e.g. MOV DPTR, #0200H

MOV A, #05H

MOVC A, @A+DPTR

; Transfer data from Lookup table location to

Accumulator.

8051

Program Memory

X1

X3

X2

X4

X5

X6

X0

X7

0200 0200H

0201H

0202H

0203H

0204H

0205H

0206H

0207H

DPTR

@ DPTR + A

A 05 X5

23-Aug-16 [email protected] 20

Data Transfer Instructions (cont..)

Mnemonics Operands Bytes/Cycle

XCH A, Rn 1/1

A, direct 2/1

A, @Ri 1/2

• e.g. XCH A, R3 ; Exchange data of R3

; with Accumulator

• e.g. XCH A, 45H ; Exchange data of ML

; with Accumulator

ACC R3

8/23/2016

11

23-Aug-16 [email protected] 21

Data Transfer Instructions (cont..)

• Exchange 4 LSB of internal RAM with 4 LSB of Acc.

• e.g. Exchange 4 LSB of M.L. 62H with 4 LSB of Acc

– MOV R0, #62H

– XCHD A, @R0

A 62H 59 37 Before

A 62H 57 39 After

Mnemonics Operands Bytes/Cycle

XCHD A, @Ri 1/1

23-Aug-16 [email protected] 22

Stack Pointer (SP)

• Stack Pointer (SP)

SP is 8 bit register. It holds address of top of the stack. Only internal

128 bytes RAM can be used as a stack memory for storing stack of

data. In 8051 the data is pushed into stack memory from lower

address towards higher address. (Opposite of 8085)

At power ON RESET 07H is stored in SP.

7FH

09H

08H

07H

00H

07H

SP

First data is

Pushed here

8/23/2016

12

23-Aug-16 [email protected] 23

Data Transfer Instructions (cont..)

Mnemonics Operands Bytes/Cycle

PUSH direct 2/2

• Push (store) 8 bit data of RAM Location into

stack memory

• e.g. PUSH 45H 7FH

09H

08H

07H SP(old)

SP(new)

45H 37H

37H

23-Aug-16 [email protected] 24

Data Transfer Instructions (cont..)

Mnemonics Operands Bytes/Cycle

POP direct 2/2

• POP (get) 8 bit data from stack top

• e.g. POP 45H

SP(new)

45H 37H

SP(old)

7FH

09H

08H

07H

37H

8/23/2016

13

23-Aug-16 [email protected] 25

Arithmetic Instructions

Mnemonics Operands Bytes/Cycle

ADD A, # data 8 2/1

ADDC A, Rn 1/1

SUBB A, direct 2/1

A, @Ri 1/1

• e.g. ADD A, #39H ;add immediate data

• ADD A, R2 ;add 8 bit data of R2

• ADD A, 39H ;add 8 bit data of ML

• ADDC A, #32H ;add with carry

• SUBB A, R3 ;Subtract with borrow

A – R3 – CF = A

23-Aug-16 [email protected] 26

Arithmetic Instructions

Mnemonics Operands Bytes/Cycle

INC A 1/1

DEC Rn 1/1

direct 2/1

@Ri 1/1

• Increment Acc/Reg/ML by 1

• INC A ; A = A + 1

• Decrement Acc/Reg/ML by 1

• DEC R2 ; R2 = R2 - 1

8/23/2016

14

23-Aug-16 [email protected] 27

Arithmetic Instructions (cont..)

Mnemonics Operands Bytes/Cycle

MUL AB 1/4

DIV AB 1/4

DA A 1/1

e.g. MUL AB ;

DIV AB ;

DA A ; Convert Invalid BCD in Acc to

; Valid BCD

A A B B X =

A B B A / =

Q R