555 Timer ©Paul Godin Updated February 2008. Oscillators ◊We have looked at simple oscillator...

-

Upload

carrie-isbell -

Category

Documents

-

view

219 -

download

0

Transcript of 555 Timer ©Paul Godin Updated February 2008. Oscillators ◊We have looked at simple oscillator...

555 Timer

©Paul GodinUpdated February 2008

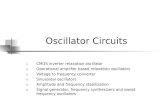

Oscillators

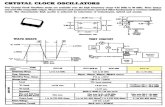

◊ We have looked at simple oscillator designs using an inverter, and had a brief look at crystal oscillators.

◊ In this presentation, we introduce the 555 timer; a versatile device that is easier to calculate, design and configure in a variety of ways.

555.2

A Versatile Device

◊ The 555 Timer is one of the best known IC’s.◊ The 555 is part of every experimenter's tool kit

◊ Capable of creating a wide variety of circuits, including:◊ Oscillators with adjustable frequency and Duty Cycle◊ Monostable Multivibrators◊ Analog to digital Converters◊ Frequency Meters◊ Many other applications….

◊ The clock on the Vulcan Board is generated by a 555 timer.

555.3

555 Timer Configurations

◊ In this course we will use the 555 timer in 2 modes:◊ Astable

◊ With some calculations, we can determine the values of the capacitor and the 2 resistors (Ra and Rb) for astable operations.

◊ Monostable◊ We can determine the value of the resistor and the

capacitor with a simple formula for one-shot operations.

◊ There are many other configurations and applications for this device.

555.4

555 Layout

Also available:•556 (two-555’s in one DIP package)•555 in a “metal can” configuration

555.5

1234

8765

Ground

Trigger

Output

Reset

Vcc

Discharge

Threshold

Control

1

2

34

5

6

78

Ground

Trigger

Output

Reset

Vcc

Discharge

Threshold

Control

Op

era

tion

of

the 5

55

Tim

er

Asta

ble

Mu

ltiv

ibra

tor

555.6

Oscillator Configuration

◊ Externally, the 555 requires an RC circuit to create the time delays required for the time high and the time low.

◊ Standard configuration requires◊ common capacitor◊ a resistor for the charge cycle◊ a resistor for the discharge cycle

555.7

General Configuration

◊ Basic connections:◊ Ground◊ Vcc

◊ Note: some 555 timers may function at voltages other than 5 volts.

◊ Reset (active low)◊ Output

555.8

1234

8765

Ground

Trigger

Output

Reset

Vcc

Discharge

Threshold

Control

General Configuration

◊ Specialized connections:◊ Trigger

◊ monitors low voltage◊ Threshold

◊ monitors high voltage◊ Discharge

◊ path to ground, to discharge the capacitor

◊ Control◊ specialized input

◊ filtering◊ special applications

555.9

1234

8765

Ground

Trigger

Output

Reset

Vcc

Discharge

Threshold

Control

Astable Configuration #1(“Standard” Configuration)

1234

8765

Ground

Trigger

Output

Reset

Vcc

Discharge

Threshold

Control

Vcc

Ra

Rb

C

Vcc

555.10

Astable

Filter Cap0.01μF

Calculated

Values

Note: Duty Cycle must be > 50%

555.11

Astable Configuration #1(“Standard” Configuration)

Rb2RaRbRa

ttt

DC21

1

C)Rb2Ra(693.1

tt1

f21

CRb693.t

C)RbRa(693.t

2

1

Minimum duty cycle > 50%

555.12

Calculations: Astable

C)RR(693.0T

CR693.0T

BAH

BL

TH TL

Notes:•The value 0.693 is a factor associated with thecharge/discharge cycle of the 555 timer.

•Duty Cycle must be > 50%

Time High, Time Low Set

555.13

555.14

Sample Calculation

◊ Design an oscillator with a frequency of 200Hz with a duty cycle of 78%.1. Determine Period (T):

2. Determine TH and TL:

s005.0Hz200

1F1

T

ms1.1s0011.0s005.0%22T

ms9.3s0039.0s005.0%78T

L

H

Time High, Time Low Set

555.15

3. Since there are 2 variables in the TL equation, select C:

4. Determine RB by using the TL equation:

7.158R

F10R693.0ms1.1

CR693.0T

B

B

BL

C=10μF

Sample Calculation

Time High, Time Low Set

555.16

5. Determine the value for RA:

1.404R

7.158R8.562

F10)7.158R(693.0ms9.3

C)RR(693.0T

A

A

A

BAH

Sample Calculation

Time High, Time Low Set

Calculations: Astable

C)R2R(693.01

F

)R2R()RR(

DC

BA

BA

BA

Notes:•The value 0.693 is a factor associated with thecharge/discharge cycle of the 555 timer.

•Duty Cycle must be > 50%

Frequency, Duty Cycle Set

555.17

Sample Design

◊ Build an oscillator using a 555 timer with a frequency of 72kHz at 75% D.C. Use a 100F capacitor.

Frequency, Duty Cycle Set

555.18

Design Solution

1- Determine the ratio of the resistors Ra and Rb:

2- Use the ratio in the frequency equation (substitution):

Rb2Ra

RbRb5.1Ra75.0Ra

Rb5.1Ra75.0)Rb2Ra(75.0RbRa

75.0Rb2RaRbRa

DC

RbC444.1

C)Rb2Rb2(44.1

C)Rb2Ra(44.1

f

Frequency, Duty Cycle Set

555.19

Design Solution

3- Solve for Rb:

4-Solve for Ra:

5-Use standard values (optional step):Ra=100kRb=47k

k50100k724

44.1RbC444.1

kHz72

k100Rb2Ra

Frequency, Duty Cycle Set

555.20

Design Solution

6- Calculate actual frequency and DC:

%1Error

757.0))k472(k100(

)k47k100(DC

%1.3Error

kHz2.74F100))k472(k100(

44.1f

Frequency, Duty Cycle Set

555.21

Design Solution

7- Create the circuit diagram using EWB:

555 Timer, 74.2kHz @ 75.7% D.C.

Frequency, Duty Cycle Set

555.22

Minimum Value for RaMinimum Value for Ra

◊ The discharge transistor causes the capacitor to discharge to ground.

◊ Ra must have a minimum value of 25 to prevent a short circuit of the power supply through the discharge transistor.

Minimum Value

555.23

In-Class Practice Problem

◊ Design an oscillator with a frequency of 500Hz and a duty cycle of 80%. Use a 10μF Capacitor. Calculate using each of the equation sets.

555.24

OTHER ASTABLE CONFIGURATIONS

555.25

Astable Configuration#2

Rb must be < .5 Ra

555.26

Astable Configuration #3

555.27

555 Timer Operation

555.28

Internal Operation of the 555 Timer

◊ Understanding the internal operation of the 555 timer is important◊ The device combines various circuit theories.

◊ Various aspects provide a preview of other circuits, such as the Analog to Digital decoders.

◊ Understanding its internal function makes it easier to create new designs with the device.

555.29

Comparator

◊ The comparator is an operational amplifier (op-amp) configuration.

◊ The comparator compares 2 analog voltages and provides a digital output.

+

-If V+ > V-, the output is a digital 1

If V- > V+, the output is a digital 0

555.30

Reference and Comparators

The Comparators provide digital logic

to an SR Latch

Comparators compare voltage levels.

•If “+” is higher, output = 1•If “-” is higher, output = 0

A 3-resistor voltage divider

provides reference voltages

555.31

Reference and Comparators

Pin 8: Vcc connection

Pin 5: “Control” connection,

used with filter cap.

Pin 1: Gnd connection

Pin 6: “Threshold” connection (high

Comparator)

Pin 2: “Trigger” connection (low

Comparator)

555.32

Latch and Output

The Q’ output controls the transistor (“on” or

“off”).The SR Latch

holds its output states

The transistor acts like a switch.

The reset input can be used to enable or disable the timer.

The buffer has important electrical functions.

555.33

Latch and Output

Pin 4: Reset connection (active

low reset)

Pin 7: “Discharge” connection

Pin 3: Digital Output

555.34

Charge Animation Discharge Animation555.35

Specification sheet

◊ From the specification sheet for the LM555, determine the following:◊ Operational voltage range◊ Maximum current output for each state

◊ Frequency Range◊ Output rise and fall time

What is a disadvantage of the 555 as a timing device?

555.36

Function of the Control Input (Pin5)

◊ Pin 5 is the control voltage connection, and is used to access the 2/3 Vcc point of the voltage divider. ◊ Normally, a 0.01F capacitor is connected to ground to

provide output voltage stability.◊ Used as an input for some applications.

◊ AC to pulse modulation◊ voltage controlled oscillator

555.37

Design Exercises

555.38

Design Exercises

1. Using a 555 timer, design an oscillator with an output of 6Hz with a duty cycle of 60%. Use a 100μF capacitor. Build in EWB.

2. Using a 555 timer, design an oscillator with an output of 10KHz with a duty cycle of 50%. Use a 3.3μF Capacitor. Build in EWB.

555.39

Animated SlidesThe following slides contain animations to

demonstrate the operations of:555 as an astable: charge cycle

555 as an astable: discharge cycle

555.40

+ < -

0

- < +

1

Vc

0

1

Animated charge cycle

+ > -

1

- > +

0 1

0

Capacitor Charges via Ra and RbLatch in a set stateQ’ is low; Q output is highCapacitor continues to chargeLower comparator provides logic low. Latch in hold state.

Upper comparator + input is greater than 2/3 Vcc reference

Latch receives a reset stateQ’ is high; Q output is lowTransistor is “on” and a connection to ground is made.Capacitor begins to discharge

555.41

Vc

1

01

0+ < -

- < +

Animated discharge cycle

01

+ > -

0

- > +

1

Capacitor is discharging. Q output is low.

Upper comparator + voltage less than reference voltage.

Latch in a hold state.Lower comparator + voltage is greater than – voltage.Latch is set. Q’ is low. Q output is high.Transistor is “off”. Capacitor

begins to charge.

555.42

©Paul R. Godinprgodin°@ gmail.com

555.43

END