5 Gbps J. SMU 1 A Serializer for LAr Front-end electronics upgrade 1.Requirements and design...

-

Upload

laureen-montgomery -

Category

Documents

-

view

213 -

download

0

description

Transcript of 5 Gbps J. SMU 1 A Serializer for LAr Front-end electronics upgrade 1.Requirements and design...

J. Ye @ SMU 1

16:1@

5 Gbps

A Serializer for LAr Front-end electronics upgrade

1. Requirements and design philosophy.

2. Key features of the serializer.3. Design status.4. Work plan towards submission in

August.

Present the design work by D.Gong and Andy T.Liu at SMU

J. Ye, SMU Physics Report on the LOC ASIC LAr week at CERN, May 2009 2

16:1@

5 Gbps

1. Req. + design2. Key features.3. Design status.4. Work plan.

Requirements Data rate:

Raw data per FEB: 128 (ch) * 14 (12 bits + 2 gain bits) * 40 Msps = 72 Gbps.

With 64/66 encoding: 74 Gbps With 20% channel (5:6) redundancy: 89 Gbps With other overhead: control words, error det/cor., ~100 Gbps Another perspective:

12 fiber channel @ 8 Gbps = 96 Gbps 12 fiber channel @ 9 Gbps = 108 Gbps We need 8 – 9 Gbps in each channel for a 12 fiber ribbon,

or 6 – 7 Gbps for a 2×8 fiber ribbons. Radiation tolerance: for the moment a simple ×10 is used

that leads to ~4 Mrad for TID. Power: FEB power budget 80 W. Assuming 20 W for the

optical link: 2 W for the interface, 9 W for serialization and 9 W for optical interface ~100 mW/Gbps for serialization and 100 mW/Gbps for optical interface.

System reliability: channel redundancy is a must. Studies needs to be carried out to decide on the scheme.

System latency: the smaller the better.

J. Ye, SMU Physics Report on the LOC ASIC LAr week at CERN, May 2009 3

16:1@

5 Gbps

1. Req. + design2. Key features.3. Design status.4. Work plan.

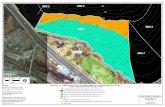

Design Philosophy The Link-on-Chip (LOC) ASIC is a 16:1 serializer at 5+ Gbps

serial output, for this submission. Radiation tolerance is based on the silicon-on-sapphire

technology, no special radiation hardening techniques are used in the design at this moment.

We aim for a simple design that provides the highest user data bandwidth with low latency and low power consumption.

The VTx is used to interface with the fiber. The VTx is being developed in the Versatile Link project.

We plan to use a Serdes embedded FPGA for the receiver. Need another user interface chip that:

Couples to the user data. The user data format and rate are unknown at this stage, and are different in each sub-systems (i.e., silicon, LAr, etc).

Provide an encoding and DC balance scheme (64/66). This user interface will first be realized in an FPGA.

LOCA 16:1 serializer

User Interface

VTx(SPF+)

user data

user clk

16 bit

312.5 MHz

CML5Gbps

fiberLVDS

J. Ye, SMU Physics Report on the LOC ASIC LAr week at CERN, May 2009 4

16:1@

5 Gbps

1. Req. + design2. Key features.3. Design status.4. Work plan.

For the August Submission Thanks to Mauro’s visit to SMU two weeks ago

to go through all technical details in the design. Further reviews will be organized before the submission.

Die size: 3 mm × 3 mm, ~120 chips. Designs to be included:

The 16:1 serializer with a ring oscillator based PLL clock unit to gain experience on the full serializer design.

An LC based PLL and a stand-alone CML output driver to probe the highest possible speed that we can reach with the chosen technology.

Other test structures for future developments.

J. Ye, SMU Physics Report on the LOC ASIC LAr week at CERN, May 2009 5

16:1@

5 Gbps

1. Req. + design2. Key features.3. Design status.4. Work plan.

Key features of the serializer A straightforward 16:1 serializer and the design is optimized for 5

Gbps output data rate. Input data and the reference clock are in LVDS. The reference

clock is 312.5 MHz. The output is CML, and 5 Gbps (the current design). Bit error rate better than 1×10-12. Single power supply at 2.5 V and power consumption is below 400

mW or less than 80 mW/Gbps. CMOS control signals to select the reference edge to be locked in

by the PLL, and to adjust the charge-pump current to achieve the best PLL performance.

LVD

S-To-CM

OS

DFF

DFF2:1

DFF

DFF2:1

… 16:8 M

AX

…

… 8:4 M

AX

…

… 4:2 M

AX

…

DFF

DFF2:1

CM

L driver

2.5 GHz PLL + clock fan-out

16 bitLVDS

312.5 MHz

312.5 M 625 M 1.25 G 2.5 G

5 Gbps

The basic serializing unit is a 2:1 multiplexer that comprises two D-flip-flop and one 2:1 MUX circuit. All stages in the cascade of 2:1 multiplexing are the same except the last stage. This is the only stage that works at the 2.5 GHz clock, assuming a 5 Gbps output. This design lets us concentrate our effort on the very last stage.

The LOC block diagram

J. Ye, SMU Physics Report on the LOC ASIC LAr week at CERN, May 2009 6

16:1@

5 Gbps

1. Req. + design2. Key features.3. Design status.4. Work plan.

Design status – the LOC Full schematics level simulation has been performed. All function blocks have gone through post-layout

simulation to meet the 5 Gbps data rate requirement. Timing is carefully adjusted in the serializer unit. These simulations include all 5 production variation corners, but not temperature variations.

We are “assembling” all the function blocks into the LOC this week. Whole chip simulation is expected be finished by the end of May.

The design document will be updated by June 10 for reviews.

We would like to finish up some fine tuning in the PLL after we send out the design document to reviewers.

The serializer unit

LVD

S to

CM

OS

The PLL and clock fan-out

CM

L ou

tput

driv

er

J. Ye, SMU Physics Report on the LOC ASIC LAr week at CERN, May 2009 7

16:1@

5 Gbps

1. Req. + design2. Key features.3. Design status.4. Work plan.

Design status – the LCPLL and the CML driver for 10 Gbps

Schematics level design on the LCPLL is completed. Post-layout simulations are performed on the VCO and

on the first stage divider. The results: VCO frequency range: 4.24 – 5.27 GHz (TT corner) VCO phase noise: typical at -120 dBc/Hz, worst at -90

dBc/Hz. Better than that of the ring oscillator VCO. VCO gain at 0.8 GHz/V, close to the ring oscillator VCO at

1.1 GHz/V, so the charge pump can be the same. The differential first stage divider: 6.1 GHz at all corners.

We plan to “recycle” the PFD, CP, LPF and most part of the divider in the ring oscillator PLL into the LCPLL.

The CML driver is checked with post-layout simulation to work up to 5 GHz, marginal for 10 Gbps data rate. More tuning will be needed after we finish the LCPLL design.

The plan is to finish this PLL design by the end of May to match the schedule of the LOC for reviews.

PFD

The divider + fan-out chain

CP LPF VCO

J. Ye, SMU Physics Report on the LOC ASIC LAr week at CERN, May 2009 8

16:1@

5 Gbps

1. Req. + design2. Key features.3. Design status.4. Work plan.

Work plan First round of complete post-layout simulation by the

end of May. Design document update: by June 10. Design review: by the end of June. Fine tuning (mostly in the two PLLs) and the CML

driver improvement: June 11 – June 30. Implementing feedbacks from design reviews: July Submission: August 3 – 15. A long vacation (yes, this should be in the work plan). Preparation for testing the chip: mid Sept. to end of

Oct. Test the chip: this winter to the next spring.

J. Ye, SMU Physics Report on the LOC ASIC LAr week at CERN, May 2009 9

16:1@

5 Gbps

1. Req. + design2. Key features.3. Design status.4. Work plan.

Backup Slides

J. Ye, SMU Physics Report on the LOC ASIC LAr week at CERN, May 2009 10

16:1@

5 Gbps

1. Req. + design2. Key features.3. Design status.4. Work plan.

The SOS technology Technology

The ASIC development is based on the 0.25 μm silicon on sapphire (SOS) technology, the UltraCMOSTM GC process from Peregrine Semiconductors Corp.

This SOS technology has been evaluated to be radiation tolerant in our applications for the LAr and the Inner Detector upgrade with the sapphire substrate grounded. It has a fT of 90 GHz which is much faster than that of the bulk silicon CMOS with the same feature size.

OKI technical Review, Oct.2004/Issue 200 Vol.71 No.4, posted at http://www.oki.com/en/otr/200/downloads/otr-200-R18.pdf