4. ANALYSIS & DESIGN OF COMBINATIONAL...

-

Upload

nguyendien -

Category

Documents

-

view

218 -

download

1

Transcript of 4. ANALYSIS & DESIGN OF COMBINATIONAL...

Analysis & Design of Combinational Logic 4 -1

Logic Design © Dong-Seog Han

4. ANALYSIS & DESIGN OF

COMBINATIONAL LOGIC

Objectives

1. Study a general approach to designing combinational logic circuits (decoders,

encoders, multiplexers, adders, subtractors, multipliers, comparators, parity

generators, and tristate buffers).

2. Study some of the problems associated with the logic devices.

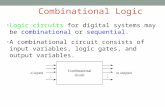

4.1 Definitions of Combinational & Sequential Logic

P ro b le m

S ta te m e n t

T ru th T a b le

C o n s tru c tio n

S w itch in g

E q u a tio n s

E q u a tio n

S im p lif ica tio n

L o g ic

D ia g ra m

D ra w n

L o g ic C ir cu it

B u ilt

Ex. Two input two-bit binary multiplier

1. input 1: 01 , AA , input 2: 01 , BB , output: 0123 ,,, PPPP

2. Truth table

Inputs Outputs

1A

0A

1B

0B

3P

2P

1P

0P

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

1

1

0

0

1

0

0

0

0

0

0

0

1

1

0

1

0

1

0

1

1

0

0

0

0

0

0

1

0

1

0

0

0

0

0

1

0

1

Analysis & Design of Combinational Logic 4 -2

Logic Design © Dong-Seog Han

3. Boolean equations

3 1 0 1 0 1 0 1 0, , , 1 5P f A A B B A A B B

2 1, 0 1 0, ,

1 0 ,1 1,1 4

P f A A B B

1 1, 0 1 0, ,

6 , 7 , 9 ,1 1,1 3 ,1 4

P f A A B B

0 1, 0 1 0, ,

5 , 7 ,1 3 ,1 5

P f A A B B

11 10

23

A0

A1A0B1B0

00 01

0 1

B0

674 5

1141512 13

1 110118 9

00

01

11

10

A1

B1

11 10

23

A0

A1A0B1B0

00 01

0 1

B0

1 1674 5

11415

112 13

11011

18 9

00

01

11

10

A1

B1

11 10

23

A0

A1A0B1B0

00 01

0 1

B0

167

14 5

11415

112 13

10118 9

00

01

11

10

A1

B1

4. Logic diagram

Ex. 2421BCD code input to decimal display

A

B

C

D

E

F

G

T IL -3 1 2 c o m m o n -

a n o d e 7 -s e g m e n t

L E D d is p la y

2 4 2 1 c o d e -

to -

7 -s e g m e n t

d e c o d e r/

d r iv e

+ V c c

w

x

y

z

+ V c c

/A = A .L

/B = B .L

/C = C .L

/D = D .L

/E = E .L

/F = F .L

/ G = G .L

A c t iv e L o w

O u tp u t

<Light-emitting diode, Seven-segment display>

Analysis & Design of Combinational Logic 4 -3

Logic Design © Dong-Seog Han

Truth table

Inputs Outputs

w x y z /A /B /C /D /E /F /G

0 0

1

1

1

1

1

1

1

1

0 0

0

0

0

0

1

1

1

1

0 0

0

0

1

1

0

0

1

1

0 1

0

1

0

1

0

1

0

1

Boolean equations

. , , ,

A A L f w x y z

d

11 10

23

x

wxyz

00 01

0 1

z

674 5

141512 13

10118 9

00

01

11

10

w

y

, , ,

B f w x y z

d

11 10

23

x

wxyz

00 01

0 1

z

674 5

141512 13

10118 9

00

01

11

10

w

y

, , ,C f w x y z

11 10

23

x

wxyz

00 01

0 1

z

674 5

141512 13

10118 9

00

01

11

10

w

y

, , ,D f w x y z

11 10

23

x

wxyz

00 01

0 1

z

674 5

141512 13

10118 9

00

01

11

10

w

y

Analysis & Design of Combinational Logic 4 -4

Logic Design © Dong-Seog Han

, , ,E f w x y z

11 10

23

x

wxyz

00 01

0 1

z

674 5

141512 13

10118 9

00

01

11

10

w

y

, , ,F f w x y z

11 10

23

x

wxyz

00 01

0 1

z

674 5

141512 13

10118 9

00

01

11

10

w

y

, , ,G f w x y z

11 10

23

x

wxyz

00 01

0 1

z

674 5

141512 13

10118 9

00

01

11

10

w

y

Logic Diagram

4.2 Introduction to Digital Integrated Circuits

ICs by no. of gates

Small-scale ICs (SSI) ~10 equivalent two-input gates (74 series)

Medium-scale ICs (MSI) ~ 100 gates

Large-scale ICs (LSI) ~ 1,000 gates

Very large-scale ICs (VLSI) ~ thousands of equivalent gates

ULSI Pentium II (750 million Trs.)

Digital Logic Families (Composed of NAND, NOR, and NOT)

RTL DTL TTL (Transistor Transistor Logic) ECL (Emitter Coupled Logic)

MOS (Metal-Oxide Semiconductor) CMOS (Complementary MOS, low power,

dominant technology) Bi-CMOS (Bipolar CMOS, more fast than CMOS)

Analysis & Design of Combinational Logic 4 -5

Logic Design © Dong-Seog Han

Digital IC Terminology

Current & voltage parameters

+

-OHV

IHV-

+

O HI

IHI

+

-O LV ILV

-

+

O LI ILI

+ 5 V

m inIHV - High-level input voltage

m axILV - Low-level input voltage

m inOHV - High-level output voltage

m axO LV - Low-level output voltage

IHI - High-level input current

ILI - Low-level input current

O HI - High-level output current

O LI - Low-level output current

Fan-out (loading factor): the maximum number of standard logic inputs that an output

can drive reliably

Ex. Find the fan-out of a 74ALS IC with

0 .2 , 2 0 , 8 , 4 0 0IL IH O L O HI m A I A I m A I A .

O u tp u t

v o lta g e

D is a llo w e d

r a n g e

m inO HV

m a xO LV

L o g ic 0

L o g ic 1

L o g ic 0

L o g ic 1

m a xILV

m inIHV

In p u t

v o lta g e

N HV

N LV

2 .7 V

(4 .9 V )

0 .5 V

(0 .1 V )

2 .0 V

(3 .5 V )

0 .8 V

(1 .5 V )

T T L (C M O S )

V c c= V d d = + 5 V

Fan-out=400/20=20

L

8 m A 0 .2m A

Fan-out=8/0.2=40

F an -o u t: m in 2 0 ,4 0 2 0

Analysis & Design of Combinational Logic 4 -6

Logic Design © Dong-Seog Han

Fan-in: Required input current, number of inputs

Propagation delays

In p u t

lo g ic le v e l

PH Lt

P LHt

O u tp u t

lo g ic le v e l

0

0

0

1

1

1

5 0 %

5 0 %

In p u t O u tp u t

,

m axD P PH L P LHt t t

Noise margin (immunity)

O u tp u t

v o lta g e

D is a llo w e d

r a n g e

m inO HV

m a xO LV

L o g ic 0

L o g ic 1

L o g ic 0

L o g ic 1

m a xILV

m inIHV

In p u t

v o lta g e

N HV

N LV

2 .7 V

(4 .9 V )

0 .5 V

(0 .1 V )

2 .0 V

(3 .5 V )

0 .8 V

(1 .5 V )

T T L (C M O S )

V c c= V d d = + 5 V

Why we use the active low output?

TTL Family

- Developed in 1963

- 54xx: military 125~55 , 74xx: commercial 70~0

- c.f. IC for Communications 85~45

- 74H (High-speed TTL), 74LP (Low-power TTL), 74S (Schottky TTL)

- 74LS (Low-power Schottky), 74AS (Advanced Schottky): 2 times faster than 74S

- 74F (Fast TTL), 74ALS (Advanced low-power Schottky TTL)

Analysis & Design of Combinational Logic 4 -7

Logic Design © Dong-Seog Han

4.3 Decoders: min-term generator

A combinational logic that converts binary information from n input lines to a

maximum of n2 unique output lines.

Minterm generator

Demultiplexer: a decoder with an enable input

n -d a ta

in p u ts

E n a b le

in p u ts

02

12

2N -1

0

n -to -m

D e co d e r

1m

P o s s ib le

O u tp u ts

2n

m

(1) Dual 2-to-4 Decoder with Enable Input (TTL 74xxx139)

Inputs Outputs

12E N

1 A1 B1 G '

2

1

X / Y

7 4 L S 1 3 9

2 A2 B2 G '

1 41 31 5

4567

1 21 11 09

1 Y 3

1 Y 01 Y 11 Y 2

2 Y 3

2 Y 02 Y 12 Y 2

3

IEEE logic symbol

Enable Select

G’ B A Y0 Y1 Y2 Y3

1

0

0

0

0

X

0

0

1

1

X

0

1

0

1

0 0 , 1 1

2 2 , 3 3

Y Y Y Y

Y Y Y Y

E N A B L E

A

2 - to -4

D e c o d e r

B

02

12

G '

Y 0

Y 1

Y 2

Y 3

0

1

2

3

Analysis & Design of Combinational Logic 4 -8

Logic Design © Dong-Seog Han

(2) A 3-to-8 Decoder constructed with two 2-to-4 Demultiplexers

E N A B L E

2 -to -4

D e c o d e r0

2

12

D 0

D 1

D 2

D 3

E N A B L E

2 -to -4

D e c o d e r0

2

12

D 4

D 5

D 6

D 7

A 0

A 1

A 2

(3) 74xxx138 3-to-8 Demultiplexer

12

ABC

B IN / O C T7 4 L S 1 3 8

G 1/ G 2 A/ G 2 B

0

123

4

5

67

Y 3

Y 0Y 1Y 2

Y 7

Y 4Y 5Y 6

4

E N

&

IEEE logic symbol

A

B

U 1

7 4 L S 1 3 8

G 1

G 2 A

G 2 B

3

0

1

2

7

4

5

6

C

(4) Design a binary 3-bit adder with a 74xxx138 and NAND gates.

, , 1, 2 , 4 , 7 , , , 3 , 5 , 6 , 7S f x y z C f X Y Z

A

B

U 1

7 4 L S 1 3 8

G 1

G 2 A

G 2 B

3

0

1

2

7

4

5

6

C

V c c

zyx

S

C

Analysis & Design of Combinational Logic 4 -9

Logic Design © Dong-Seog Han

4.4 Encoders

Inverse function of decoders

K e y p a d E n c o d e r

D e c im a l B C D

C P U

B C D

D e c o d e r

B in a y7 S e g .

D is p la y

D r iv e r

C a lc u la to r

in p u ts

E n a b le

in p u ts

0

E n co d e r

n -1

O u tp u ts

B in a ry

C o d e

0

1

2 1n

2n

(1) Octal-to-binary Encoder

Inputs Outputs

D7 D6 D5 D4 D3 D2 D1 D0 A2 A1 A0

0 0

0

0

0

0

0

1

0 0

0

0

0

0

1

0

0 0

0

0

0

1

0

0

0 0

0

0

1

0

0

0

0 0

0

1

0

0

0

0

0 0

1

0

0

0

0

0

0 1

0

0

0

0

0

0

1 0

0

0

0

0

0

0

0 , 1 A A

D 0

D 1

D 2

D 3

D 4

D 5

D 6

D 7

A 2

A 1

A 0

Ambiguities:

if D3 & D6 are 1 simultaneously, the output is 111.

All inputs=0 A2A1A0=000, D0=1

A2A1A0=000; requires one more output to

indicate that at least one input is equal to 1.

Analysis & Design of Combinational Logic 4-10

Logic Design © Dong-Seog Han

(2) Decimal-to-BCD Encoder (74xxx147)

Inputs Outputs 1 2 3 4 5 6 7 8 9 D C B A 1 0 x x x x x x x x

1 1 0 x x x x x x x

1 1 1 0 x x x x x x

1 1 1 1 0 x x x x x

1 1 1 1 1 0 x x x x

1 1 1 1 1 1 0 x x x

1 1 1 1 1 1 1 0 x x

1 1 1 1 1 1 1 1 0 x

1 1 1 1 1 1 1 1 1 0

A

2

3

4

5

6

7

8

9

1

1

2

4

8

B

C

D

7 4 L S 1 4 7

U 1

H P R I/B C D

+ 5 V

(3) Priority Encoder

4-input priority encoder

Inputs Outputs

/V=0 indicates that all the inputs are 0.

D3 D2 D1 D0 A1 A0 /V 0 0 0 0 1

0 0 0 1 X

0 0 1 X X

0 1 X X X

Where we can use the priority encoder? Several possible events may occur in an

industrial system, and you want to identify an event and assign and transmit a code to

the control unit based on some priority.

11 10

23

D2

D3D2D1D0

00 01

0 1

D0

674 5

141512 13

10118 9

00

01

11

10

D3

D1

1A

11 10

23

D2

D3D2D1D0

00 01

0 1

D0

674 5

141512 13

10118 9

00

01

11

10

D3

D1

2A

11 10

23

D2

D3D2D1D0

00 01

0 1

D0

674 5

141512 13

10118 9

00

01

11

10

D3

D1

/V

Analysis & Design of Combinational Logic 4-11

Logic Design © Dong-Seog Han

4.5 Digital Multiplexers

S o u r c e A

S o u r c e B

S o u r c e C

S o u r c e D

S e le c t

S w itc h

E n a b le

S w itc h

D a ta

O u tp u t

In p u ts

0S

1Sn -1S

O u tp u t

S e le c t

Y

E N

M U X

-12n

0I

1I

2 1nI

(e.g.) 74xx153 Dual 4-1 multiplexer, 74xx151: Single 8-to-1, 74xx150: 16-to-1 multiplexer

1 4

2

1

6

5

4

3

1 5

1 0

1 1

1 2

1 3

0

1

0

1

2

3

M U X

7 4 L S 1 5 3

7

9

D a ta

O u tp u t

S e le c t

In p u ts

E n a b le

D a ta

In p u ts

G3

0

E N

(1) 4-to-1 Line Multiplexer

Block diagram

0

1

2

3

14

M U X

0S

1S

YO u tp u t

In p u ts

S e le c t

I0

I1

I2

I3

Truth table

Inputs Output

I3 I2 I1 I0 S1 S0 Y

0

0

0

1

1

0

0

0

0

1

0

0

0

0

1

0

0

1

0

1

0

0

1

0

1

0

1

0

0

1

Analysis & Design of Combinational Logic 4-12

Logic Design © Dong-Seog Han

Function table: Condensed truth

table

S1 S0 Y

0

0

1

1

0

1

0

1

I0

I1

I2

I3

Logic diagram

I0

I1

I2

I3

S 1

S 0

Y

(2) 4-bit 4-to-1 Mux

0

1

0

1

2

3

M U X

7 4 L S 1 5 3

G3

0

E N

U 1

0

1

0

1

2

3

M U X

7 4 L S 1 5 3

G3

0

E N

U 1

Y 3

Y 2

Y 1

Y 0

A

B

E n a b le

IA 3

IB 3

IC 3

ID 3

IA 2

IB 2

IC 2

ID 2

IA 2

IB 2

IC 2

ID 2

IA 1

IB 1

IC 1

ID 1

(3) Combinational Circuit Implementation

Boolean function of N variables: 1 2 1 0, , ..., ,

n nv v v v

(i) Connect the n-1 variables to the

selection line of the MUX

2 0: M SB , , : L SB

nv v

O u tp u t

E N

M U X0I

1I

12 1nI

0v

1v

2nv

1nv

1nv

1

0

Y

2nS

1S

0S

12 1n

Analysis & Design of Combinational Logic 4-13

Logic Design © Dong-Seog Han

(ii) List the inputs of the multiplexer and under them list all the minterms in two rows.

0I

1I

2I

3I

4I

1nv

1nv

0

2 / 2n

1

2 / 2 1n

2

2 / 2 1n

2 / 2 1n

2 1n

(iii) Circle all the minterms of the function & inspect each column separately

① If the two minterms in a column are not circled, apply 0 to the corresponding

multiplexer input.

② If the two minterms are circled, apply 1 to the corresponding multiplexer input.

③ If the bottom minterm is circled and the top is not circled, apply 1nV A to the

corresponding mux input.

④ If the top minterm is circled and the bottom is not circled apply 1nV to the

corresponding mux input.

Circle at column iI Input,

iI Circle at column

iI Input,

iI

0

○ A

○ ○

1 ○

A’

Ex. , , 1, 3 , 5 , 6 F f A B C

FY

M U X0I

1I

2I

3I

0

1

A

A '

0S

1S

B C

14

0I 1I 2I 3I

A

A

0 1 2 3

4 5 6 7

Implementation table

Analysis & Design of Combinational Logic 4-14

Logic Design © Dong-Seog Han

Ex. , , , 2 , 6 , 7 , 8 , 9 ,1 3 ,1 4 ,1 5F f D A B C

FY

0I

1I

2I

3I

D

B C

2S

4I

5I

6I

7I

0

1

A

M U X

1S

0S

8 1

4I

0I

1I

2I

3I

0 1 2 3 4 5 6 7

5I

6I

7I

8 9 10 11 12 13 14 15

D

D

(4) Demultiplexer

In p u t

S e le c t

Y

E N

D EM U X

1 2n

0I1I1nI

0D

1D

2 1n

D

1nS

1S

0S

Ex. 14 demultiplexer

D EM U X

41

0S1S

E

0D

1D

2D

3D

Input Output

0

1

1

1

1

X

0

0

1

1

X

0

1

0

1

0S

1D

2D

3D

1SE

0D

Analysis & Design of Combinational Logic 4-15

Logic Design © Dong-Seog Han

4.6 Adders & Subtractors

(1) Binary Adders

① Half Adders

Inputs Outputs

iA

iB

1iC

iS

0

0

1

1

0

1

0

1

0

0

0

1

0

1

1

0

0

1

0

1

1

0 1

2 3

iA

iA

iB

iB

1i i iC A B

0

1

0 1

1

1

0 1

2 3

iA

iA

iB

iB

i i i i i i

S A B A B A B

iA

iB

iS

1iC

② Full Adder

Inputs Outputs

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

iA

iB

iC

1iC

iS

ABC

00

1

0

01 11 10

0 1 23

4 5 67

B

C

A

iS

ABC

00

1

0

01 11 10

0 1 23

4 5 67

B

C

A

1iC

Analysis & Design of Combinational Logic 4-16

Logic Design © Dong-Seog Han

i iA B

iS

1iC

iC

iA

iB

F AiC

1iC

iS

iA

iB

③ Binary Ripple Carry Adder (Power of hierarchy & reuse in design)

4-bit Ripple Carry Adder

F A F A F A F A

2S 1

S0S

3S

0A

1A

2A

3A

3B

2B

1B

0B

0C

4C

Carry propagation: a long circuit delay

2n+2 gate delay for n-bit ripple carry adder (ex-or delay=2)

fast gate or carry look-ahead adder

④ Carry Look-Ahead Adder

iS

1iC

iA

iB

iP

iG

iC

1

i i i

i i i

i i i

i i i i

P A B

G A B

S P C

C G P C

4-bit Adder

L o o k

A h e a d

C a r r y

G e n e r a to r

7 4 L S 1 8 2

P 3

G 3

P 2

G 2

P 1

G 1

P 0

G 0

B 3

A 3

B 2

A 2

B 1

A 1

B 0

A 0

C 0C 0

C 4

C 3

C 1

C 2

C 4

P 3S 3

P 2S 2

P 1S 1

P 0S 0

1 0 0 0

2 1 1 1 1 1 0 0 0

1 1 0 1 0 0

3 2 2 2

2 2 1 1 0 1 0 0

2 2 1 2 1 0 2 1 0 0

4 3 3 3

C G P C

C G P C G P G P C

G P G P P C

C G P C

G P G P G P P C

G P G P P G P P P C

C G P C

Analysis & Design of Combinational Logic 4-17

Logic Design © Dong-Seog Han

(B) Binary Adder-Subtractor

① Signed Binary Addition & Subtraction

0S

0C

0B

0A

F AF AF AF A

( ) : 1

( ) : 0

1A

2A

3A

2B

3B

1B

1S

2S

3S

4C

74238 4-bit Adder

(2) Decimal Arithmetic

Design a BCD adder with 4-bit binary adders and some glue logics.

4 -b it A d d e r

4 4

4

Z 8 Z 4 Z 2 Z 1

C a r r y - InC a r r y -

O u t

(K )

B C D (0 ~ 9 ) B C D (0 ~ 9 )

B C D A d d e r

A d d e n d A u g e n d

In p u t

C a r r y

S 1S 2S 4S 8C a r r y

9

9+

81

1 0 0 1

1 0 0 1

1 0 0 1 0

+ 1(C a r r y - in )

1

1 9 1 0 0 1 1

Binary Sum BCD Sum Deci

mal

K Z8 Z4 Z2 Z1 C S8 S4 S2 S1 0 0 0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0 1 1

0 0 0 0 1 1 1 1 0 0

0 0 1 1 0 0 1 1 0 0

0 1 0 1 0 1 0 1 0 1

0 1 2 3 4 5 6 7 8 9

0 0 0 0 0 0 1 1 1 1

1 1 1 1 1 1 0 0 0 0

0 0 1 1 1 1 0 0 0 0

1 1 0 0 1 1 0 0 1 1

0 1 0 1 0 1 0 1 0 1

10 11 12 13 14 15 16 17 18 19

Analysis & Design of Combinational Logic 4-18

Logic Design © Dong-Seog Han

23

KZ8Z4Z2Z1

Z2

10118 9

262724 25

181916 17

00

01

11

10

K

67

Z8

Z2

141512 13

303128 29

222320 21

0 1 4 5

000 001 011 010 100 101 111 110

Z4

Z1 Z1

C

A B

C a r r y - InK

Z 8 Z 4 Z 2 Z 1

4 -b it B in a r y A d d e r

K

Z 8 Z 4 Z 2 Z 1

4 -b it B in a r y A d d e r

M S B

0

C

0

S 8 S 4 S 2 S 1

4.7 Binary Comparator

A 2-bit magnitude comparator

Inputs Outputs Inputs Outputs

A1 A0 B1 B0 A=

B

A>

B A<B A1 A0 B1 B0 A=

B A>B

A<B

0 0 0 0 1 1

0 1 0 1

1 0 0 0

0 0 0 0

0 1 1 1

1 0 0 0 1 1

0 1 0 1

0 0 1 0

1 1 0 0

0 0 0 1

0 1 0 0 1 1

0 1 0 1

0 1 0 0

1 0 0 0

0 0 1 1

1 1 0 0 1 1

0 1 0 1

0 0 0 1

1 1 1 0

0 0 0 0

1 1 1 0

23

A 0

A 1 A 0B 1 B 0

0 0

1

0 1

0 1

B 0

671

4 5

11 41 51 2 1 3

11 01 18 9

0 0

0 1

1 1

1 0

A 1

B 1

( ) 1 0 1 0

1 0 1 0 1 0 1 0

1 0 1 0

A B A A B B

A A B B A A B B

A A B B

1 1 1 0

23

A 0

A 1 A 0B 1 B 0

0 0 0 1

0 1

B 0

671

4 5

11 41 5

1 11 2 1 3

1 01 11 1

8 9

0 0

0 1

1 1

1 0

A 1

B 1

( ) 1 1 0 1 0

1 0 0

A B A B A B B

A A B

Analysis & Design of Combinational Logic 4-19

Logic Design © Dong-Seog Han

1 1

1 1 1 0

23

A 0

A 1 A 0B 1 B 0

0 0

1

0 1

0 1

B 0

1 1674 5

1 41 51 2 1 3

11 01 18 9

0 0

0 1

1 1

1 0

A 1

B 1

( ) 1 1 1 0 0

0 1 0

A B A B A A B

A B B

4.8 Binary Multiplier

0A

1A

0B

0 0A B

1B

2A

2B

03 BA

12 BA

21 BA

30 BA

3A

3B

2 0A B

1 1A B

0 2A B

13 BA

22 BA

31 BA

1 0A B

0 1A B

23 BA

32 BA 33 BA

0S

1S2S3S4S5S6S

A 0 B 0

S 0

H A

B 0A 1B 1A 0

S 1

F A

S 2

A 2 B 0 A 1 B 1 A 0 B 2

H AH A

F A

F A

S 3

A 3 B 0 A 2 A 1B 1 B 2 A 0 B 3A 3 B 1A 2 B 2 A 1 B 3

F A

F A

H A

S 4

A 3 A 3B 3 B 3B 2 A 2

F A

F A

S 5

F A

S 6S 7

4.9 Tristate Buffers

XX

E n a b le

A AX

E n a b le

X ' XX

E n a b le '

A AX

E n a b le '

X '

Distinctive shape tri-state buffers

Analysis & Design of Combinational Logic 4-20

Logic Design © Dong-Seog Han

XX

E N 1

XX '

E N 1X

E N 1

XX '

E N 1

X

IEEE tri-state buffers

4.10 Combinational Logic Hazards

Hazards

Unwanted switching transitions that may appear at the output of a circuit because

different paths exhibit different propagation delays.

① Static hazard: causes a single transient in a combinational-logic output signal that

should have remained unchanged in response to an input change.

1 10

Static 1-hazard

10 0

Static 0-hazard

1x

2x

3x

y

② Dynamic hazard: the output changes more than once as a result of a single input

variable change.

Ex. Draw the output F if all gates have the same propagation delay of 5ns.

w = 0y

x = 0

F

y

t= 0 5 1 0 1 5 2 0 2 5 3 0 [n s ]

w = 0

y

x = 0

F

y

t= 0 5 1 0 1 5 2 0 2 5 3 0 [n s ]