21 January 2003Paul Dauncey - UK Electronics1 UK Electronics Status and Issues Paul Dauncey Imperial...

-

Upload

aileen-brown -

Category

Documents

-

view

218 -

download

2

Transcript of 21 January 2003Paul Dauncey - UK Electronics1 UK Electronics Status and Issues Paul Dauncey Imperial...

21 January 2003 Paul Dauncey - UK Electronics 1

UK Electronics Status and Issues

Paul Dauncey

Imperial College London

21 January 2003 Paul Dauncey - UK Electronics 2

UK electronics project (finally!) approved in Dec 2002• Full equipment request, but only for ECAL electronics• Full manpower request for engineering effort from Rutherford

Laboratory (RAL)• New engineer (Adam Baird, RAL) has now joined the project• RAL will also do layout and some testing

Budgeted to use all money and effort by the end of Mar 2004

RAL people have experience of CMS tracker• Significant knowledge of design of Front End Driver (FED)

• Readout board for CMS silicon tracker

• Architecture close to proposed CALICE board

Will now use FED as a starting point for CALICE

UK approval

21 January 2003 Paul Dauncey - UK Electronics 3

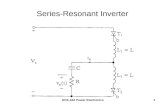

0V

CMS Tracker FED

Front End FPGA

12x Opto Rx

PD

Arr

ay

4x Prog

Delay

1

Synch &Processing

TTCrx

VME

QDR SSRAM2

5V 3.3V 1.5V

DualADC

3.3V

DualADC

1

6

0V

Front End FPGA

12x Opto Rx

PD

Arr

ay

Synch &Processing

8 DualADC

DualADC

43

48

Readout &Synch Control

ASIC

ASIC

ASIC

FPGA

12

1

1

TempSense

TempSense

4x Prog

Delay FPGA

1

3

4x Prog

Delay FPGA

4x Prog

Delay FPGA

22

24

TempSense

3.3V1.5V5V

-5V

spare

PD

Boundary Scan SystemACE

E-FuseHot swap

DC-DC

Back End FPGA

TempSense

12x trim dac

12x trim dac

BufferJumperMatrix

Compact Flash

VME64xInterface

FPGA

Test Connector

SW

SW

Hot swap cycle

Live extract request

ConfigE2PRO

M

Vref

DAQ

TTS

Spare

1.5V

3.3 V5.0 V

2.5V

-5.0V

2.5V

96

85

Vref

1.5V

Run/Halt

VME

Power Good

LE

Ds

extract

IdE2

Prom

FLT

LE

Ds

FSYNC

Readout

+12V

LE

Ds

+5V+3.3V

FE 1

FE 8

EMU

LE

DsProcess

Transfer

+2.5V

LE

Ds

+1.5V-5.0V

halted LE

DsBusy

error

TTC

Over temp

LE

Ds

VME

ClockControl

Data

ClockControl

Data

8 3.3V 1.5V

21 January 2003 Paul Dauncey - UK Electronics 4

Ideally, keep everything to the right, redo everything to the left• Restricts readout board to same I/O and inter-FPGA paths as FED• No major problems seen so far

FED layout

21 January 2003 Paul Dauncey - UK Electronics 5

• FED more complicated and hence expensive than previous design• Keep cost within budget by increasing number of cables per board• Previous design had 6 cables (= 6 VFE-PCBs) per board, new design has 16• Total number of boards for the ECAL drops from 15 to 6• Cost per board should be around £6k ~ 10k

• Save on much of layout and some firmware design• VME FPGA should be very close (if not identical); would like VME

interrupts but not (yet) implemented• Back end (BE) FPGA can reuse major parts of FED firmware• Front end (FE) FPGA will need all new firmware

• BE FPGA much larger than needed• Use spare logic for trigger handling; no need for separate board• Trigger I/O and distribution via J0/J2 backplane unused pins• Requires adding termination resistors for incoming LVDS, i.e. changing

layout of back of board

Implications of using FED

21 January 2003 Paul Dauncey - UK Electronics 6

• Space for cable connectors, line drivers/receivers, ADCs, etc. restricted by position of FE FPGA

• Need to minimise the number of components here

• BE has 21MByte memories for event buffering• With 16 cables, board event size = 166182 = 3.5kBytes/event• 2MBytes stores only around 500 events in each beam burst• May need larger memories for CALICE; i.e. would require changing layout

of back of board

• 9U front panel so can fit 16 high-density 68-pin SCSI connectors• 38 pins needed; leaves 30 pins = 15 differential lines spare• Connected directly to FE FPGA for use as LVDS• Could use as I/O lines for digital HCAL readout

• For more details, see

http://www.hep.ph.ic.ac.uk/calice/electronics/electronics.html

Implications of using FED (cont)

21 January 2003 Paul Dauncey - UK Electronics 7

ECAL assumed electronics schedule

J F M A M J J A S O N D J F M A M J

Prototype 2 boards

Design

Layout

Fabrication and assembly

Testing, including VFE prototype tests

Production 9 boards

Redesign

Layout

Fabrication and assembly

Testing

2003 2004

21 January 2003 Paul Dauncey - UK Electronics 8

• ECAL prototype test schedule• When and where will prototype tests be done?

• ECAL final system schedule• When and where is full readout electronics system needed?• What sets this date and how firm is it?• Will first use be beam, cosmics, calibration tests…?

• HCAL schedule• When will analogue and digital options be ready?• Will either or both options use UK readout?• Is a prototype test needed for the analogue?• When and where will prototype test be done for digital?

Issues – CALICE schedule and plans

21 January 2003 Paul Dauncey - UK Electronics 9

• Voltage levels still have some uncertainties• Main problem would be negatively-shifted LVDS• Needed for schematics – before end February

• Confirm connector choice• Compatibility with cable and connector needed at VFE-PCB• Needed for schematics – before end February

• Pin allocations within connector• In principle, needed for schematics – before end February• If desperate, could wire cables to swap pins later – before end May

• Cable specification• Some cables required for VFE-PCB tests• Need to be manufactured – before end May

• Prototype board testing with “semi-final” VFE-PCB• Needed before redesign – before end November

Issues – VFE-PCB interface

21 January 2003 Paul Dauncey - UK Electronics 10

• Laboratory requirements; cable safety specification, etc.• Needed for cable manufacture – before end May

• Define number of events needed per beam spill• Affects size of onboard memory required• Also needs event size estimate per board from HCAL if using UK boards• Needed for schematics – before end February

• Cable lengths• Distance between VME crate and ECAL/HCAL• Needed for cable manufacture – before end May

• Trigger logic and distribution• Allocation of I/O lines with termination resistors• Needed for assembly– before end May• Number of pins to be allocated on backplane for trigger fanout• Needed for firmware design – before end May

Issues – beam test details

21 January 2003 Paul Dauncey - UK Electronics 11

• Analogue; is VFE-PCB interface compatible?• For signal levels, cables, connectors• Needed for schematics – before end February• Number of boards required for manufacture – before end February 2004

• Digital; interface specification• Sufficient number of spare connector pins?• Needed for schematics – before end February

• Digital; allocations of pins• Have to mount termination resistors on correct lines • Needed for assembly – before end April

• Digital; firmware development for spare pins• UK unlikely to have manpower required• Needed for digital HCAL tests – before end November

Issues – HCAL plans