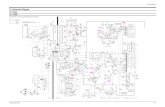

039 Processor Bd Schematic

description

Transcript of 039 Processor Bd Schematic

-

16 ELECTRONIC DIAGRAMS & PARTS: GAME KING PLUS 19 UPRIGHT (821-352-00) - (PRELIMINARY) AUGUST 24, 2001

PROCESSOR BOARD (VIDEO CONTROLLER) SCHEMATIC 757-039-11 REV A PAGE 1 OF 11

4

4

3

3

2

2

1

1

D D

C C

B B

A A

GNDA(ToNETPLEXGround)

CONNECTEDTOU71(5)

+13VDC

NOTES:(UNLESSOTHERWISEINDICATED)

1.ALLRESISTORSEXPRESSEDINOHMS1/4W5%ALLCAPACITORSEXPRESSEDINMICROFARADS

2.ALL14PINICS,PIN14ISPWR,PIN7ISGNDALL16PINICS,PIN16ISPWR,PIN8ISGNDALL20PINICS,PIN20ISPWR,PIN10ISGND

3.JUMPEROPTIONSSHOWNONPAGE2

RESERVEDFORSLOT

RESERVEDFORSLOT

RESERVEDFORMULTIM

EDIA

20PINS

(14.74560MHz)

GND+13VDC+13VDC

+5VDC

28PINS

MEZ2SEL\

N/C--------------------

N/C---------------------DET 1-----------------

DET2------------------GND-------------------CARDCAGEDET

MECH SW----------

SENSTB\------------SENCLK--------------SDATATxA---------SDATARxA--------SDATA ADR--------SDATATxB---------SENGND-------------SENRST\------------GNDB-----------------GNDB-----------------L6-4--------------------V REEL6------------L6-1-------------------DET 6-----------------L6-3-------------------L6-2-------------------+25VDC-------------+25VDC-------------DET 3-----------------V REEL1------------DET 5-----------------V REEL2------------L1-2--------------------V REEL3------------DET 4-----------------V REEL4------------L1-1-------------------V REEL5------------L1-3--------------------L1-4--------------------L2-1--------------------L2-2--------------------L2-3--------------------L2-4--------------------L3-1--------------------L3-2--------------------L3-3--------------------

L5-4--------------------L5-3--------------------L5-2--------------------L5-1--------------------L4-4--------------------L4-3--------------------L4-2--------------------L4-1--------------------L3-4--------------------

NORMALSTRAPPING:1-15,3-13,4-12,5-6&7-8

FROMMULTI-MEDIA

TO MULTI-MEDIA

MULTI-MEDIASTRAPPING:15-16,13-14,11-12,

6-10&8-9

AUSTRALIANSLOT

CONNECTION

LPSTB\---------------

TOMULTI-MEDIA

(VCCGNDPLANE)+5VDC

GNDATOCARDCAGESWITCH

GNDBGNDB

WR0\WR1\

AGND COIL GNDA

BGND COIL GNDB

+25VDC

+13VDC

For Reference

TMS

TDI

TDO

INT1\ISP(OPTIONAL)

+25VDC+25VDC

SCLSDA

FWR1A\

FWR0A\

TCK

RESET\

FORPCBUSEONLY

REV ECO DESCRIPTION BY/DATE CHK/DATEREVISIONS

A

PROTECT GAME KING CTR/TT

757 039 111101NOV99 1NONETDW

C

SCHEMATIC, GAME KING 2

DRAWN DATE DATECHECKED DATEAPPROVED SCALE

SHT __ OF __

DWG. SIZE DWG. NO. REV LTR

TITLE

9295 PROTOTYPE DRIVE RENO, NV 89511INTERNATIONALGAMETECHNOLOGYALL DESIGN, OPERATIVE AND PROCESS DATA PERTAINING TO

THE ARTICLE SHOWN ON THIS SHEET IS THE PROPERTY OFINTERNATIONAL GAME TECHNOLOGY, RENO, NEVADA, THISINFORMATION IS DISCLOSED IN CONFIDENCE AND IS NOT TOBE COPIED, REPRODUCED, REVEALED TO OR APPROPRIATEDBY OTHERS, IN PART OR IN WHOLE, WITHOUT THE EXPRESSCONSENT OF IGT. THIS PRINT IS LOANED AND RECIPIENTCOVENANTS IT WILL NOT BE USED IN ANY MANNERDETRIMENTAL TO THE INTEREST OF IGT, AND MUST BERETURNED ON DEMAND.

75703911

DWG

NO:

EA . PROTOTYPERELEASE TDW/01NOV99 .

EB . USED MAIN 5 VOLTS FORU62 PULLUPS TDW/08NOV99 .

A 5043 PRODUCTIONRELEASE TDW/27DEC99 .

9) Power & Watchdog

PAGE 9

CEOUT

INT2

WCHDOG SEL

VOUTRxDdTxDdRESET SIMM

CARDCAGE DETDROPDOOR DET

MAINDOOR DETBILLVAL DETDOORVAL OUT

RESET CPLD/F/O

INTERROGATE

CCAGE OPENDDOOR OPENMDOOR OPENBVAL OPEN

TT-BACKUP

SRAM BAT LOW

+13VDC

RESET QUART

TT-DET

TT-CNTR1TT-CNTR2

+13VDC LOW

TT-DISABLE

TT BAT LOW

VBATT

RESET I/O

RESET VIDEO

RESET MEZZ

RESET CPU/SEN/AUD

PA RESET

2) CPU

PAGE 2

D[0..15]

RESET CPU/SEN/AUD

IOT SEL

PD[0..7]

INT0

IO RDIO WR

RD

WR1WR0

IA[1..3]

SYS CLK

FAILURE

BBSTB

A25

BLT CLK

QUART CLK

BITBLITZ CLK

INT1

INT3INT2

MM CLKS ALE

PA SEL

BLTRDY

MEZRDY

SENRDY

RESET CPLD/F/O

MEZ1 SEL

BITBLITZ SEL

SLV SEL

EPR SEL

FLH SELRAM SEL

ISP[1..6]

A[1..31]

4) QUARTs & I/O

PAGE 4

IO RDIO WR

QRT2 SELQRT1 SEL

IA[1..3]

RESET I/O

TxDb

A[1..31]

JKPT RST

I/O RESET

INTERROGATE

RxDb

MDOOR OPENDDOOR OPEN

BVAL OPEN

CCAGE OPEN

TT BAT LOWSRAM BAT LOW

LPSW

VERTOUT

RxDd

SCLK256

TxDd

INT0

NETPLEX RxDNETPLEX TxD

FWR EN

RESET QUART

A25

SRESET

TT-CNTR2TT-CNTR1

TT-DET

DCS TxDh

POWER SAVE

INT3

TxDfRxDf

TxDaDIR

DTR

DCD

COMM RxDcCOMM TxDc

COMM RTSCOMM CTS

RxDa

SIN IN

DCS RxDh

PROG RxDgPROG TxDg

TT-DISABLE

QUART CLK

PD[0..7]

OUT5OUT6OUT7

IO2B2IO3B2

OUT SELSOUND SEL

SPEAKERA+SPEAKER-

+13VDC

+25VDC

MM AUDIO1

RESET CPU/SEN/AUD

7) Video BLOCK & VDAC

PAGE 7

PD[0..7]

BD[0..15]

FLATCH2

DOT CLK

RED

FD[0..15]

BLANK1BLANK2

IO RDIO WR

COLOR SEL

RD

IA[1..3]

FLATCH1

BA1

DD[0..7]

FWR0B

SC-1

D[0..15]

PX[0..7]

BLOCKRW

BA0

GREENBLUE

ISP[1..6]

256COLOR

RESET VIDEO

FWR1B

BLOCK

CA0

A[1..31]

VBLK0 SELVBLK1 SEL

6) BitBlitz & VDRAM

PAGE 6

D[0..15]

BBSTB

BLT CLK

BLTRDY

WR0WR1

RDRESET VIDEO

BITBLITZ SEL

H SYNC

V SYNC

BLANK2

+13VDC LOW

FLATCH1FLATCH2

BA1BA0

BLANK1

BLOCKRW

DD[0..7]

BD[0..15]

VERTOUT

DOT CLK

DOT CLK2

SC-1

FD[0..15]

BITBLITZ CLKLPSTB

A[1..31]

256COLOR

ISP[1..6]

BLOCK

CA0

3) Main Memory

PAGE 3

RD

A[1..31]

D[0..15]

RAM SEL

WR0WR1

QRT1 SEL

SENET SEL

WCHDOG SEL

QRT2 SEL

SOUND SEL

CEOUT

IOT SEL

VOUT

COLOR SEL

FWR ENIO WRIO RD

MEZ2 SEL

OUT SEL

EPR SEL

FLH SEL

FWR0B

BOOT SEL

GAME SELVBIT SEL

RESET SIMM

VBATT

FWR1B

FWR0AFWR1A

VBLK1 SELVBLK0 SEL

5) SENET

PAGE 5

A[1..31]

PD[0..7]

SENRDY

IO WRIO RD

SENET SEL

SENCLK

SENRST

SDASCL

FAILURE

SENSTB

SDATA ADRSDATA TxB

SDATA TxA

+13VDC

SDATA RxAOUT7OUT6OUT5IO3B2IO2B2

SYS CLK

RESET CPU/SEN/AUD

SCLK256

TT-BACKUP

MAINDOORDET\BILLVALDET\DOORVALOUTDROPDOORDET\

CARDCAGEDET\

MNHSYNC

DOTCLK2

+13VDCLOW\

USARTTXD

USARTRXD

USARTCLK

MMBLUE

MMHORIZMMGREEN

MMVERT

MNGREEN

HSYNC

MMHORIZ

MMGREEN

VSYNC

MMVERTMMBLUE

VBITSEL\VOUT

MEZ2SEL\

GAMESEL\

BOOTSEL\

VOUTVBITSEL\

VOUT

MNGREEN

VSYNC

HSYNC

USARTCLKUSARTRXDUSARTTXD

BOOTSEL\GAMESEL\

SENRST\

SDATAADR

SCL

SDATATxB

SENSTB\

SDA

SDATATxASDATARxA

SENCLK

SENET SEL\

VBATT

MMCLKSALE

RESETCPLD/F/O

RESET\SIMM

WR1\

BLTRDY\

RAMSEL\

BITBLITZSEL\

BBSTBINT1\

SYSCLK

SENRDY\

IOTSEL\

MEZRDY\

SLVSEL\

RESETMEZZ

PASEL\

PASEL\

WR0\

EPRSEL\

BLTCLK

MEZ1SEL\

FAILURE

FLHSEL\

INT2

BITBLITZ CLK

INT3\

BVAL OPEN\

SRESET\

TT-CNTR1

RESET QUART

TT-DET\

INT0\

TT-DISABLE\

COMMRxDc

COMMCTS

COMMTxDc

SRAM BAT LOW\

INTERROGATE

TT-CNTR2

MM[1..5]

A25\

TxDdRxDd

CCAGE OPEN\

QUARTCLK

MDOOR OPEN\

SININ

TT BAT LOW\

DDOOR OPEN\

SOUND SEL\

PROGRxDg

QRT1 SEL\

DCSRxDh

A24

NETPLEXTxD

TxDb

RESET\ I/O

RxDa

A12

OUT6

SCLK256

LPSW

A5

FWREN\

PROGTxDg

OUT5

MMAUDIO1

A15

A13

A1

OUT7

A26A25

A8

A17

A23

SPEAKERB+

TxDa

A3

MMAUDIO1

IO2B2

QRT2 SEL\

+13VDC

A19

A21

JKPTRST

SPEAKERA+

IO3B3

SPEAKER-

VERTOUT

A6

A4

POWERSAVE

I/ORESET\

DTR

A11

A7

OUT SEL\

A22

A18

A16

TxDf

+25VDC

SPEAKERB+

A14

A2

A9

RxDf

DCSTxDh

A[1..31]

A10

DCD

RxDb

A20

DIR

NETPLEXRxD

COMMRTS

CE\OUT

WCHDOGSEL\

CE\OUT

DD[0..7]

FLATCH2

IA[1..3]

PX4PX5

PX2

D15

PD1

PX3

PX1

IA1

PD5

IORD\

PX7

BLANK2

PD7

PX6

PX0

BLOCKRW\

FWR0B\

FD[0..15]BD[0..15]

PD2

RD\

DOTCLK

SC-1

D12

VGND

BA0

COLORSEL\

RED

D5

D11

IOWR\

BA1

D8

D13

D7

D4

PD3

BLANK1

RED

D[0..15]

D14

D3

IA2

PD6

D6

IA3

DOTCLKPX[0..7]

FLATCH1

PD0

D2

256COLOR\

D10

D0

VGND

PD4

REDVGND

PD[0..7]

D9

RESET\VIDEO

D1

BLANK2

RESET\ CPU/SEN/AUD

BLOCK

CA0

FWR1B\

ISP[1..6]

ISP2

ISP3

ISP1

ISP6

GND

SENGND

MNBLUEMNBLUE

MMRED

MNRED

MNRED

MMRED

HSYNCMNHSYNC

MNVSYNC

MNVSYNCVSYNC

MMVERTMMHORIZ

MMGREEN

MMBLUE

MMRED

FWR0A\FWR1A\

BLUE

BLUEGREEN

GREENGREENBLUE

VBLK0 SEL\

LPSTB\

VBLK1 SEL\

PARESET\

VCCVCC

VCC

B

VCC

A

A

V

AB

AUDIO

R187 751 2R189 751 2

J2

32 PIN DIN

1A1B2A2B3A3B4A4B5A5B6A6B7A7B8A8B9A9B

10A10B11A11B12A12B13A13B14A14B15A15B16A16B

J5

1A1C2A2C3A3C4A4C5A5C6A6C7A7C8A8C9A9C10A10C11A11C12A12C13A13C14A14C15A15C16A16C17A17C18A18C19A19C20A20C21A21C22A22C23A23C24A24C25A25C26A26C27A27C28A

29A29C30A30C31A

32A32C

31C

28C

R188 751 2

J10

1 2 3 4 5 6 7 8 9

J11

10 PIN

12345678910

J1

64 PIN DIN

1A1B2A2B3A3B4A4B5A5B6A6B7A7B8A8B9A9B

10A10B11A11B12A12B13A13B14A14B15A15B16A16B17A17B18A18B19A19B20A20B21A21B22A22B23A23B24A24B25A25B26A26B27A27B28A

29A29B30A30B31A

32A32B

31B

28B

J4

1A1C2A2C3A3C4A4C5A5C6A6C7A7C8A8C9A9C10A10C11A11C12A12C13A13C14A14C15A15C16A16C17A17C18A18C19A19C20A20C21A21C22A22C23A23C24A24C25A25C26A26C27A27C28A

29A29C30A30C31A

32A32C

31C

28C

CR15

1N914

13

X1

HEADER, VIDEO 1

12345678

161514131211109

CR10

1N914

13

CR9

1N914

13

R191

0 OHM3 Amps

1 2

CR14

1N914

13

FID1 FID2

FIDUCIAL

REF X1

16 pin DIP Socket

FID3

E22

CR13

1N914

13

CR8

1N914

13

-

AUGUST 24, 2001 ELECTRONIC DIAGRAMS & PARTS: GAME KING PLUS 19 UPRIGHT (821-352-00) - (PRELIMINARY) 17

PROCESSOR BOARD (VIDEO CONTROLLER) SCHEMATIC 757-039-11 REV A PAGE 2 OF 11

4

4

3

3

2

2

1

1

D D

C C

B B

A A

EPRSEL\FLHSEL\RAMSEL\

SLVSEL\IOSEL\

11.9996MHZ

CPUCLKR10 R9 R19 FREQUENCY------------------------------------0 1 0 32.0087MHz1 1 0 29.4912MHZ0 0 0 24.0143MHz (DEFAULT)

0=OPEN , 1=INSTALLED

R20STRAPPEDDISABLESTHEPLL(TRI-STATESOUTOUTS)

STRAPPINGOPTIONS

(1,6)

(1,3)

fromQUART#2

fromMULTIMEDIA

fromQUART#1

Low+13VDC

(1)

(1)

08000000h10000000h18000000h20000000h28000000h30000000h38000000h

(1)PASEL\

BLTSEL\

MEZZ1SEL\

(1)

AS\

(10)

(1,5)

(1,6)

(1,9)

00000000h

READY\

ALE

MEZ1SEL\

BITBLITZSEL\

DEN\

SLVSEL\

FLHSEL\

BLAST\

IOSEL\

WR

RAMSEL\

BE0\BE1\

EPRSEL\CLK

DT/R\

(1,6,7)

R83,R85,R89,R101andR66ARENOTUSEDATTHISTIME

OPTIONALFORDIFFERENTCPUSPEEDS

U45 U40 U4 U19 U42 U46 U31 U32

U19

TESTINGPURPOSEONLY

(1)

(1,4,5,7,11)

(1,3,4,5,7,11)

(1,4,5,9,11)

(1,3,4,6,7,10)

(1,3,6,7,10)

(1,3,6,10)

(1,3,6,10)

(1,9)

(1,3,4,5,7)

(1,4,7,11)

(1,3,4,5,6,7,10)

(1,6)

(1,6)

(1,6)

(1,5)

(1,5)

(1)

(1,4)

(1,4)

(1,4)

(1,3)(1,3)

(1,4)

J5,2C

J5,4A

J5,3A

(1,3)

J4,15A

(1)J5,4C

757039

11DWG

NO:

A

PROTECT GAME KING CTR/TT

757 039 111101NOV99 2NONETDW

C

SCHEMATIC, GAME KING 2

DRAWN DATE DATECHECKED DATEAPPROVED SCALE

SHT __ OF __

DWG. SIZE DWG. NO. REV LTR

TITLE

9295 PROTOTYPE DRIVE RENO, NV 89511INTERNATIONALGAMETECHNOLOGYALL DESIGN, OPERATIVE AND PROCESS DATA PERTAINING TO

THE ARTICLE SHOWN ON THIS SHEET IS THE PROPERTY OFINTERNATIONAL GAME TECHNOLOGY, RENO, NEVADA, THISINFORMATION IS DISCLOSED IN CONFIDENCE AND IS NOT TOBE COPIED, REPRODUCED, REVEALED TO OR APPROPRIATEDBY OTHERS, IN PART OR IN WHOLE, WITHOUT THE EXPRESSCONSENT OF IGT. THIS PRINT IS LOANED AND RECIPIENTCOVENANTS IT WILL NOT BE USED IN ANY MANNERDETRIMENTAL TO THE INTEREST OF IGT, AND MUST BERETURNED ON DEMAND.

BLT CLK1

3.6864MHZ26.6722MHZ

14.74560MHz

MM CLK1

QUART CLK1

PD2PD1PD0

PD7

PD3

PD6

PD4PD5

IA1

IA3IA2

24.0143MHZ

CPU CLK

ISP1ISP2ISP3ISP4

D15

D14

D11

D7

D6

D4

D2

D1

D13

D5

D5

D6

D11D10

D0

D2

D1

D14

D7

D12

D3

D10

D9

D8

D12

D5D3D4

D13

D6

D0

D3

D9

D8

D15

D1

D7

D0

D4

D2

D5D6

D0

D7

D3D4

D1D2

D15

D11D10

D14

D12

D9

D13

D8

PD2PD1PD0

PD7

PD3

PD6

PD4PD5

CPU CLK1

BITBLITZ CLK1

A8

A31

A30

A23

A18

A13

A11

A2

A1

A10

A4

A6

A6

A11

A28

A25

A16

A31

A17

A20

A19 A14

A28

A27

A22

A4

A3

A21

A5

A22

A26

A21

A29

A23

A1

A12

A7

A10

A2

A28

A27

A14

A13A12

A24

A24

A31A30

A29

A9

A2

A19

A17

A25

A25

A5

A3

A30

A29

A18

A15

A27

A3

A20

A1

A9

A26

A15

A7

A16

A8

VCC

VCC

VCC

VCC VCC

VCC

VSS

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

TP

E4

ETCH

U16 80960SA

41403938373635302928272625242019

1615141312111098543

83828180

17

21

31

33

44

47

53

71

73

6 1

18

22

32

34

43

48

54

63

72

74

77

84

7

57585960

706461

6867494645

7679

66

69525156

55

62

78

D0AD1AD2AD3AD4AD5AD6AD7AD8AD9

AD10AD11AD12AD13AD14AD15

A16A17A18A19A20A21A22A23A24A25A26A27A28A29A30A31

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

INTOINT1INT2/INTRINT3/INTA

LOCKHOLDHLDA

DT/RDENA1A2A3

ASREADY

W/R

BLAST/FAILBE0BE1RESET

CLK2

VCC

ALE

TP

E2

R66 1K1 2

TP

TP

U52

74AC245

23456789

191

1817161514131211

A1A2A3A4A5A6A7A8

GDIR

B1B2B3B4B5B6B7B8

U26

74HC138

123

645

15141312111097

ABC

G1G2AG2B

Y0Y1Y2Y3Y4Y5Y6Y7

U42B

74AC324

56

TP

R59910

12

TP

RP1

10K

12345 6 7 8

E12

RP11

10K

123456789

10

RP7

10K

123456789

10

REF U16

84 pin PLCC Socket (Through Hole)

U32

74AC573

23456789

111

1918171615141312

D1D2D3D4D5D6D7D8

COC

Q1Q2Q3Q4Q5Q6Q7Q8

U4

CY2291

201

4 16192

6

714151718

813101211395

32XIN32XOUT

VDD VDDVBATT

32K

XTALIN

XTALOUTS0S1S2OE

XBUFFFLPCLKCPUCLK

CLKACLKBCLKCCLKDGND

U3B

74HC04

34

E17

U40

74AC573

23456789

111

1918171615141312

D1D2D3D4D5D6D7D8

COC

Q1Q2Q3Q4Q5Q6Q7Q8

R101K

12

RP4

10K

12345678910

U3C

74HC04

56

R3

20

1 2

U3E

74HC04

1110

R26

20

1 2

U3A

74HC04

1 2

C8

0.1uF

12

R6410K

12

R28

20

1 2

C63

0.1uF

12

R201K

12

C34

0.1uF

12

C49

0.1uF

12

R91K

12

C19

0.1uF

12

R83 1K1 2

R93 10K

1 2

C4

0.1uF

12

+C20

22uF

12

R101 1K1 2

R88 10K1 2

C41

0.1uF

12

RP13

10K

123456789

10

R581K

12

R9210K

12

C47

0.1uF

12

RP5

10K

123456789

10

R191K

12

R80 10K1 2

RP8

10K

123456789

10

R71

10K

1 2

U18A

74HC14

1 2

R51 10K

1 2

R18

20

1 2

R94 10K

1 2

R86 10K

1 2

R85 1K1 2

R82 10K

1 2

R2

20

1 2

R99 10K

1 2

Y2

14.7456 MHz

1 2

R65 10K

1 2

TP

U3D

74HC04

98 RP3

10K

12345

R70 1K

1 2

RP6

10K

1 2 3 45678

+ C510uF

12

RP9

10K

123456789

10

U42A

74AC321

23

R89 1K1 2

U29

XC9536, BUSS CONTROLLER

35

19

34

39

18

331

24

44

25

43

26

40

38

27

1328

8

29

42

22

9

5

14

11

2

2036

15

3

16

6

17

12

30

47

37 SALE

IO_EN

FAIL

OPT 1

BE1

IO_RDDEN

SYSCLK

OPT 4

IOTSEL

RAMNW

BBSTB

OPT 2

IO_WR

WR0

ASRESET

BITSEL

RD

EXTRDY

RDY

SLVSEL

OPT 0

BLAST

IOSEL

EPROMSEL

NCWR1

TDI

RAMSEL

TMS

CLK

TCK

ALE

TDO

MEZ1SELWR

BE0

C7

0.1uF

12

R96

100

1 2

TP

R79 1K

1 2

R72

100

1 2

U3F

74HC04

1312

U42C

74AC329

108

D[0..15]

RESET\ CPU/SEN/AUD

IOT SEL\

PD[0..7]

A[1..31]

INT0\

IO RD\IO WR\RD\

WR1\

WR0\

SYS CLK

FAILURE

BBSTBA25\

BLT CLK

QUART CLK

BITBLITZ CLK

INT1\

INT3\

INT2

MM CLK

S ALE

PA SEL\

BLTRDY\

MEZRDY\

SENRDY\

RESET CPLD/F/O

MEZ1 SEL\

BITBLITZ SEL\SLV SEL\

EPR SEL\FLH SEL\RAM SEL\

IA[1..3]

ISP[1..6]

SIMMRDY\

-

18 ELECTRONIC DIAGRAMS & PARTS: GAME KING PLUS 19 UPRIGHT (821-352-00) - (PRELIMINARY) AUGUST 24, 2001

PROCESSOR BOARD (VIDEO CONTROLLER) SCHEMATIC 757-039-11 REV A PAGE 3 OF 11

1

1

2

2

3

3

4

4

D D

C C

B B

A A

SENETSEL\WCHDOGSEL\QRT2SEL\SOUNDSEL\

QRT1 SEL\

COLORSEL\

U21U26U22U11U47 U39

BASE

(1,9)

VBATT

STUFFFORRTC62423(REMOVEFORDALLASRTC)

VOUT

WR0\RD\(1,2)

(1)

(1,5)

(1,4)

(1)

MEZ2SEL\

OUTSEL\

(1,7,10)

(10)SRAMCE\CE\OUT

28000000h28010000h28020000h28030000h

28070000h

28040000h

28060000h28050000h

08000000H08200000H08400000H08600000H

00000000H00200000H

U41

08800000H08A00000H08C00000H08E00000H

FWR1B\

FWR0B\

FWR1A\

FWR0A\

(1,10)

OPTIONALREALTIMECLOCK

(1,2,4,5,7,11)

(1,4,11)

(1,2,6,7,10)

(1,2,4,5,6,7,10)

(1,9,10)

(1,2,6,7,10)

(1,10)

(1,10)

(9,10)

(1,2,6,10)

(1,2,6,10)

(1,9)

(1,9)

(1,2,4,5,7)

(1,4,11)(1,7)

(1,7)(1,7)

(1,4)

(1,4)

(1,2)

(1,2)

(1,2)

(1,7,10)

(1,10)

J5,3C

757039

11DWG

NO.

A

PROTECT GAME KING CTR/TT

757 039 111101NOV99 3NONETDW

C

SCHEMATIC, GAME KING 2

DRAWN DATE DATECHECKED DATEAPPROVED SCALE

SHT __ OF __

DWG. SIZE DWG. NO. REV LTR

TITLE

9295 PROTOTYPE DRIVE RENO, NV 89511INTERNATIONALGAMETECHNOLOGYALL DESIGN, OPERATIVE AND PROCESS DATA PERTAINING TO

THE ARTICLE SHOWN ON THIS SHEET IS THE PROPERTY OFINTERNATIONAL GAME TECHNOLOGY, RENO, NEVADA, THISINFORMATION IS DISCLOSED IN CONFIDENCE AND IS NOT TOBE COPIED, REPRODUCED, REVEALED TO OR APPROPRIATEDBY OTHERS, IN PART OR IN WHOLE, WITHOUT THE EXPRESSCONSENT OF IGT. THIS PRINT IS LOANED AND RECIPIENTCOVENANTS IT WILL NOT BE USED IN ANY MANNERDETRIMENTAL TO THE INTEREST OF IGT, AND MUST BERETURNED ON DEMAND.

_10) Memory Options

PAGE 10

A[1..31]

GAME SEL

RD

FWR0A

FWR1A

RESET SIMM

SRAM CE

VOUT

SRAM WE1

SRAM WE0

SRAM OE

VBIT SEL

FWR0BFWR1B

D[0..15]

WR1WR0

XM4 SELXM3 SELXM2 SELXM1 SELXMB SEL

EPSONRTCSEL\

A7

A10

SRAM WE1\

A1

D15

D9

A21D1

SRAM WE0\

XM4SEL\

A8

A6

A4

A1

A3

D8

A15

A3 D1

A23

A22

A18A17

D0D0

D2

SRAM OE\

XM1SEL\

A5

A12

A2

A14

D6

A16

A4

A11

D12

D3

XM2SEL\

D[0..15]

A22

A17

D4

A18

D7

D2

A16

A21

D0

A2

XM3SEL\

A13

A19

D5

D13

D10

D14

D11

A9

D3

VCC

VCC

VCC

VCC

VSS

VCC

VCC

VCC

VCC

TP

Y3

32.768 MHz

1 2TP

TP

U25A74AC32

1

23

U25B74AC32

4

56

TP

U25C74AC32

9

108

U25D74AC32

12

1311

REF U39

40 pin DIP Socket

R8110K

12

U42D74AC32

12

1311

U20

74HC138

123

645

15141312111097

ABC

G1G2AG2B

Y0Y1Y2Y3Y4Y5Y6Y7

U19A74AC32

1

23

R104 1K1 2

U7

74HC138

123

645

15141312111097

ABC

G1G2AG2B

Y0Y1Y2Y3Y4Y5Y6Y7

TP

TP

U19D74AC32

12

1311

TP

R62

1K12

TP

R31

1K12

R9810K

12

R9710K

12

+C64

22uF

12

R61

0 OHM

1 2

R57 1K1 2

R60

1K

1 2

U21 RTC DS1215S

6

1

2

11123139

4

14

16

7

10

15

D

X1

X2

CEIOEWERST

ROM/RAM

BAT1

BAT2

VCCI

Q

CEO

VCCO

R10010K

12

C48

0.1uF

12

U46

RTC 62423

579

10

42

1311

2024

19161514

1

12

2322

368

171821

A0A1A2A3

ALECS0WRRD

CS1VDD

DOD1D2D3

STD.P

GND

(VDD)(VDD)

GNDGNDGND

GNDGNDGND

U39

256KX16 EPROM120nS

2122232425262728293132333435

1918171615141312109876543

363738

30

220

39

11401

A0A1A2A3A4A5A6A7A8A9A10A11A12A13

D0D1D2D3D4D5D6D7D8D9

D10D11D12D13D14D15

A14A15A16(2M)

GND

CEOE

VPP(A17)

GNDVCCVPP

RP10

10K

1234 5

678

U41B

74HC139

1413

15

1211109

AB

G

Y0Y1Y2Y3

C28

0.1uF

12

R1131K

12

C54

0.1uF

12

C40

0.1uF

12

C31

0.1uF

12

C27

0.1uF

12

C46

0.1uF

12

R30

1K1 2

U41A

74HC139

23

1

4567

AB

G

Y0Y1Y2Y3

RD\

A[1..31]

D[0..15]

QRT1 SEL\SENET SEL\

WCHDOG SEL\QRT2 SEL\

SOUND SEL\

CE\OUT

IOT SEL\

VOUT

COLOR SEL\

IO WR\

IO RD\

MEZ2 SEL\

OUT SEL\

VBLK0 SEL\

EPR SEL\

FWR0B\

BOOT SEL\

GAME SEL\

VBIT SEL\

SRAM CE\

VBATT

WR1\

WR0\

FWR EN\

RAM SEL\

VBLK1 SEL\

RESET\ SIMM

FWR1B\

FWR0A\FWR1A\

FLH SEL\

-

AUGUST 24, 2001 ELECTRONIC DIAGRAMS & PARTS: GAME KING PLUS 19 UPRIGHT (821-352-00) - (PRELIMINARY) 19

PROCESSOR BOARD (VIDEO CONTROLLER) SCHEMATIC 757-039-11 REV A PAGE 4 OF 11

4

4

3

3

2

2

1

1

D D

C C

B B

A A

(1)

(1)

(1,9)

TELLTALE

TxDe

U44 U77 U78U2 U76 U62

IO2A1

RS485

RS232DATACOLLECTION

SENET CYCLE DONE

CHOPPEDACIN(LOWVOLTAGE)

PROGRESSIVECOMMUNICATIONS

RXDD2

ONBOARDF/OCOMMUNICATIONS

#2

#1

JACKPOT RESET DETECT

LIGHTPENSWITCHDETECT

+13VDCRESET\

SILICONSERIALNUMBER

SPAREI/O

SPAREF/O

MICROTOUCH / SPARE

(1,2)

(1,2)

(1,3)

(1,2)

(1,9)

(1,9)

J2,7A

J2,13B

J2,8BJ2,8A

J2,9AJ2,10B

J2,12AJ2,12B

J2,9B

J2,13A

(1,3)

J2,14A

J2,14BJ2,15B

J2,15A

J2,16AJ2,16B

J1,4A

J1,4BJ1,3B

J1,5BJ1,5A

Max. rate = 38.4kb/s

Max. rate = 9.6kb/s

Max. rate = 19.2kb/s

Max. rate = 115.2kb/s

Max. rate = 19.2kb/s

Max. rate = 4800b/s

Max. rate = 19.2kb/s

RESET\

TOLEDs (DS2&DS3)

TOLEDs (DS5,DS6&DS7)

SPARE

(1,3,11)

OUTCLK

(1,11)

(1,11)

(1)

OPTION

U78 U79U60 U20 U30

4504 INPUT OUTPUTMODE LEVEL LEVEL

1 (VCC) TTL CMOS

0 (VSS) CMOS CMOS

OPTIONAL

RESETQUART

(1,2,7,11)

(1,2,5,7,11)

(1,2,3,5,7,11)

(1,2,5,9,11)

(1,3,11)

(1,11)

(1,2,3,5,6,7,10)

(1,9)(1,9)

(1,8,9)

(1,8,9)

(1,9)

(1,8,9)(1,8,9)

(1,8,9)(1,8,9)

(1,8.9)(1,8.9)

(1,8.9)

(1,2,3,5,7)

(1,6)

(1,5)

(1,5)

(1,5)

(1,5)

(1,5)(1,5)

(1,3)

(1,2)

J2,3A

J5,21C

J2,4A

J1,18A,18B

J2,1A,1B

J2,11A

J2,11B

(1) J2,10A

J1,3A

(1)

(1)(1)(1)

(1)(1)

(1)(1)

(1)

(1)(1)

(1)

(1)

(1)(1)

(1)(1)

(1)(1)

(1)

(1)

DATACOLLECTIONSYSTEM(IGT)

757039

11DWG

NO.

A

PROTECT GAME KING CTR/TT

757 039 111101NOV99 4NONETDW

C

SCHEMATIC, GAME KING 2

DRAWN DATE DATECHECKED DATEAPPROVED SCALE

SHT __ OF __

DWG. SIZE DWG. NO. REV LTR

TITLE

9295 PROTOTYPE DRIVE RENO, NV 89511INTERNATIONALGAMETECHNOLOGYALL DESIGN, OPERATIVE AND PROCESS DATA PERTAINING TO

THE ARTICLE SHOWN ON THIS SHEET IS THE PROPERTY OFINTERNATIONAL GAME TECHNOLOGY, RENO, NEVADA, THISINFORMATION IS DISCLOSED IN CONFIDENCE AND IS NOT TOBE COPIED, REPRODUCED, REVEALED TO OR APPROPRIATEDBY OTHERS, IN PART OR IN WHOLE, WITHOUT THE EXPRESSCONSENT OF IGT. THIS PRINT IS LOANED AND RECIPIENTCOVENANTS IT WILL NOT BE USED IN ANY MANNERDETRIMENTAL TO THE INTEREST OF IGT, AND MUST BERETURNED ON DEMAND.

_11) Audio

PAGE 11

SPEAKERA+

SPEAKER-

+13VDC

MM AUDIO1

IO WRSOUND SEL

RESET CPU/SEN/AUD

OUT SEL

+25VDC

OUT CLK

IA1

PD[0..7]

IA1IA2IA3

A4A5A6

IA1IA2IA3A4A5A6

SNOUTSNOUT

RXDA2

TXDA1

RXDA1

IO2A1IO3A1IO3A1

IO0A1

TXDB1TXDB1

RXDB1

TXDC1

RXDC1IO0C1

IO2C1

RXDC2

IO0B1

TXDA2

RXDB2IO0B2

IO2C2

TXDC2TXDB2

TXDD2

SNINSNIN

PD6

PD1

PD7

PD3

PD1PD2PD3PD4

PD0

PD7

PD5

PD0

PD5

PD7

PD6

PD4

PD4

PD6

PD2

PD5

OUT CLK

IA1

VCC

VCC

VCC

VDD

VCC

VCC

VCC

VSS

+13VDC

+13VDC

+13VDCVCC

VCC

VCC +13VDC

+13VDC

VCC

VCC

VCC

VCC

VCC

A

A

A

VCC

+13VDC

VCC

VCC

C112

0.1uF

12

C76

0.1uF

12

Q8

2N3904

2

1

3

R198

2.2K

1 2

C61

0.1uF

12

R87

10K

12

R7810K

12

Q5

2N3904

2

1

3

R56

10K

1 2

U45

SC26C94

181715131211109

192027262524

8723222116

363729303132

444333343539

515049484746

4523

4565

38

42

41

2

2840

114

D0D1D2D3D4D5D6D7

RXDATXDAIO0AIO1AIO2AIO3A

RXDBTXDBIO0BIO1BIO2BIO3B

RXDCTXDCIO0CIO1CIO2CIO3C

RXDDTXDDIO0DIO1DIO2DIO3D

A0A1A2A3A4A5

RDNWRNCENIQRNIACKNDACKNRESET

X1/CLK

X2

VCC

VSSVSS

VSSVSS

R84

10K

12RP22

10K

1 234

RP15

10K

1 2 3 45678

R217

2.4K

1 2

E15

R1962.2K

12

U62A74HC125

23

1

U62B

74HC125

56

4

U80

4504

35791114

13

246

101215

8

116

AIBICIDIEIFI

MODE

AOBOCODOEOFO

VSS

VCVOUT

U87B

ILD2

43

56

R208220

12

R175

470

1 2

C103

0.1uF

12

R185

750

1 2

TP

R181

1K

1 2

CR18

1N914

13

RP2310K

1 2 3 45678

R11 10K1 2

C113

0.1uF

12

RP19

10K

1 2 3 45678

Q7

2N3904

2

1

3

C24

0.1uF

12

RP24 100K

12 3

4

RP20

10K

123 4

J9

1 2

C26

0.1uF1

2

U86A

ILD2

12

87

TP

+C70

22uF

12

TP

U62D

74HC125

12 11

13

S1

TEST SWITCH

1 2

TP

R1181K

12

C101

0.1uF

12

E11

R55 10K1 2

R1681K

12

R69

10K

12

TP

U62C

74HC125

98

10

TP

CR17

1N914

13

TP

U61

DS2401Z

1324

DATAN/C

GNDGND

U19C74AC32

9

108

C124

0.1uF

12

RP25 100K12345

678

R1701K

12

TP

R211

150

1 2

R226220

12

E13 PAD

E14 PAD

U2

74HC175

4

5

12

13

91

237610111514

D1

D2

D3

D4

CLKCLR

Q1Q1Q2Q2Q3Q3Q4Q4

TP

U18C

74HC14

56

TP

U86B

ILD2

43

56

R22510K

12

RP21 100K12345

678

Q4

2N3904

2

1

3

TP

R197220

12

RP18 100K

12 3

4

U31

SC26C94

181715131211109

192027262524

8723222116

363729303132

444333343539

515049484746

4523

4565

38

42

41

2

2840

114

D0D1D2D3D4D5D6D7

RXDATXDAIO0AIO1AIO2AIO3A

RXDBTXDBIO0BIO1BIO2BIO3B

RXDCTXDCIO0CIO1CIO2CIO3C

RXDDTXDDIO0DIO1DIO2DIO3D

A0A1A2A3A4A5

RDNWRNCENIQRNIACKNDACKNRESET

X1/CLK

X2

VCC

VSSVSS

VSSVSS

U77

4504

3579

1114

13

246101215

8

116

AIBICIDIEIFI

MODE

AOBOCODOEOFO

VSS

VCVOUT

R200

220

1 2

TP

R117

4.7K

1 2

TP

R212

220

1 2

E1 PAD

U18D

74HC14

9 8

R199

220

12

U81

4504

35791114

13

246

101215

8

116

AIBICIDIEIFI

MODE

AOBOCODOEOFO

VSS

VCVOUT

R631K

12

U87A

ILD2

12

87

C1260.1uF

12

U76

4504

3579

1114

13

246101215

8

116

AIBICIDIEIFI

MODE

AOBOCODOEOFO

VSS

VCVOUT

CR12

1N914

13

C53

0.1uF

12

RP12

10K

1234

5

6789

10

C6

0.1uF

12

C105

0.1uF

12

IO RD\

IO WR\

QRT2 SEL\

QRT1 SEL\

IA[1..3]

RESET\ I/O

TxDb

A[1..31]

I/O RESET\

INTERROGATE

RxDb

MDOOR OPEN\DDOOR OPEN\BVAL OPEN\CCAGE OPEN\

TT BAT LOW\SRAM BAT LOW\

LPSW

VERTOUT

SCLK256

INT0\

FWR EN\

RESET QUART

A25\

SRESET\

TT-CNTR2TT-CNTR1

TT-DET\

DCS TxDh

POWER SAVE

INT3\

TxDfRxDf

TxDa

DIRDCD

COMM TxDc

COMM RTS

SIN IN

DCS RxDh

PROG RxDgPROG TxDg

TT-DISABLE\

QUART CLK

PD[0..7]

OUT5

OUT6

OUT7

IO2B2IO3B2

OUT SEL\

SOUND SEL\

SPEAKERA+

SPEAKER-

+13VDC

+25VDC

MM AUDIO1

NETPLEX TxD

RESET\ CPU/SEN/AUD

RxDdTxDd

DTR

COMM CTSCOMM RxDc

NETPLEX RxD

RxDa

JKPT RST

-

20 ELECTRONIC DIAGRAMS & PARTS: GAME KING PLUS 19 UPRIGHT (821-352-00) - (PRELIMINARY) AUGUST 24, 2001

PROCESSOR BOARD (VIDEO CONTROLLER) SCHEMATIC 757-039-11 REV A PAGE 5 OF 11

4

4

3

3

2

2

1

1

D D

C C

B B

A A

CH1SDOCH2SDOMASDOSCLKSTBIO_EN

U83

U68

U6

RP9

SENGRD - (J1-13A)

J2,1A/1B

(FAILUREDETECTED)

(FIRMWAREDEFINEABLEbyQUART)

(FIRMWAREDEFINEABLEbyQUART)

(FIRMWAREDEFINEABLE)

(FIRMWAREDEFINEABLE)

CPUFALURE

OUT5

OUT6

OUT7

(1,2)

(1,3)

(1,2,5)

J1,2A

J1,2B

(1)

J1,11A

J1,12B

J1,12AJ1,10BJ1,10AJ1,13B

(1,2)

DON'TSTUFF

U3

I 2C

LED configiration (FRONTPANELVIEW)

DSx DSx DSx DSx DSx DSx

PCBside

FAIL

OUT7

OUT6

OUT5

IO3B

2

IO2B

2

(FIRMWAREDEFINEABLE)

OPTIONAL

(1,2,4,7,11)

(1,2,3,4,7,11)

(1,2,4,9,11)

(1,2,3,4,6,7,10)

(1,2,3,4,7)

(1,4)

(1,4)

(1,4)

(1,4)

(1,4)

(1,4)

(1)

(1)

(1)(1)

(1)(1)

J1,11B

(1)

(1)

(1)

757039

11DWG

NO.

A

PROTECT GAME KING CTR/TT

757 039 111101NOV99 5NONETDW

C

SCHEMATIC, GAME KING 2

DRAWN DATE DATECHECKED DATEAPPROVED SCALE

SHT __ OF __

DWG. SIZE DWG. NO. REV LTR

TITLE

9295 PROTOTYPE DRIVE RENO, NV 89511INTERNATIONALGAMETECHNOLOGYALL DESIGN, OPERATIVE AND PROCESS DATA PERTAINING TO

THE ARTICLE SHOWN ON THIS SHEET IS THE PROPERTY OFINTERNATIONAL GAME TECHNOLOGY, RENO, NEVADA, THISINFORMATION IS DISCLOSED IN CONFIDENCE AND IS NOT TOBE COPIED, REPRODUCED, REVEALED TO OR APPROPRIATEDBY OTHERS, IN PART OR IN WHOLE, WITHOUT THE EXPRESSCONSENT OF IGT. THIS PRINT IS LOANED AND RECIPIENTCOVENANTS IT WILL NOT BE USED IN ANY MANNERDETRIMENTAL TO THE INTEREST OF IGT, AND MUST BERETURNED ON DEMAND.

A1A2A3A4A5A6A7A8A9A10

PD0

PD1

PD2

PD5

PD4

PD3

PD7

PD6

VCC

VCC

+13VDC

VCC

VCC

VCC

VCC

+13VDC

VCC

VCC

TP

R24 10K1 2

TP

R8 10K1 2

TP

R5 10K1 2

RP16

4.7K

1 2 3 4

5

6 7 8 9

10

R169 201 2

R23 10K1 2

TP

R192 201 2

TP

TP

C9

0.1uF

12

TP

U5E

74HC14

11 10

C117

0.1uF

12

TP

C125

0.1uF

12

TP

U18F

74HC14

1312

C21

0.1uF

12

U5A

74HC14

1 2

C12

.01uF

12

CR16

1N914

13

CR11

1N914

13

R193150

12

U78

4504

3579

1114

13

246101215

8

116

AIBICIDIEIFI

MODE

AOBOCODOEOFO

VSS

VCVOUT

C109

0.1uF

12

RP2

1K

1234

5

6789

10

U18E

74HC14

11 10

U5C

74HC14

5 6

C104

0.1uF

12

SENETEEG68PLCC

SENET II

U10

39

4647

68

5

2021

38

8 69 61

62

63

64

65

66

67

2625

35

10111213141516171819

27

28

29

30

31

32

33

34

40

1

42

43

41

34

36

5051

7

222324

37

4849

605958575655545352

2

4445

VCC

VCCVCC

VCC

VCC

VCCVCC

VCC

GND

GND(selramhi)

GND

CABSDI

CABSTBOUT

CABSTBIN

SEL0

SEL1

SEL2

SEL3

GNDGND

GND

A1A2A3A4A5A6A7A8A9A10

D0

D1

D2

D3

D4

D5

D6

D7

SENRDY

RESET

IO-W

RIO

-RD

SENSEL

SCLK17

SCLK256(rd7)

GND

GNDGND

GND(w

rtramhi)

GND (scanen)GND (scantn)NC (scanout)

(oenramhi)GND (rd2) NC

(rd3) NC

CH1SDOCH1SDI

CH2SDO(ntr) MASDO(rd6) SCLKO

(rd4) STB(rd5) IO_EN

SDASCL

SYSCLK

(rd0) NC(rd1) NC

+C25

22uF

12

U5D

74HC14

9 8

R25 10K1 2

U85

M34R32

12

34

56

7

8

NCNC

WCRVSS

SDASCL

MODE/WC

VCC

U5F

74HC14

13 12

R178

10K

1 2

R17 1K1 2

R5410K

12

R7 1K1 2

TP

DS6

Red

21

DS4

Yellow

21

DS1

Yellow

21

RP17 22

1234 5

678

DS2

Yellow

21

TP

R206

100

1 2

C58

0.1uF

12

DS3

Yellow

21

R205

100

1 2

DS5

Yellow

21

U74

74C240

468

11131517

119

181614129753

2010

2

1A21A31A42A12A22A32A4

1G2G

1Y11Y21Y31Y42Y12Y22Y32Y4

VDDVSS

1A1

R194

10K

12

R17910K

12

U5B

74HC14

3 4

R17710K

12

R17410K

12

R15010K

12

E9

R16010K

12

R6 1K1 2

R14910K

12

R16 1K1 2

A[1..31]

PD[0..7]

SENRDY\

IO WR\

IO RD\

SENET SEL\

SENCLK

SENRST\

SDA

SCL

FAILURE

SENSTB\

SDATA ADR

SDATA TxB

SDATA TxA

+13VDC

SDATA RxA

OUT7

OUT6

OUT5

IO3B2

IO2B2

SYS CLK

RESET\ CPU/SEN/AUD

SCLK256

-

AUGUST 24, 2001 ELECTRONIC DIAGRAMS & PARTS: GAME KING PLUS 19 UPRIGHT (821-352-00) - (PRELIMINARY) 21

PROCESSOR BOARD (VIDEO CONTROLLER) SCHEMATIC 757-039-11 REV A PAGE 6 OF 11

4

4

3

3

2

2

1

1

D D

C C

B B

A A

(1,2)

(1,4)

OPTIONAL

(1,2)

(1)

SC-1

(1)

SC-3

SC-1

FORENGINEERINGTESTING

STUFF IFPLLNOTUSED

SC-2

U13 U55 U12 U7 U14 U28 U50

note:BD12,BD13,BD14andBD15areNOTUSEDor connected

NORMALLYNOTSTUFFED

(1,7)

FORPCBUSEONLY

(1,2,3,7,10)

(1,2,3,4,5,7,10)

(1,2,3,7,10)

(1,2,3,10)

(1,2,3,10)

(1,7,9)

(1,8,9)

(1,7)

(1,7)

(1,7)

(1,7)

(1,7)

(1,7)

(1,7)(1,7)

(1,7)

(1,7)

(1,7)

(1,7)

(1,7)

(1,2)

(1,2)

(1,2)

(1)

(1)

(1,2,7)

757039

11DWG

NO.

A

PROTECT GAME KING CTR/TT

757 039 111101NOV99 6NONETDW

C

SCHEMATIC, GAME KING 2

DRAWN DATE DATECHECKED DATEAPPROVED SCALE

SHT __ OF __

DWG. SIZE DWG. NO. REV LTR

TITLE

9295 PROTOTYPE DRIVE RENO, NV 89511INTERNATIONALGAMETECHNOLOGYALL DESIGN, OPERATIVE AND PROCESS DATA PERTAINING TO

THE ARTICLE SHOWN ON THIS SHEET IS THE PROPERTY OFINTERNATIONAL GAME TECHNOLOGY, RENO, NEVADA, THISINFORMATION IS DISCLOSED IN CONFIDENCE AND IS NOT TOBE COPIED, REPRODUCED, REVEALED TO OR APPROPRIATEDBY OTHERS, IN PART OR IN WHOLE, WITHOUT THE EXPRESSCONSENT OF IGT. THIS PRINT IS LOANED AND RECIPIENTCOVENANTS IT WILL NOT BE USED IN ANY MANNERDETRIMENTAL TO THE INTEREST OF IGT, AND MUST BERETURNED ON DEMAND.

CCLK

DONE

SC-3

FD1FD2FD3FD4FD5FD6FD7FD8FD9FD10FD11FD12FD13FD14FD15

FD0

FD0FD1FD2FD3FD4FD5FD6FD7

FD8FD9FD10FD11FD12FD13FD14FD15

BD0BD1BD2BD3BD4BD5BD6BD7

BD11BD12BD13BD14BD15

BD8BD9BD10

A7

A12

A8

A11

A21

A6

A16

A20

A3

A15

A5

A1

A18A17

A9

A13

A2

A14

A4

A10

SC-2

DIN

ISP5

ISP2ISP3

ISP4

DD0

DD2

DD4

DD6

DD3

DD1

DD7

DD5

D11

D4

VA1

D10

VS2

VA8

D0

VA0

VA4

VS8D3

VS7

VS5

D10

VS10

D12

D2

D11

D8

D0

VA2

VA4

VS4

VA1

BBDOTCLK

VS5

VA1D13

VA5

D8D7

VS[0..15]

VS4

VA7

D4

VS14VS15

VS13

VS8

VS6

D7D6

VA5

D0

VA2

D1

VS1

VA6

D15

VA8

D15

D12

VS2

D3

VA6

VA3

VS0

VS9

VS6

VS12

D10D11

VS11

VA0

D6

D8

D5

D2

VS10

D4

D2

VA3

VS13

VS15

VS0VA4

VA7

D9

D3

D5

VS14

VS9

D13

D1

D14

D7

VA6

D5

VA2

VA[0..8]

VS7

D14

D9

VS1

VA7

D6

VS3

VS12

D1

VA8

VA0

VA5

VA3

VS3

D9

VS11

BD15BD14BD13BD12

VCC

VCC

VCC

VCC

VCC

VSS

VCC VCC

VCC

V

R1271K

12

TP

R4

10K1 2

E7

JUMPER

U59A74HC32

1

23

R2710K

12

TP

R21920

12

R47

0 OHM1 2

TP

R102 10K

1 2

E3

R67 10K

1 2

R29

10K

12

R49

10K

1 2

R1081K

12

R42

220

1 2

Y1

26.667MHz

14 8

7 1

VCC OUT

GND EN

REF U9

84 pin PLCC Socket (SMT) U11

256X16 VDRAM60nS

373635343130292827

26

39

63

64 571012

46911

2

38

41

32

33

151720224345485053555860

141619214446

8

495154565961

3 13

23

42

52

62

1 18

47

57

2425

40

A0A1A2A3A4A5A6A7A8

RAS

CAS

SE

SC I/O 00I/O 01I/O 02I/O 03

SI/O 00SI/O 01SI/O 02SI/O 03

DT/OE

QSF

DSF

VCC

VSS

I/O 04I/O 05I/O 06I/O 07I/O 08I/O 09I/O 10I/O 11I/O 12I/O 13I/O 14I/O 15

SI/O 04SI/O 05SI/O 06SI/O 07SI/O 08SI/O 09

VCC

SI/O 10SI/O 11SI/O 12SI/O 13SI/O 14SI/O 15

VSS

VSS

VSS

VSS

VSS

VSS

VCC

VCC

VCC

VCC

WBL/WELWBU/WEU

NC

CR7

1N914

13

TP

U59C74HC32

9

108

CR4

1N914

13

U8

XC9536, DD CONTROLLER

34 15

38

29

16

37

17

36

30

33

39

35

28

1

6

2

18

78

3

195

91112

4

20

1314

22

40

24

42

25

4443

2627

SC1 TDI

C256

NC

TMS

NC

TCK

NC

TDO

NC

CA0

NC

BLOCK

VS12

VS0

VS13

DD0

VS1VS2

VS14

DD1DCLK

VS3VS4VS5

VS15

DD2

VS6VS7

DD3

VS8

DD4

VS9

DD5

VS11VS10

DD6DD7

TP

R14

0 OHM1 2

R1

10K

12

E5

R3210K

12

TP

R3310K

12

+ C2

22uF

12

R3710K

12

R4110K

12

U1

256X16 VDRAM60nS

373635343130292827

26

39

63

64 571012

46911

2

38

41

32

33

151720224345485053555860

141619214446

8

495154565961

3 13

23

42

52

62

1 18

47

57

2425

40

A0A1A2A3A4A5A6A7A8

RAS

CAS

SE

SC I/O 00I/O 01I/O 02I/O 03

SI/O 00SI/O 01SI/O 02SI/O 03

DT/OE

QSF

DSF

VCC

VSS

I/O 04I/O 05I/O 06I/O 07I/O 08I/O 09I/O 10I/O 11I/O 12I/O 13I/O 14I/O 15

SI/O 04SI/O 05SI/O 06SI/O 07SI/O 08SI/O 09

VCC

SI/O 10SI/O 11SI/O 12SI/O 13SI/O 14SI/O 15

VSS

VSS

VSS

VSS

VSS

VSS

VCC

VCC

VCC

VCC

WBL/WELWBU/WEU

NC

C13

0.1uF

12

CR5

1N914

13

C35

0.1uF

12

R48

10K

12

U17

XC1765D

12

34

76

DATACLK

RESET/OECE

VPPCEO

C56

0.1uF

12

C3

0.1uF

12

C36

0.1uF

12

C23

0.1uF

12

FID4

E8

C74

0.1uF

12

FID5

FIDUCIAL

U18B

74HC14

34

C14

0.1uF

12

R218

0 OHM

1 2

C1

0.1uF

12

U9 XC3142, BitBlitz

43

22

64

1

444641454042484950515253

2421276166167114732523282620191817153934

5410

79

83

54

131175

87

828132

7876

8084

6

77

626359606567686970

123132

557472

3029475856363857

37

9

33

35

GND

VCC

VCC

GND

D0D1D2D3D4D5D6D7D8D9D10D11

A1A2A3A4A5A6A7A8A9A10A11A12A13A14A15A16A17A18BLANK2A20

RESETADRSTB

DSF-2

RD

WR0WR1

BITCLKBLTSELLPSTB

SC-1SC-2

OE-1OE-2WE-1WE-2

CAS-1CAS-2

DSF-1WE-3

SC-3

RAS

VA0VA1VA2VA3VA4VA5VA6VA7VA8

PWRDNM0M1

DONECCLK

DIN/256COLOR

FLATCH1FLATCH2

BA0BA1

BLOCKRWDOTCLK

HORZVERT

OSC

BLTRDY

BLANK

A21

TP

R221

10K

1 2

R15

0 OHM

1 2

U27

74HC574

23456789

111

1918171615141312

D1D2D3D4D5D6D7D8

CLKOC

Q1Q2Q3Q4Q5Q6Q7Q8

U48

74HC574

23456789

111

1918171615141312

D1D2D3D4D5D6D7D8

CLKOC

Q1Q2Q3Q4Q5Q6Q7Q8

CR6

1N914

13

E6

R534.7K

12

D[0..15]

BBSTB

BLT CLK

BLTRDY\

WR0\

WR1\

RD\

RESET\ VIDEO

BITBLITZ SEL\

H SYNC

V SYNC

BLANK2

FLATCH1

FLATCH2

BA1

BA0

BLANK1

BLOCKRW\

DD[0..7]

BD[0..15]

VERTOUT

DOT CLK2

FD[0..15]

BITBLITZ CLK

LPSTB\

A[1..31]

SC-1

ISP[1..6]

BLOCKCA0

+13VDC LOW\

DOT CLK

-

22 ELECTRONIC DIAGRAMS & PARTS: GAME KING PLUS 19 UPRIGHT (821-352-00) - (PRELIMINARY) AUGUST 24, 2001

PROCESSOR BOARD (VIDEO CONTROLLER) SCHEMATIC 757-039-11 REV A PAGE 7 OF 11

4

4

3

3

2

2

1

1

D D

C C

B B

A A

SCO

SC0

FLATCH2

FLATCH2

FLATCH2

FLATCH2

(1,3)

(1,2,3,4,5)

(1,2,4,11)

BLANK1FLATCH1

ENBLK1

BLOCKLOOKUP

(1,6)

(1,6)

(1,6)

ENBLK2

(1)

ENBLK2

COLOR SEL\IO RD\

IOWR\VDACW\

VDAC R\

OPTIONALIF PLCC PART NOT AVAILABLE

256COLOR\

256 EN\

PLCA1PLCA2PLCA3

PLCA4

PLCA0

SC1

BA0BA1

BLOCKRW\

FWR1B\

ENBLK1256 EN\

RESET\

(1,6)

RD\SC-1

(1,2,6)

(1,6)

BLOCK

(1,6)

FLATCH2FLATCH1

SC0

(1,3)

VBLK1SE

L\

FLATCH1

GNDGNDVBLK0 SEL\

FWR0B\

FLATCH2

FLATCH2

VBLK0SE

L\

256C GND

(1,2,4,5,11)

(1,2,3,4,5,11)

(1,2,3,6,10)

(1,2,3,4,5,6,10)

(1,2,3,6,10)

(1,3,10)

(1,3,10)

(1,6,9)

(1,6)(1,6)

(1,3)

(1,6)

(1,6)

(1,6)

(1,6)

(1,6)

(1,6)

J1,24BJ1,25BJ1,24A

757039

11DWG

NO.

A

PROTECT GAME KING CTR/TT

757 039 111101NOV99 7NONETDW

C

SCHEMATIC, GAME KING 2

DRAWN DATE DATECHECKED DATEAPPROVED SCALE

SHT __ OF __

DWG. SIZE DWG. NO. REV LTR

TITLE

9295 PROTOTYPE DRIVE RENO, NV 89511INTERNATIONALGAMETECHNOLOGYALL DESIGN, OPERATIVE AND PROCESS DATA PERTAINING TO

THE ARTICLE SHOWN ON THIS SHEET IS THE PROPERTY OFINTERNATIONAL GAME TECHNOLOGY, RENO, NEVADA, THISINFORMATION IS DISCLOSED IN CONFIDENCE AND IS NOT TOBE COPIED, REPRODUCED, REVEALED TO OR APPROPRIATEDBY OTHERS, IN PART OR IN WHOLE, WITHOUT THE EXPRESSCONSENT OF IGT. THIS PRINT IS LOANED AND RECIPIENTCOVENANTS IT WILL NOT BE USED IN ANY MANNERDETRIMENTAL TO THE INTEREST OF IGT, AND MUST BERETURNED ON DEMAND.

D0D1D2D3D4D5D6D7

D8D9D10D11D12D13D14D15

BD0BD1BD2BD3BD4BD5BD6BD7

BD8BD9BD10BD11FD0FD1FD2FD3

FD4FD5FD6FD7FD8FD9FD10FD11

BA21

CA4

CA4

CA0CA1

CA2

CA[0..4]

CA3

CA3

CA1

CA2

BA2

BA18

BA14

BA13

BA6

BA23

BA17

BA3

BA15

BA16

BA10

BA8BA7

BA5

BA9

BA16

BA3

BA10

BA8

BA15BA14

BA6

BA6 BA9

BA16

BA5

BA3

BA12

BA12

BA4

BA18

BA18

BA14

BA13

BA19

BA16

BA7

BA11

BA13

BA7

BA5

BA4

BA24

BA19

BA7

BA17

BA9

BA19

BA15

BA12BA11

BA2

BA8

BA13

BA19

BA3

BA11

BA6

BA25

BA22

BA10

BA17

BA11

BA4

BA10

BA8

BA17

BA18

BA[2..24]

BA20

BA9

BA5

BA15

BA12

BA4

BA14

BA2

A3A2A1

BA2

BL15

BL5

BL0

BL6

BL11

BL2BL3

BL0

BL7

BL8

BL4

BL15

BL10

BL4

BL15

BL2

BL14 BL14

BL4

BL12

BL9

BL13

BL[0..15]

BL8

BL3

BL13

BL1

BL9

BL6

BL10BL11

BL7

BL5

BL12

BL1

DD5

DD1

DD7DD6

DD4

DD0

DD3DD2

ISP5ISP2ISP3ISP6

ISP3

BL12

BL5

BL13

BL6BL7

BL14

BLKRW\+VBLK1

BK7

BK12

BK15

BK10

BK8

BK3

BK5

BK2

BK9

BK8

BK0

BK9

BK15

BK14

BK13

BK9

BK10

BK7

BK1

BK4

BK4

BK2

BK11

BK7

BK5

BK10

BK8

BK8

BK11BK12

BK1

BK1

BK6

BK6

BK0

BK2

BK11

BK13

BK0

BK11

BK14

BK4

BK6

BK6

BK12

BK1

BK14

BK14

BK4

BK3

BK13

BK0

BK5

BK2

BK10

BK13

BK3

BK12

BK[0..15]

BK7

BK5

BK9

BK15

BK15

BK3

BL0BL1BL2BL3

BL4BL5BL6BL7BL8

BL10

BL12BL14BL15

BL9

BL11

BL13

PX5

PX4

PX7

PD4

PD3

PD1

PX6

PD0

PX0

IA2

PX7

PD6

PX5

PX3

IA1

PD7

PX0

PX7

PX0

PX2

PD7

PX3

PX4

IA1

PD5

PX2

PX2

PX3

PX6

PX4

PX0

PD1

PX3PX3

PX4

PX2PX1

PX6

PX1

PX1

PD0

PX5

VIDEO VCC

PD3

PD6

IA2

PD2

PD4

PX2

PD5

PX0

PX7

PD2

PX6

PX1PX1

PX5

BA20

VCC

VCC

VCC

VSS

VCC

V V

V

V

V

V

VCC

BA

TP

U53

512KX8 EPROM100nS

12111098765

272623254

282932

1314151718192021

2422

30

1

31

A0A1A2A3A4A5A6A7A8A9A10A11A12A13A14A15A16(1M)

D0D1D2D3D4D5D6D7

OECE

A17(2M)

VPP(A19)

PRG(A18)

R105 10K

1 2

U44A74HC08

1

23

R90 10K

1 2

R123

10K

12

R68 10K

1 2

U73

VDAC (DIP)

56789

101112

1718192021222324

123

26272515

16

13

14

4

28

P0P1P2P3P4P5P6P7

DQ0DQ1DQ2DQ3DQ4DQ5DQ6DQ7

REDGREENBLUE

RS0RS1WR

BLANK

PCLK

VSS

IREF

VCC

C119

0.1uF

12

TP

R176

0 OHM

1 2

R190

0 OHM3 Amps

12

C120

0.1uF

1 2

TP

U33

74HC574

23456789

111

1918171615141312

D1D2D3D4D5D6D7D8

CLKOC

Q1Q2Q3Q4Q5Q6Q7Q8

TP

U47

74HC574

23456789

111

1918171615141312

D1D2D3D4D5D6D7D8

CLKOC

Q1Q2Q3Q4Q5Q6Q7Q8

C82

0.1uF

12

U44B74HC084

56

U57

74HC574

23456789

111

1918171615141312

D1D2D3D4D5D6D7D8

CLKOC

Q1Q2Q3Q4Q5Q6Q7Q8

REF U30

32 pin DIP Socket

REF U53

32 pin DIP Socket

U28

74HC574

23456789

111

1918171615141312

D1D2D3D4D5D6D7D8

CLKOC

Q1Q2Q3Q4Q5Q6Q7Q8

R186

0 OHM3 Amps

12

U24

XC9536, PIXEL CONTROLLER

3837363534333911

24

15

2526

16

27

1730

29

13

2

8

1

3

12

43

9

28

14

187

40

44

4

22

6

19

42

20

5

PX6PX5PX4PX3PX2PX1PX0C256

COLORSEL

TDI

IO_RDVDAC_WR

TMS

IO_WR

TCKTDO

PX7

F1

DD0

CA1

CA4

BLOCK

ENBLK2

BLANK1

CA2

DD7

CA3

DD4DD3

B256

SC1

DD2

VDAC_RD

SCO

DD5

DD1

DD6

ENBLK1

R147150

12

R173

10K

12

C45

0.1uF

12

U82

VDAC (PLCC)

89

101112131415

3233343536373839

1718166

7

4 20

21

22

23

2 3 5 19

24

41

42

43

44

1

27

2526

28

31

30

29

40

D0D1D2D3D4D5D6D7

P0P1P2P3P4P5P6P7

RS0RS1WRRD

BLANK

VCC

VCC

VCC

VCC

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

N/C

BLUE

REDGREEN

IREF

VREF

OPA

COMP

PCLK

C52

0.1uF

12

C123

0.1uF

12

U43

74HC574

23456789

111

1918171615141312

D1D2D3D4D5D6D7D8

CLKOC

Q1Q2Q3Q4Q5Q6Q7Q8

C43

0.1uF

12

C57

0.1uF

12

C73

0.1uF

12

C55

0.1uF

12

+ C5122uF

12

C127

10pF50V

12

C44

0.1uF

12

C30

0.1uF

12

C33

0.1uF

12

C29

0.1uF

12

C71

0.1uF

12

U59D74HC3212

1311

R148

151%

1 2

C42

0.1uF

12

C72

0.1uF

12

C50

0.1uF

12

C32

0.1uF

12

U23

74HC245

23456789

191

1817161514131211

A1A2A3A4A5A6A7A8

GDIR

B1B2B3B4B5B6B7B8

+

-

Q3

LM3342

13

R74

10K

12

CR3

1N914

13

R10310K

12

U22

74HC245

23456789

191

1817161514131211

A1A2A3A4A5A6A7A8

GDIR

B1B2B3B4B5B6B7B8

U44D74HC0812

1311R91

10K

12

R46

10K

1 2

TP

J3

72 Pin SIMM

1 23 45 67 89 10

11 1213 1415 1617 1819 2021 2223 2425 2627 2829 3031 3233 3435 3637 3839 4041 4243 4445 4647 4849 5051 5253 5455 5657 5859 6061 6263 6465 6667 6869 7071 72

L1

FERRITE BEAD

1 2

REF U73

28 pin DIP Socket

U58

74HC257

2

3

5

6

11

10

14

13

151

4

7

9

12

1A

1B

2A

2B

3A

3B

4A

4B

GA/B

1Y

2Y

3Y

4Y

U49

74HC257

2

3

5

6

11

10

14

13

151

4

7

9

12

1A

1B

2A

2B

3A

3B

4A

4B

GA/B

1Y

2Y

3Y

4Y

R7710K

12

R7310K

12

R11510K

12

R11410K

12

E20

+ C8110uF

12

U30

512KX8 EPROM100nS

12111098765

272623254

282932

1314151718192021

2422

30

1

31

A0A1A2A3A4A5A6A7A8A9A10A11A12A13A14A15A16(1M)

D0D1D2D3D4D5D6D7

OECE

A17(2M)

VPP(A19)

PRG(A18)

R9510K

12

U44C74HC089

108

R76 10K

1 2

C114

1.0uF

12

E10

R75

1K1 2

U34

74HC257

2

3

5

6

11

10

14

13

151

4

7

9

12

1A

1B

2A

2B

3A

3B

4A

4B

GA/B

1Y

2Y

3Y

4YU59B

74HC324

56

U35

74AC174

346

111314

91

257101215

D1D2D3D4D5D6

CLKCLR

Q1Q2Q3Q4Q5Q6

C108

0.1uF

12

PD[0..7]

BD[0..15]

FLATCH2

DOT CLK

FD[0..15]

BLANK1

BLANK2

IO RD\IO WR\

COLOR SEL\

BA1

SC-1

D[0..15]

PX[0..7]

IA[1..3]

A[1..31]

RD\

BA0

RESET\ VIDEO

BLOCKRW\

DD[0..7]

ISP[1..6]

CA0

BLOCK

FLATCH1

VBLK1 SEL\

FWR0B\

FWR1B\

VBLK0 SEL\

REDGREENBLUE

-

AUGUST 24, 2001 ELECTRONIC DIAGRAMS & PARTS: GAME KING PLUS 19 UPRIGHT (821-352-00) - (PRELIMINARY) 23

PROCESSOR BOARD (VIDEO CONTROLLER) SCHEMATIC 757-039-11 REV A PAGE 8 OF 11

4

4

3

3

2

2

1

1

D D

C C

B B

A A

(9)

(1,9)

CC-OPEN

MD-OPEN

STUFFR154FORCARDCAGEALARM (DEFAULT)

STUFFR153FORMAINDOORALARM

U37

U41U36 U92 U60 U25 U61 U50 U35

(1,4,9)

(1,4,9)

(1,9)

(1,9)

(1,9)

(1,9)

(1,6,9)

(1,4,9)

(1,4,9)

(1,4,9)

(1,4,9)

(1,4,9)

(1,4,9)

(1,4,9)

757039

11DWG

NO.

A

PROTECT GAME KING CTR/TT

757 039 111101NOV99 8NONETDW

C

SCHEMATIC, GAME KING 2

DRAWN DATE DATECHECKED DATEAPPROVED SCALE

SHT __ OF __

DWG. SIZE DWG. NO. REV LTR

TITLE

9295 PROTOTYPE DRIVE RENO, NV 89511INTERNATIONALGAMETECHNOLOGYALL DESIGN, OPERATIVE AND PROCESS DATA PERTAINING TO

THE ARTICLE SHOWN ON THIS SHEET IS THE PROPERTY OFINTERNATIONAL GAME TECHNOLOGY, RENO, NEVADA, THISINFORMATION IS DISCLOSED IN CONFIDENCE AND IS NOT TOBE COPIED, REPRODUCED, REVEALED TO OR APPROPRIATEDBY OTHERS, IN PART OR IN WHOLE, WITHOUT THE EXPRESSCONSENT OF IGT. THIS PRINT IS LOANED AND RECIPIENTCOVENANTS IT WILL NOT BE USED IN ANY MANNERDETRIMENTAL TO THE INTEREST OF IGT, AND MUST BERETURNED ON DEMAND.

MD-OPENMD-OPEN

CC-OPEN

VDD

VDD

VDD

VDD

VDD

VSS

TP

C116

0.1uF

12

TP

R18310K

12

C98

0.1uF

12

U71

40175

4

5

12

13

91

237610111514

D0

D1

D2

D3

CLKCLR

Q0Q0Q1Q1Q2Q2Q3Q3

C99

0.1uF

12

TP

C100

0.1uF

12

U75D

4081

12

1311

R184

100K

1 2

TP

U67B

4556

1413

15

1211109

AB

E

Q0Q1Q2Q3

U75C

4081

8

910

R1611K

12

U68

4536

9101112

67

15143

4

5

13

12

ABCD

8_BYCINH

MONOOINHIN1

O1

O2

DO

SR

R155

200K

12

R107470K

12

U67A

4556

23

1

4567

AB

E

Q0Q1Q2Q3

RP14

470K

1 2 3 45678

R137

390K

1 2

U65

4503

246

101214

115

35791113

I1I2I3I4I5I6

DADB

O1O2O3O4O5O6

U70

4076

14131211

910712

15

3456

D0D1D2D3

DDADDBCLKODAODBRST

Q0Q1Q2Q3

C102

1000pF

12

R171

1K

12

U83A

4001

1

23

U83B

4001

5

64

R157

10K

12

U83C

4001

8

910

U66C

4071

8

910

U66D

4071

12

1311

C92

1000pF

12

R158

10K

12

U66B

4071

5

64

R203470K

12

U83D

4001

12

1311

R210470K

12

R1361K

12

R209

100K

1 2

R213470K

12

U75B

4081

5

64

R1561K

12

R1591K

12

R202

100K

1 2

R204470K

12

R1451K

12

R154

0 OHM

1 2

+ C6210uF

12

R153

0 OHM

1 2

U75A

4081

1

23

R133 1K

1 2

U66A

4071

1

23

R125 1K

1 2

R152 1K

1 2

Q6MOSFET N1

32C86

0.1uF

12

R201

100K

1 2

C87

0.1uF

12

R14247K

12

R214

100K

1 2

R182

100

1 2

C91

0.1uF

12

C78

0.1uF

12

CARDCAGE DET\

DROPDOOR DET\

MAINDOOR DET\

BILLVAL DET\

+13VDC LOW\

TT-BACKUP

DOORVAL OUT

INTERROGATE

DDOOR OPEN\

MDOOR OPEN\

BVAL OPEN\

TT-DISABLE\

TT-CNTR1

TT-CNTR2

TT-DET\

CCAGE OPEN\

-

24 ELECTRONIC DIAGRAMS & PARTS: GAME KING PLUS 19 UPRIGHT (821-352-00) - (PRELIMINARY) AUGUST 24, 2001

PROCESSOR BOARD (VIDEO CONTROLLER) SCHEMATIC 757-039-11 REV A PAGE 9 OF 11

4

4

3

3

2

2

1

1

D D

C C

B B

A A

1N6373

OPTIONAL

OPTIONALCOMPONENTSTOBEUSEDONLYWHENBT1 ISNOT INSTALLED.

(1,3)

OPTIONAL

(1,4,8)

(1,6,8)

(1,2)

(1,2)

U22 U69

(1,4,8)

J2,1A/1B

(1,4)

FOREXTERNALPOWERSUPPLY

REMOVEE27WHENUSINGANEXTERNALPOWERSUPPLY

(1,3)

(1,3)

(1,4)

(1)

(1)

(1,2,4,5,11)

(1,3,10)

(3,10)

(1,4)

(1,8)

(1,4,8)

(1,8)

(1,8)

(1,8)

(1,8)

(1,8)

(1,4)

(1,4)

(1,4)

(1,6,7)

(1,4,8)

(1,4,8)

(1,4,8)

(1,4,8)

(1,4,8)

(1,4,8)

(1)

OPTIONAL

757039

11DWG

NO.

A

PROTECT GAME KING CTR/TT

757 039 111101NOV99 9NONETDW

C

SCHEMATIC, GAME KING 2

DRAWN DATE DATECHECKED DATEAPPROVED SCALE

SHT __ OF __

DWG. SIZE DWG. NO. REV LTR

TITLE

9295 PROTOTYPE DRIVE RENO, NV 89511INTERNATIONALGAMETECHNOLOGYALL DESIGN, OPERATIVE AND PROCESS DATA PERTAINING TO

THE ARTICLE SHOWN ON THIS SHEET IS THE PROPERTY OFINTERNATIONAL GAME TECHNOLOGY, RENO, NEVADA, THISINFORMATION IS DISCLOSED IN CONFIDENCE AND IS NOT TOBE COPIED, REPRODUCED, REVEALED TO OR APPROPRIATEDBY OTHERS, IN PART OR IN WHOLE, WITHOUT THE EXPRESSCONSENT OF IGT. THIS PRINT IS LOANED AND RECIPIENTCOVENANTS IT WILL NOT BE USED IN ANY MANNERDETRIMENTAL TO THE INTEREST OF IGT, AND MUST BERETURNED ON DEMAND.

8) TellTale

PAGE 8

CARDCAGE DET

DROPDOOR DET

MAINDOOR DET

BILLVAL DET

+13VDC LOW

TT-BACKUP

DOORVAL OUT

INTERROGATE

DDOOR OPEN

MDOOR OPEN

BVAL OPEN

TT-DISABLE

TT-CNTR1

TT-CNTR2

TT-DET

CCAGE OPEN

VCC OUT1

VCC OUT2

VCC

VDD

VCC

VCC

VCC

VCC

VCC

VSS

VCC

+13VDC

+13VDC

VCC

VCC

VCC

VCC

VCC

VCC

A

R120

10K

1 2

TP

U69

ICS1722N

12345687

10111213141516

9

CHGDCHGPFNMMNCMNSEL0SEL1VSS

RCAUX0AUX1OPRF

VINN/CVDD

MRN

R13810K

12

TP

C122

.01uF

12

U56C

40106

5 6

R126

430

1 2

TP

R45

22M

1 2

U56F

40106

13 12

U64C

40106

5 6

TP

CR2

1N914

1 3

TP

R22

100

1 2

R122

510

1 2

C10

1000pF

12

U56A

40106

1 2

TP

TP

R39

1M1%

1 2

R163

15K

12

R381M1%

12

U56D

40106

9 8

TP

TP

R215

0 OHM3 Amps

12

C18

0.1uF

12

+ C93

100uF25V

12

U72

LM317

1234 5

678VIN

VOUTVOUTADJ NC

VOUTVOUT

NC

TP

R52

100K1%

1 2

TP

TP

D3

1N6373

21

REF U84B2 CLIP

R143

39

1 2

R11610K

12

R431M1%

12

TP

R1396.04K1%

12

L2

100uH

12

C88

47pF

12

TP

U56E

40106

11 10

U64A

40106

12

+

FO1

HFBR-2522

1

2

3

4

R1720 OHM3 Amps

12

TP

TP

Q22N3904

2

1

3

TP

R36

100K1%

1 2

R21 51

.25W

12

U63

Supervisory (691)

7

5

2

12

6

15

16

14

10

4

8

11

9

13

1

3

OSC IN

BATT/N

VOUT

CE OUT

LOW LN

RESET

RESET

WDO

PFO

GND

OSC SL

WDI

PFI

CE IN

VBATT

VCC

BT2

3.6VNiCad

12

C11

.01uF

12

R121

1M1%

1 2

FO2

HFBR-1522

1

2

R34

1K

1 2

U12

ICL7665

1

2

3

4 5

6

7

8OUT1

HYS1

SET1

GND HYS2

SET2

OUT2

V+

U84

LM2576T-5.0

3

4

2

1

5

GND

FDB

OUT

+VIN

OFF

U64B

40106

34

C22

0.1uF

12

C80

0.1uF

12

R3510K

12

R12

3.3K

1 2

C79

0.1uF

12

E21

12

R112

39

12

U64D

40106

9 8

CR1

1N5818

21

R141

330K

1 2

BT1

3.0VLithium

12

C77

0.1uF

12

C106

100pF

12

C68

0.1uF

12

REF U84A

HEAT SINK

U6

75453

24

3

576

1

R14047K

12

+ C107

1000uF25V

12

REF U84B1HEAT SINK

U64E

40106

11 10R119

0 OHM

1 2

R111

330K

12

U56B

40106

3 4

D1

Schottky

13

R110

680K

12

Q12N3904

2

1

3

D2

Schottky

1 3

R1091K

12

C118

.01uF

12

R1310K

12

R44

22M

1 2

R1341K

12

R146

51K12

REF U84B3 HEATSINK COUMPOUND

D4

1N5823

21

R4010K

12

CE\OUT

INT2

WCHDOG SEL\

VOUT

RxDdTxDd

RESET\ CPU/SEN/AUD

CARDCAGE DET\

DROPDOOR DET\

MAINDOOR DET\

BILLVAL DET\

DOORVAL OUT

RESET CPLD/F/O

INTERROGATE

CCAGE OPEN\

DDOOR OPEN\

MDOOR OPEN\

BVAL OPEN\

TT-BACKUP

SRAM BAT LOW\

+13VDC

RESET QUART

TT-DET\

TT-CNTR1

TT-CNTR2

+13VDC LOW\

TT-DISABLE\

TT BAT LOW\

VBATT

RESET\ SIMM

RESET\ I/O

RESET\ VIDEO

RESET MEZZ

PA RESET\

-

AUGUST 24, 2001 ELECTRONIC DIAGRAMS & PARTS: GAME KING PLUS 19 UPRIGHT (821-352-00) - (PRELIMINARY) 25

PROCESSOR BOARD (VIDEO CONTROLLER) SCHEMATIC 757-039-11 REV A PAGE 10 OF 11

4

4

3

3

2

2

1

1

D D

C C

B B

A A

RD\

FWR1A\

RD\ RD\

RESET\RESET\

SRAM

WE1\

SRAM OE\ SRAM OE\SRAM OE\

(1,2,3,6,7)

(1,2,3,6,7)

(3)

(1,3)

XMB SEL\

GND GND GND GND GND GND

(3)

SRAM WE1\FWR1B\

FWR1A\

FWR1B\SRAM WE1\

FWR1A\

VBIT SEL\SRAM CE\GAME SEL\

VOUT VOUTVOUT

(1,2,3,6)

WR0\WR1\ WR1\

WR0\WR1\WR0\

SRAM CE\VBIT SEL\

SRAM CE\VBIT SEL\

GAME SEL\ GAME SEL\SRAM WE0\FWR0B\

FWR0A\SRAM WE0\FWR0B\

FWR0A\ FWR0A\SRAM WE0\FWR0B\

XMB SEL\ XMB SEL\

FWR1B\

XM1 SEL\XM2 SEL\

XM3 SEL\

XM4 SEL\ XM4 SEL\

XM1 SEL\XM2 SEL\

XM3 SEL\ XM3 SEL\

XM1 SEL\XM2 SEL\

XM4 SEL\

VOUT

A18

(2)

SIMMRDY\SIMMRDY\SIMMRDY\

GAME BIT

VOUT

SRAM

A18

(1,2,3,4,5,6,7)

(3)(1,3,9)

(3)(3)

(1,3)

(3)(3)(3)

(1,3)

(1,3)

(3,9)

(1,3,7)(1,3,7)

(3)

(1,2,3,6)

757039

11DWG

NO.

A

PROTECT GAME KING CTR/TT

757 039 111101NOV99 10NONETDW

C

SCHEMATIC, GAME KING 2

DRAWN DATE DATECHECKED DATEAPPROVED SCALE

SHT __ OF __

DWG. SIZE DWG. NO. REV LTR

TITLE

9295 PROTOTYPE DRIVE RENO, NV 89511INTERNATIONALGAMETECHNOLOGYALL DESIGN, OPERATIVE AND PROCESS DATA PERTAINING TO

THE ARTICLE SHOWN ON THIS SHEET IS THE PROPERTY OFINTERNATIONAL GAME TECHNOLOGY, RENO, NEVADA, THISINFORMATION IS DISCLOSED IN CONFIDENCE AND IS NOT TOBE COPIED, REPRODUCED, REVEALED TO OR APPROPRIATEDBY OTHERS, IN PART OR IN WHOLE, WITHOUT THE EXPRESSCONSENT OF IGT. THIS PRINT IS LOANED AND RECIPIENTCOVENANTS IT WILL NOT BE USED IN ANY MANNERDETRIMENTAL TO THE INTEREST OF IGT, AND MUST BERETURNED ON DEMAND.

D11

D5

A28A28

A24A23

A20A20

A18

A13

A12

A5

D3

A1

A7

A10

D14

D12

D12

A3

D0

D13

D2

D11

A12

A7

D4

D2

D5

D2

D7

A16A16A17

A13

A10A9 A9

A27

A2

A16

A3

A17

A17

D11

D5

A12

A7

D6

A20 A20

A18

A14

A14

A14

A2

D10

A17A17

D15

A30

A6

A4

D2

A20

A13

A1

D6

A11

A6

A15

A16

A3

A9

A9

A6

D2

D8

A7

D0

A7

A3

A9

A11

D12

A29

A3A4

D6

A26

D8

A15

D11

A13

A10

A7

A16

A5

A17

A7

D1

A27

D4

A3

D10

D7

D0

D15

A6

A4A4

D3

A18

A13

D4

D0

A12A11

A21

A16

D9

D8

A8 A8

D11

A7

A5

D1

D3D2

A18

A8

A2

A4

A14

A10

D1A14

D4A16

A31

A30

A6

D9

D6

A23

A10

A12

D1

A27

A19

A2

A22

A11

A11

D7

A17

D15

A6

D13

D9

A8

A15

A15

D5

A10